(54) РАЗРЯД ДВОИЧНО-ДЕСЯТИЧНОГО СУММАТОРА

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1982 |

|

SU1229757A1 |

| Устройство для деления десятичных чисел | 1976 |

|

SU744562A1 |

| Сумматор-вычитатель | 1981 |

|

SU993254A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для умножения десятич-НыХ чиСЕл | 1979 |

|

SU817704A1 |

| Последовательный двоично-десятичный сумматор-вычитатель | 1978 |

|

SU734685A1 |

| Множительное устройство | 1979 |

|

SU832554A1 |

| Устройство для умножения десятичных чисел | 1984 |

|

SU1182514A1 |

| Преобразователь двоичного кодаВ дЕСяТичНый | 1979 |

|

SU830371A1 |

| Устройство для суммирования двоично-десятичных чисел | 1980 |

|

SU1001087A1 |

1

Изобретение относится к области вычислительной техники и может быть использовано в двоично-десятичных сумматорах - вычитателях накапливающего типа.

Известен разряд двоично-десятичного сумматора, работающего в прямом коде и позволяющего прибавлять к числу, содержащемуся в сумматоре, положительное число. Известная схема разряда двоично-десятичного сумматора состоит из двоичного сумматора, узла переноса и преобразователя кода. Информационные входы разряда двоично-десятичного сумматора соединены с соответствующими входами двоичного сумматора, входы «Управление и «Перенос разряда двоично-десятичного сумматора - соответственно с управляющим входом и входом переноса двоичного сумматора, а вход переноса двоичного сумматора - с первым входом узла переноса, выход которого связан с выходом «Перенос разряда двоичнодесятичного сумматора и первой группой корректирующих входов двоичного сумматора. Выходы разрядов двоичного сумматора подключены к первой группе одноименных ннформационных входов преобразователя кода, информационные выходы которого соединены с соответствующими выходами разряда двоично-десятичного сумматора, а выход переноса двоичного сумматора - к второму входу узла переноса.

Цель изобретения - расширение функциональных возможностей схемы разряда двоично-десятичного сумматора путем введения операции вычитания без преобразования кодов на регистрах ЦВМ.

Это достигается тем, что в разряд двоичнодесятичного сумматора введен узел переключения выходов двоичного сумматора, информационные входы которого соединены с соответствующими выходами разрядов двоичного сумматора, а его управляющий вход - с входом «Сложение-Вычитание разряда двоично-десятичного сумматора, причем выходы разрядов узла переключения выходов двоичного сумматора подключены к соответствующим разрядам второй группы входов преобразователя кода, второй группы корректирующих входов двоичного сумматора и к группе корректирующих входов узла переноса.

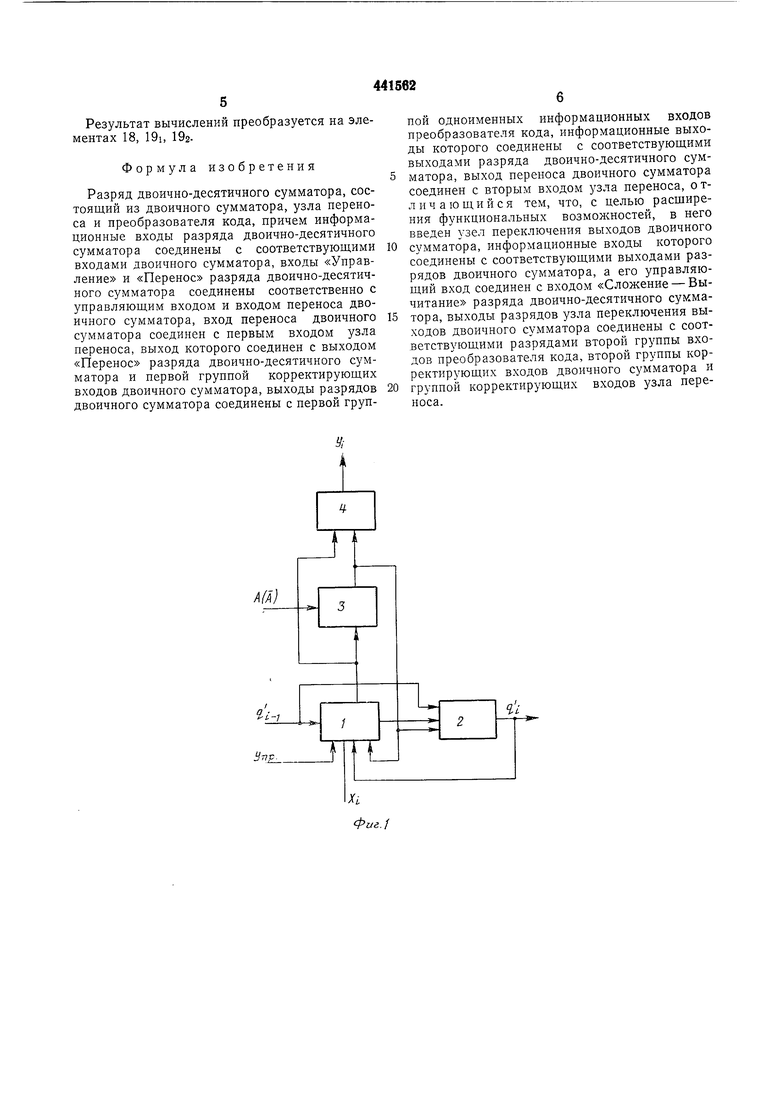

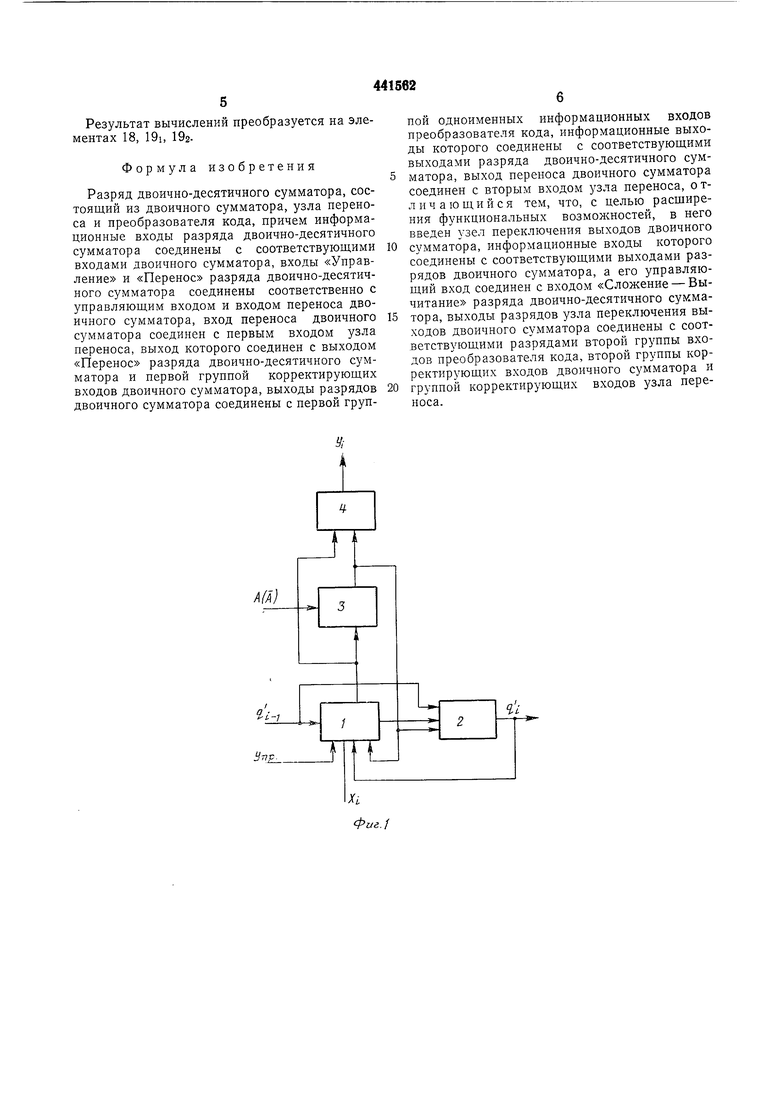

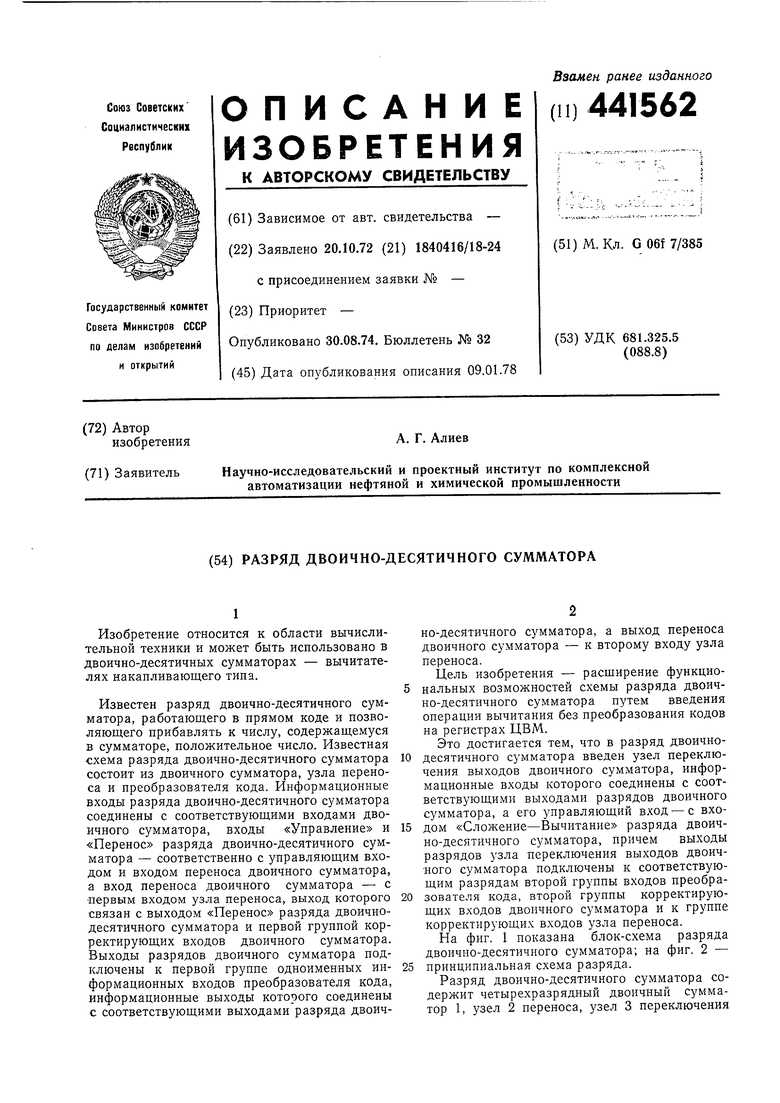

На фиг. 1 показана блок-схема разряда двоично-десятичного сумматора; на фиг. 2 - принципиальная схема разряда.

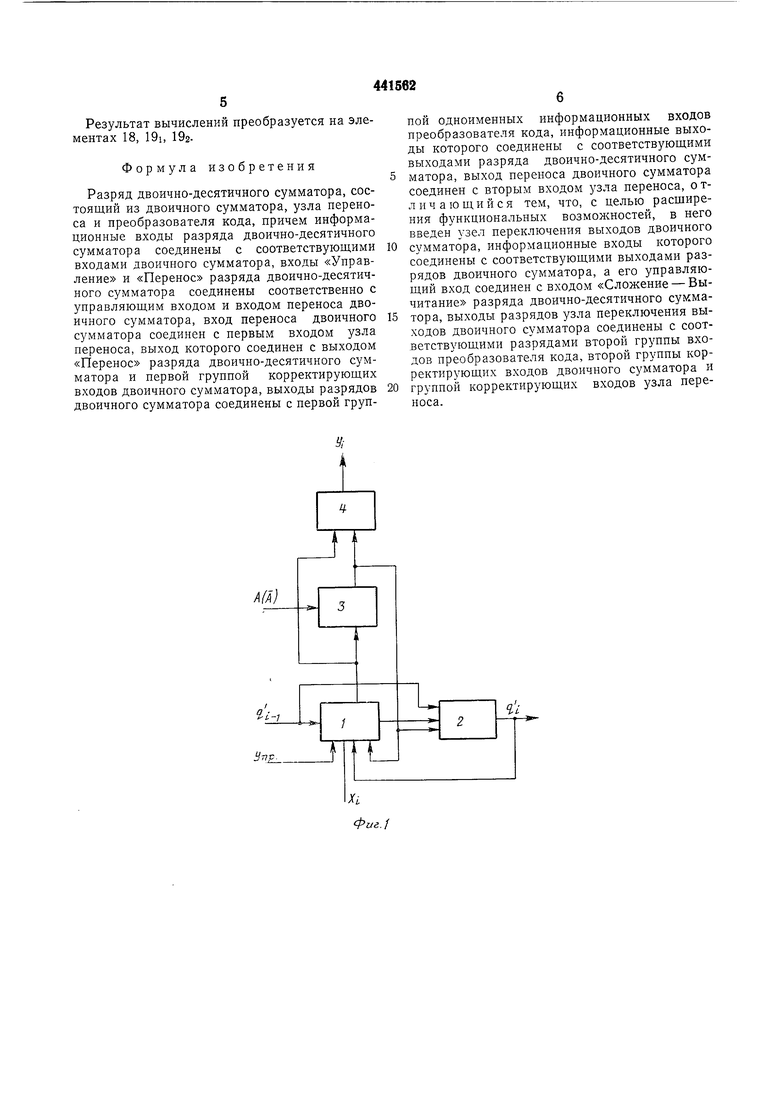

Разряд двоично-десятичного сумматора содержит четырехразрядный двоичный сумматор 1, узел 2 переноса, узел 3 переключения выходов двоичного сумматора и преобразователь 4 кода. Работает разряд следующим образом. Шипы i-ro разряда входного кода числа Хг поступают на двоичный сумматор 1, кроме того, на двоичный сумматор подаются шины переноса от предыдущего и данного разрядов - qi-i и qi, а также выходы узла 3 (переключателя выходов триггеров). Сумматор 1 и узел 3 выдают необходимые сигпалы на узел 2 переноса. К узлу 2 также поступают шипы переноса от предыдущего разряда . С выхода узла переноса берется выходная щина, qi - перенос г-го разряда. Шины выходного кода сумматора 1 подаются па узел 3, па зшравляющие входы которого проходит сигнал А. На вход преобразователя 4 кода поступают необходимые сигналы от сумматора 1 и ззла 3. Шины Уг г-го разряда выходного кода (реззльтаты вычисления) берутся с выхода преобразователя кода. В исходном состоянии в четырехразрядном двоичном сумматоре 1 содержатся цифры Zi, соответствующие значению Pi i-то разряда обратного кода числа Р. Цифра Zi в сумматоре может представляться в коде 8-4-2-1 или в сдвинутом относительно него коде (например, «плюс 6). Zi Pc + С,(1) где Pi - цифра г-го разряда обратного кода числа Р; С -величина сдвига кода сумматора относительно кода 8-4-2-I (С ). В дальнейшем под Zi понимается представлением цифры Pi в коде сумматора. Код цифры Zi поступает на узел 3 инверсии кода, управляемого по входу Л-признаком ХзнНа выходе узла 3 получается четырехразрядный двоичный код числа 3 0 Х,„ 1. На схему подаются сигналы управления, по которым в сумматоре 1 происходит сложение цифр, подаваемых на его входы, - , Xi, qi-i, Qgi (по признакам qi-i и qi в сумматор добавляются соответственно цифры 1 и 6). При сумматор 1 работает в обычном порядке. Если , код сумматора, подаваемый по цепям обратной связи на его вход, с помощью узла 3 инвертируется. Это приводит к тому, что результат сложения оказывается записанным в сумматоре в инверсном коде. Поэтому можно написать, что результат сложения О Vl 1 + + + 1 l5 lZ i+Xi+ql i+6qi,, зн-1 цифра Vi в коде сумматора соответствует цифре Уг i-ro разряда обратного кода суммы У, т. е. с. По окончании как сложения, так и вычитания, в предлагаемом сумматоре оказываются записанпым:и в коде сумматора значения разрядов обратного кода суммы (разности). При выдаче числа сигнал А подается кодом -в случае операции «Сложение и кодом -когда операция «Вычитание. Таким образом, в десятичном разряде на вход преобразователя кода подаются коды цифр Vi Yi + C и 15(У; + С) Значения Vi и У, как фзнкции Уг и УЗП имеют вид 9-7,+С & + В преобразователе выполняется обратное преобразование(vi, У)-, следовательно, на выходную шину У разряда поступает прямой код числа У. Сложность преобразователя существенно зависит от значения С. В случае и он является наиболее простым. На фиг. 2 показан пример электрической принципиальной схемы одного разряда двоично-десятичного сумматора, построенной на микросхемах серии К172. Пунктирными линиями выделены блоки, соответствующие фиг. 1. На элементах 5i-lOi происходит процесс суммирования, а именно на элементах 5i и 52 осуществляется прием входного числа Xi и сигналов переносов по шинам qi-i и qi разрешенными соответственно тактами TI и TzНа элементах 7, 1ч, 8i, 82 формируется сквозной перенос между двоичными разрядами, а на элементах 9ь §2, lOi образуется двоичная сумма кодов. На элементе 11 происходят прием п запоминание результата сквозного переноса. На элементах 12-15 обеспечивается прием; и запоминание результатов двоичного суммирования двух кодов - входного числа г и числа Р, содержащегося в двоичном сумматоре. Число Р может быть положительным или отрицательным и является результатом предыдущих операций. На элементах 102, 16i, 162, 1 осуществляется переключение выходов двоичных триггеров при операциях «Сложение и «Вычитание.

Результат вычислений преобразуется на элементах 18, 19ь 192.

Формула изобретения

Разряд двоично-десятичного сумматора, состоящий из двоичного сумматора, узла нереноса и преобразователя кода, причем информационные входы разряда двоично-десятичного сумматора соединены с соответствующими входами двоичного сумматора, входы «Управление и «Перенос разряда двоично-десятичного сумматора соединены соответственно с управляющим входом и входом переноса двоичного сумматора, вход переноса двоичного сумматора соединен с первым входом узла переноса, выход которого соединен с выходом «Перенос разряда двоично-десятичного сумматора и первой группой корректирующих входов двоичного сумматора, выходы разрядов двоичного сумматора соединены с первой групВпЕ

пой одноименных информационных входов преобразователя кода, информационные выходы которого соединены с соответствующими выходами разряда двоично-десятичного сумматора, выход переноса двоичного сумматора соединен с вторым входом узла переноса, отличающийся тем, что, с целью расширения функциональных возможностей, в него введен узел переключения выходов двоичного сумматора, информационные входы которого соединены с соответствующими выходами разрядов двоичного сумматора, а его управляющий вход соединен с входом «Сложение - Вычитание разряда двоично-десятичного сумматора, выходы разрядов узла переключения выходов двоичного сумматора соединены с соответствующими разрядами второй группы входов преобразователя кода, второй группы корректирующих входов двоичного сумматора и группой корректирующих входов узла переноса.

-4lJ

L-i i h

zo-t г

I

1

.; 1iTO

ff

ft

Тг Т, ii

cmJBbH C/ фиг Z

Yi-r

Ю,

ГС

13 Г--1 6.

i U

w

ihF;

W, /5г

:fl7

75я

7,

П

г /

A /Г

Авторы

Даты

1974-08-30—Публикация

1972-10-20—Подача