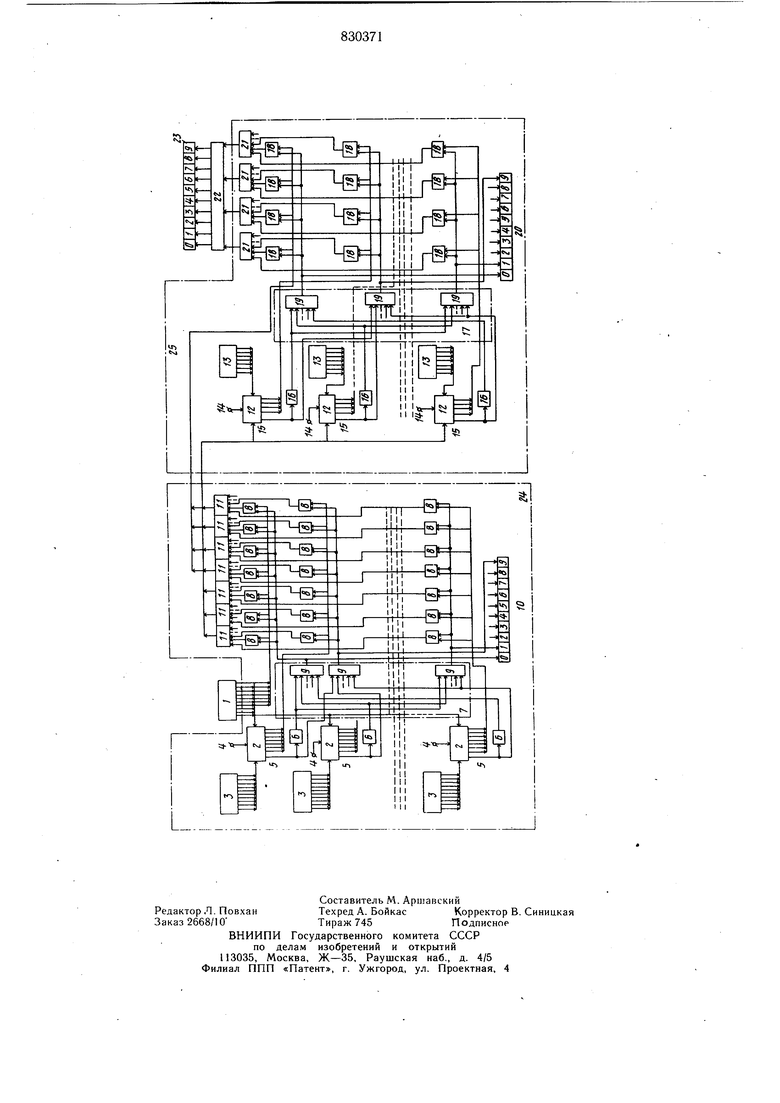

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении двоично-десятичных преобразующих устройств. Известен реверсивный преобразователь двоичного кода в двоично-десятичный, содержащий регистр, щифратор двоичных эквивалентов, сумматор, первый и второй входы которого соединены с выходами регистра и щифратора двоичных эквивалентов соответственно 1. Недостаток этого преобразователя заключается в низком быстродействии, обусловленном последовательным принципом обработки двоичных разрядов, необходимостью нескольких циклов для определения каждого десятичного разряда и последовательным определением десятичных разрядов. Наиболее близким к предлагаемому по технической сущности является преобразователь двоичного кода в десятичный, содержащий регистр двоичного числа, щифратор двоичных эквивалентов, блок формирования старщей единицы и выходной регистр. Кроме того, данный преобразователь содержит схему сравнения, два элемента задержки. сумматор, второй щифратор эквивалентов, и десять элементов И 2. Недостаток данного преобразователя заключается в низком быстродействии, связанном с последовательным принципом обработки двоичных разрядов и последовательны.м определением значений десятичных разрядов. Цель изобретения - повыщение быстродействия и помехоустойчивости. Поставленная цель достигается тем, что в преобразователь двоичного кода в десятичный, содержащий регистр двоичного числа, щифратор двоичных эквивалентов, блок формирования старщей единицы и выходной регистр, дополнительно введены дещифратор двоично-десятичного кода и (К-1) каскадов преобразования, где К - число десятичных разрядов, причем информационный вход первого каскада преобразования соединен с выходами регистра двоичного числа, информационные входы j-ro (j 2-(K-1) каскада преобразования соединены с информационными, выходами (j-I)-oro каскада преобразования, а выход (К-1)-ого каскада, преобразования через дещифратор двоично-десятичного кода соединен с группой входов выходного регистра младшегодесятичного разряда, а в каждый из каскадов преобразования введено девять сумматоров, девять элементов НЕ, блок выделения старшей единицы десять групп элементов И и группу элементов ИЛИ, выходы которых являются выходами каскада преобразования, а входы соединены с выходами одноименных элементов И групп, первые входы которых соединены с соответствуюшими выходами блока формирования старшей единицы и входами соответствуюш,их разрядов выходного регистра, вторые -входы элементов И первой группы соединены с младшими разрядами информационных входов каскада преобразования, вторые входы элеменТОВ и остальных групп соединены с разрядными выходами соответствующих сумматоров, выходы переноса которых соединены со входами соответствующих элементов НЕ и с прямыми входами блока выделения старшей единицы, инверсные входы которого соединены с выходами элементов НЕ, входы переноса всех сумматоров соединены с входом логической единицы, первые информационные входы сумматоров соединены с выходами шифратора двоичных эквивалентов, а вторые входы сумматоров соединены с информационными входами каскада преобразования. На чертеже приведена блок-схема предлагаемого преобразователя двоичного кода В десятичный. Преобразователь двоичного кода в десятичный содержит регистр 1 двоичного числа, подлежащего преобразованию, разрядные выходы которого соединены с первыми входами девяти сумматоров 2, вторые входы которых, соединены с выходами шифратора 3 двоичных эквивалентов задающих значения десятичных чисел данного разряда, кратных степени десяти, записанных обратными кодами. Здесь в качестве примера рассматривается преобразователь на три десятичных разряда. Входы 4 переноса сумматоров соединены с источником питания, напряжение которого соответствует значению логической единицы, а выходы 5 переноса сумматоров 2 соединены ; входами элементов НЕ 6, выходы которых соединены с входами блока 7 выделения старшей единицы, первый выход которого индицирует цифру нуль третьего десятичного разряда и соединен с первым входом одной из десяти групп элементов И 8, на вторые входы которых подведены выходы младших разрядов регистра 1 двоичного числа, обеспечивающие записи наибольшего десятичного числа младших десятичных разрядов. В данном случае числа 99, для записи которого требуется семь двоичных разрядов. Блок 7 выделения старшей единицы состоит. например, из элементов И 9, каждый из которых расшифровывает соответствующий номер старшей единицы среди сигналов переноса, выработанных сумматорами 2. Выходы блока 7 выделения старшей единицы соединены с входами соответствующих разрядов выходного регистра 10. Выходы элементов И 9 индицируют цифры третьего десятичного разряда: «1 - «9, и соединены с первыми входами каждой из остальных девяти групп элементов И 8, ко вторым входам которых подключены выходы младших разрядов сумматоров 2 индицируемой цифры. Выходы групп элементов И 8 одноименных двоичных разрядов соединены с входами группы элементов ИЛИ 11, выходы котортй образуют для смежного низшего десятичного разряда входной регистр двоичного числа, число разрядов которого определяет схему преобразователя для низшего разряда, повторяемую до получения четырехразрядной группы элементов ИЛИ. Для получения второго десятичного разряда выходы семи элементов ИЛИ группы 11 соединены с первыми входами девяти сумматоров 12, вторые входы которых соединены с выходами шифратора двоичных эквивалентов 13 десятичных данного разряда, кратных степеням десяти, записанных обратными кодами. Входы 14 переноса сумматоров 12 соединены с источником питания, напряжение которого соответствует значению логической единицы, а выходы 15 переноса этих сумматоров соединены со входами элементов НЕ 16, выходы которых подключены ко входам блока выделения старшей единицы 17, первый выход которой индицирует цифру «О второго десятичного разряда и соединен с первыми входами первой группы элементов И-18, на вторые входы которых подвешены выходы четырех младших разрядов входного регистра, образованного группой элементов ИЛИ 11. Блок выделения старшей единицы состоит, например, из элементов И 19. Четыре разряда входного регистра обеспечивают запись наибольщего десятичного числа младшего десятичного разряда, т.е. первого десятичного разряда. Выходы блока 17 выделения старшей единицы соединены с входами соответствующих разрядов выходного регистра 20 второго каскада. Выходы каждой из групп элементов И 18 одноименного двоичного разряда соединены со входами группы элементов ИЛИ 21. Число элементов в этой группе равно четырем, т.е. числу двоичных разрядов смежного десятичного разряда. Выходы элементов ИЛИ группы 21 соединены со входами дешифратора 22 двоично-десятичного кода, выходы которого индицируют цифры младшего десятичного разряда, т.е. первого десятичного разряда, и соединены со входами выходного регистра 23. В структуре предложенного трехразрядного преобразователя можно выделить два каскада 24 и 25 преобразования, причем выход каскада 25 преобразования через дешифратор двоично-десятичного кода 22 соединен с выходным регистром младшего десятичного разряда. Устройство работает . следующим образом. Если во входном регистре 1 преобразователя записано число 0000000000, то при его суммировании в двоичных сумматорах 2 третьей декады с десятичными эквивалентами двоичных чисел, кратных степени десяти, записанных в шифраторах 3, на выходах 5 переноса сумматоров третьего десятичного разряда появляется цифра «О. Производят, например, сложение содержимого регистра с двоичным эквивалентом десятичного числа 100, записанного в обратном коде: 100-4)001100100 1110011011 - в обратном коде 1110011011 0000000000 1 0.1110011100 Аналогичный результат дёют и остальные суммы, т.е. нигде не получается единицы переноса. Следовательно, на выходах всех элементов И 9, сигналы равны «О, кроме первой, на выходе которой сигнал равен 1, что соответствует цифре «О третьего десятичного разряда. Сигнал «О поступает на первые входы первой группы элементов И 8, на вторые входы которых подведены семь младших разрядов входного регистра 1. Но так как во всех этих разрядах записаны цифры «О, то на выходах этой группы элементов И 8 во всех разрядах сигнал также равен «О. На выходах остальных девяти элементов И 9 сигнал равен «О, так как на них заведены прямые и инверсные выходы 5 перенос, и следовательно, нигде совпадений не произойдет, потому что на прямом выходе перенос везде получен «О. Следовательно, на выходе всех семи элементов группы ИЛИ 11 сигналы также равны «О. Так как элементы ИЛИ группы 11 являются входным регистром для второй декады, то и во второй и в первой декаде индицируются цифры «О. Пусть теперь в регистре 1 записано число 1101010100- -852. Так как преобразуемое оно меньше эквивалента числа 900, но больше эквивалентов чисел 800, 700...100, то на выходе 5 переноса сумматора с подключенным шифратором эквивалента 900 сигнал равен «О, а на этих же выходах остальных сумматоров сигнал равен «1. Действительно: 900- 1110000100 0001111011в обратном коде. Произведя действия сумматоров, получают:1101010100 0001111011 0.1111010000 800 1100100000 1101010100 0011011111 1.0000110100 0011011111 - в обратном коде И Т.Д. Из всех десяти элементов И 9 сигнал «I присутствует только на выходе той, к которой подведены прямые выходы 5 перенос сумматоров, соединенных с эквивалентами чисел 800 и ниже, и инверсный выход перенос разряда сумматора, к которому подключен эквивалент цифры 900. Этот элемент И соответствует десятичной цифре 8 третьей декады. Н,а ее выходе получается сигнал, равный «1. Он же поступает и на первые входы семи элементов И 8, на вторые входы которых подведены выходы семи младших разрядов сумматора, к которому подсоединен двоичный эквивалент числа 800, т.е. подводится двоичное число 0110100, являюшееся-остатком, полученным при вычитании и подлежащем дальнейшему преобразованию. Так как на первых входах остальных групп элементов И 8 сигнал равен «О, то на выходе семи элементов ИЛИ группы 11 также записано это число, равное десятичному числу 52, которое подается на первые входы сумматоров 12. Сигнал «1 возникает на выходе перенос 15 только тех сумматоров 12, ко вторым входам которых подключены двоичные эквиваленты десятичных чисел, равные и меньше 50. Но так как на входы элементов И 9 подведены прямые выходы перенос- младших цифр по индицируемую включительно, дополнительные инверсными выходами перенос, то только на выходе элемента И 19, соответствующего цифре 5 второго десятичного разряда, появляется сигнал «1, который одновременно поступает на первый вход группы элементов И 18, вторые входы которых соединены с выходами четырех разрядов сумматора 12, к которому подключен двоичный эквивалент числа 50- 0110010 1001101 в обратном коде. Этот сумматор производит операцию: 0110100 1001101 1.0000010 Таким образом, на выходе этой группы оявляется двоичное число 0010. Так как на выходе всех остальных элементов И группы 18 сигналы равны «О, то на выходах группы элементов ИЛИ 21 записано то же самое число 0010, которое далее подается на входы двоично-десятичного дешифратора 22. На соответствующем выходе дешифратора индицируется десятичное число «2. Подаваемые на преобразователь числа должны быть ограничены числом 999, в противном случае необходимо добавить соответствующие старшие десятичные разряды. Быстродействие предлагаемого преобразователя двоичного кода в десятичный определяется лишь временами задержек, возникаюш,их в микросхемах, на которых собран преобразователь. Практически требуется одно суммирование для получения значения одного десятичного разряда. Поэтому в сравнении с многотактным преобразователем 2 быстродействие предлагаемого преобразователя повышается в сотни раз. Формула изобретения Преобразователь двоичного кода в десятичный, содержаш,ий регистр двоичного числа, шифратор двоичных эквивалентов и выходной регистр, отличающийся тем, что, с целью увеличения быстродействия и повышения помехоустойчивости, в него введен дешифратор двоично-десятичного кода и (К-1) каскадов преобразования, где К- число десятичных разрядов, причем информационный вход первого каскада преобразования соединен с выходами регистра двоичного числа, информационные входы j-oro (j 2-(К-1) каскада преобразования соединены с информационными выходами (j-l)-ro каскада преобразования, а выход (К-1)-опо каскада преобразования через дешифратор двоично-десятичного кода соединен с группой входов выходного регистра младшего десятичного разряда, причем в каждый из каскадов преобразования содержит девять сумматоров, девять элементов НЕ, блок выделения старшей единицы, десять групп элементов И и группу элементов ИЛИ, выходы которых являются выходами каскада преобразования, а входы соединены с выходами одноименных элементов И групп, первые входы которых соединены с соответствующими выходами блока старшей единицы и входами соответствующих разрядов выходного регистра, вторые входы элементов И первой группы соединены с младшими разрядами информационных входов каскада преобразования, вторые входы элементов И остальных групп соединены с разрядными выходами соответствующих сумматоров, выходы переноса которых соединены со входами соответствующих элементов НЕ и прямыми входами выделения блока старщей единицы, инверсные входы которого соединены с выходами элементов НЕ, входы переноса всех сумматоров соединены с входом логической единицы, первые информационные входы сумматоров соединены с выходами шифратора двоичных эквивалентов, а вторые входы сумматоров соединены с информационными входами каскада преобразования. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 620975, кл. G 06 F 5/02, 1977. 2.Авторское свидетельство СССР № 523406, кл. G 06 F 5/02, 1973 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в двоично-десятичный | 1979 |

|

SU773616A1 |

| Реверсивный преобразовательдВОичНОгО КОдА B дВОичНО-дЕСяТичНый | 1979 |

|

SU849198A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1283979A1 |

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код градусов,минут,секунд | 1980 |

|

SU960791A1 |

| Преобразователь двоично-десятичногоКОдА B дВОичНый | 1979 |

|

SU798800A1 |

| Преобразователь кодов | 1978 |

|

SU744548A1 |

| Реверсивный преобразователь двоичного кода в двоично-десятичный | 1988 |

|

SU1621182A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1980 |

|

SU957200A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1285604A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

Авторы

Даты

1981-05-15—Публикация

1979-04-19—Подача