1

Изобретение относится к области вычислительной техники и может использоваться в цифровых вычислительных устройствах.

Известны сдвигающие регистры, каждый разряд которых состоит из двух полутактовых триггерных ячеек, каждая из которых включает два двухэмиттерных транзистора, причем коллектор первого, подключен к базе второго и к первому резистору, а коллектор второго - к базе первого и ко второму резистору.

Однако известный сдвигающий регистр имеет невысокое быстродействие, так как следующая ячейка переключается частью тока, текущего через одно из коллекторных сопротивлений. Кроме того, такие ячейки критичны к параметрам активных компонентов схемы, что снижает надежность регистра.

Цель изобретения - повысить надежность и увеличить быстродействие устройства.

Это достигается введением в каждую триггерную ячейку двух переключающих транзисторов, коллекторы которых подключены к коллекторам двухэмиттерных транзисторов, эмиттеры переключающих транзисторов и первые эмиттеры двухэмиттерных транзисторов каждой ячейки подключены к соответствующей управляющей тактовой шине, резисторы каждой ячейки - к соответствующей тактовой щине питания, базы переключающих транзисторов второй ячейки подключены ко

вторым эмиттерам двухэмиттерных транзисторов первой ячейки, базы переключающих

транзисторов которой подключены ко вторым

эмиттерам двухэмиттерных транзисторов триггерной ячейки последующего разряда.

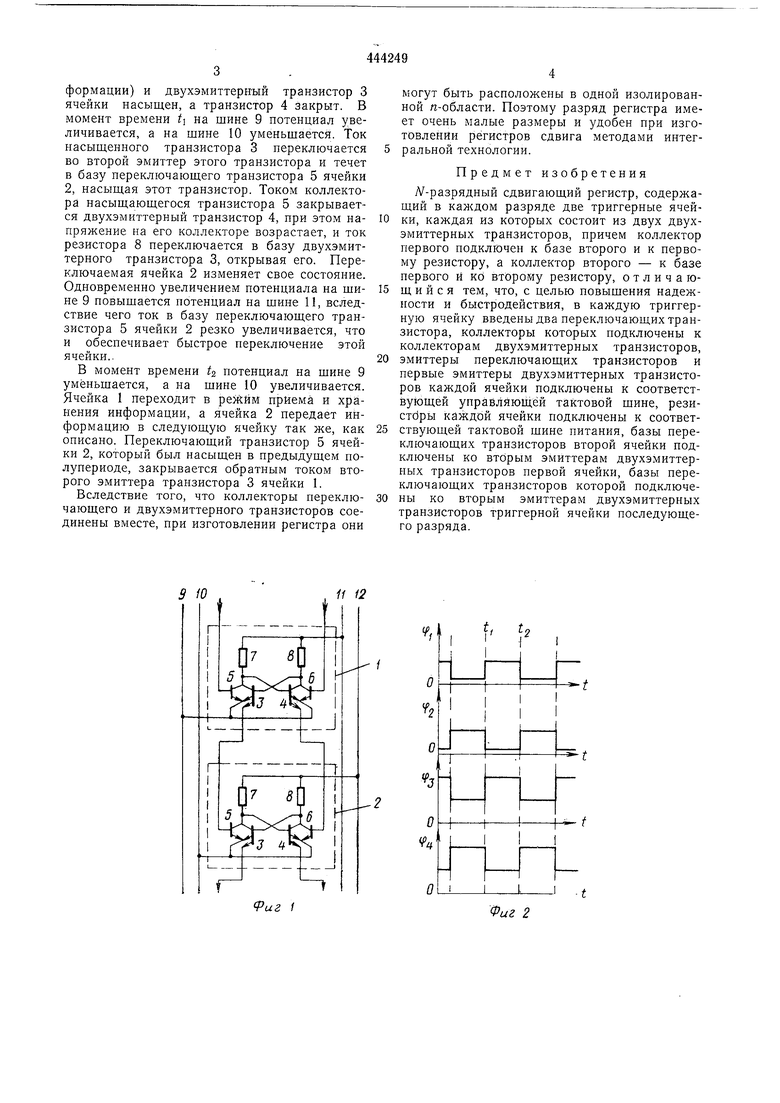

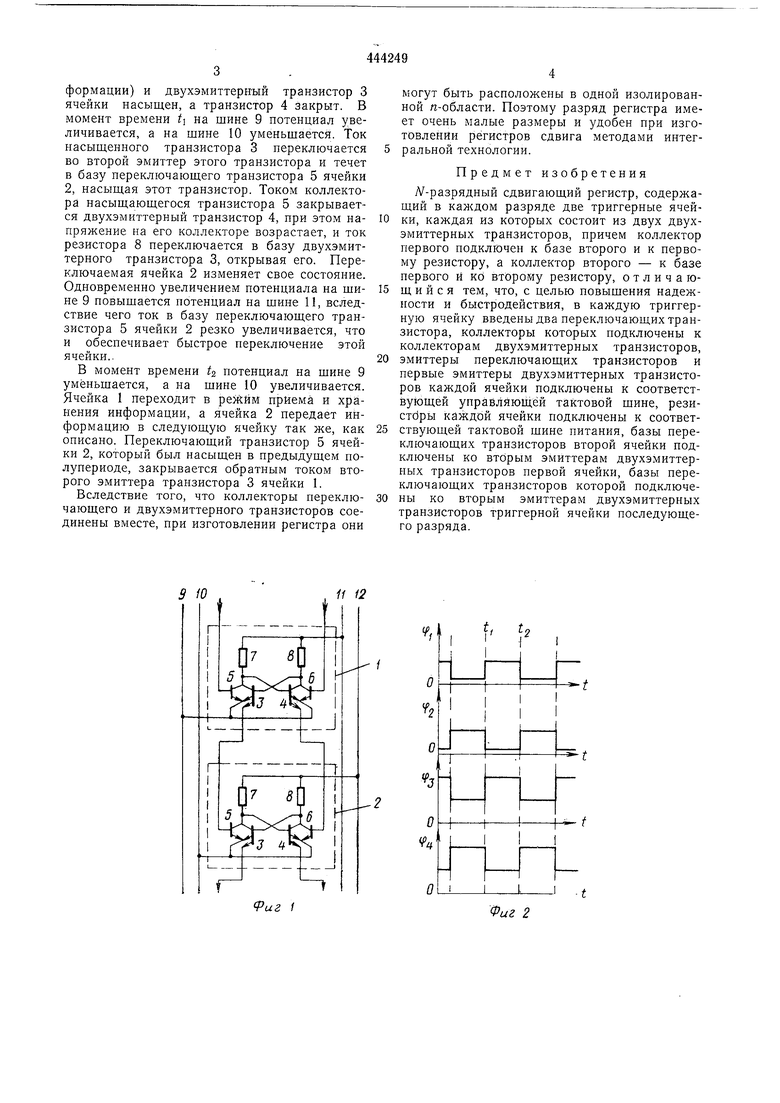

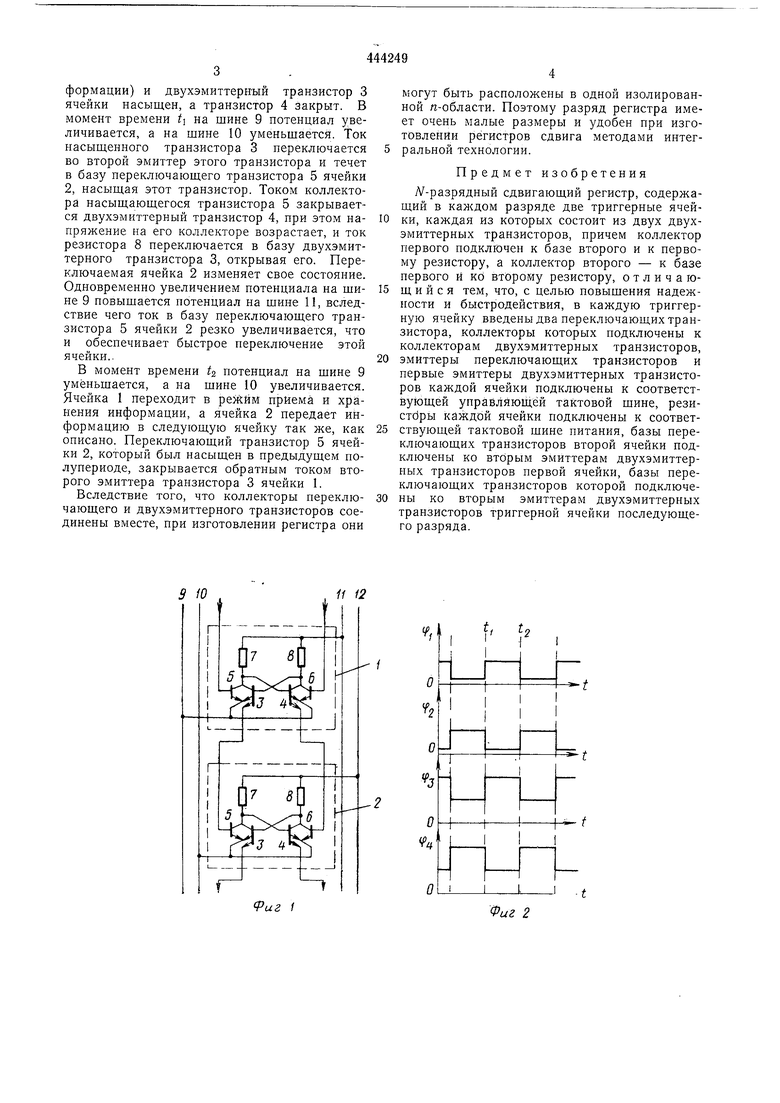

На фит.. 1 изображена принципиальная схема одного разряда Л-разрядного сдвигающего регистра; на -фиг. 2 - управляющие (ф и Ф2 тактовые импульсы и Тактовые импульсы

для питания фз и 94) предлагаемого регистра. Разряд Л -разрядного сдвигающего регистра состоит из двух одинаковых триггерных ячеек 1 и 2, каждая из которых содержит два двухэмиттерных транзистора 3 и 4 с перекрестными связями,, переключающие транзисторы 5 и 6, коллекторы которых подключены к резисторам 7 и 8. Передача информации происходит с помощью управляющих тактовых импульсов ф1 и ф2, которые подаются соответственно по шинам 9 и 10. Изменение величин токов при переходе из режима хранения в режим передачи информации осуществляется путем использования тактовых импульсов питания фз и ф4, ирилол ;енных соответственно к

щинам 11 и 12.

Сдвигающий регистр работает следующим образом.

Пусть к щине управляющих тактовых импульсов 9 прилол ен низкий уровень потенциала (ячейка 1 работает в режиме хранения ин

| название | год | авторы | номер документа |

|---|---|---|---|

| Накопитель для запоминающего устройства | 1983 |

|

SU1137537A1 |

| Ячейка памяти | 1973 |

|

SU444244A1 |

| Формирователь сигналов записи и считывания | 1983 |

|

SU1113852A1 |

| Ячейка памяти | 1974 |

|

SU536527A1 |

| РЕГИСТР СДВИГА | 1973 |

|

SU364029A1 |

| Ячейка памяти | 1973 |

|

SU444245A1 |

| Ячейка памяти | 1974 |

|

SU491998A1 |

| Оперативное запоминающее устройство | 1979 |

|

SU903972A1 |

| Ячейка памяти для регистра сдвига | 1979 |

|

SU851495A1 |

| Сдвигающий регистр с импульсным питанием | 1973 |

|

SU479154A1 |

Авторы

Даты

1974-09-25—Публикация

1973-04-12—Подача