1

Устройство предназначено для автоматического управления светофорной сигнализацией при двухфазной схеме организации движения транспорта с последовательным переключением тактов.

Известно устройство управления дорожными сигналами, содержащее четыре схемы с двумя устойчивыми состояниями, включающие сигналы предостерегающий, зеленый по магистрали, предостерегающий, зеленый по пересечению, четыре схемы выдержки времени для определения времени длительности горения каждого сигнала. На каждый такт имеется своя схема памяти и схема выдержки времени.

С целью повышения надежности в устройстве выход блока памяти промежуточных тактов переключения подключен ко входу первого элемента выдержки времени, к выходу устройства и к одному из своих входов, выход первого элемента времени подключен ко входу «сброс блока памяти промежуточных тактов и ко входу блока памяти основных тактов, выход одного каскада которого подключен ко входам двух логических элементов «И, а выход другого каскада соединен со входом первого каскада блока памяти основных тактов переключения, выходы логических схем «И подключены к соответствующим выходам устройства и соответственно через второй и третий элемент выдержки времени - ко входу

первого каскада и ко входу «сброс второго каскада блока памяти отрабатываемого такта переключения, выходы второго и третьего элементов выдержки времени подключены ко входам «сброс блока памяти основных тактов и к соответствующим входам блока памяти промежуточных тактов переключения выход первого каскада блока памяти отрабатываемого такта подключен ко входу второго каскада и ко входу одного элемента «И, вход другого элемента «PI соединен с выходом второго каскада блока памяти отрабатываемого такта переключения.

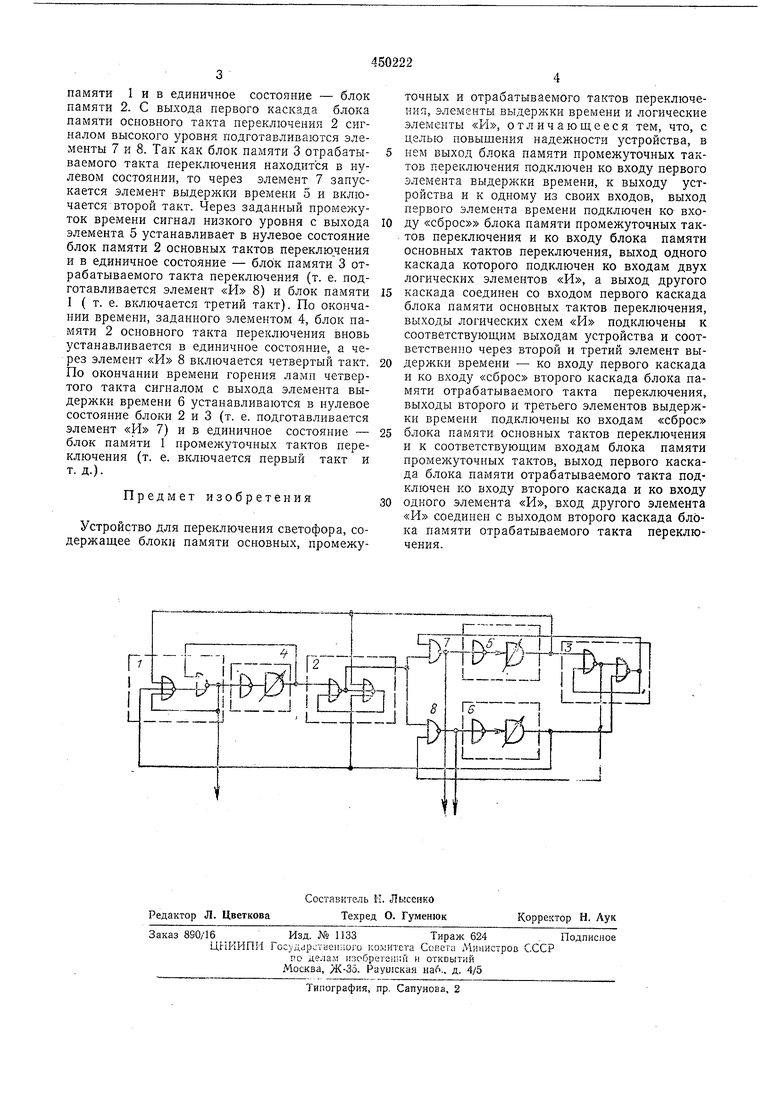

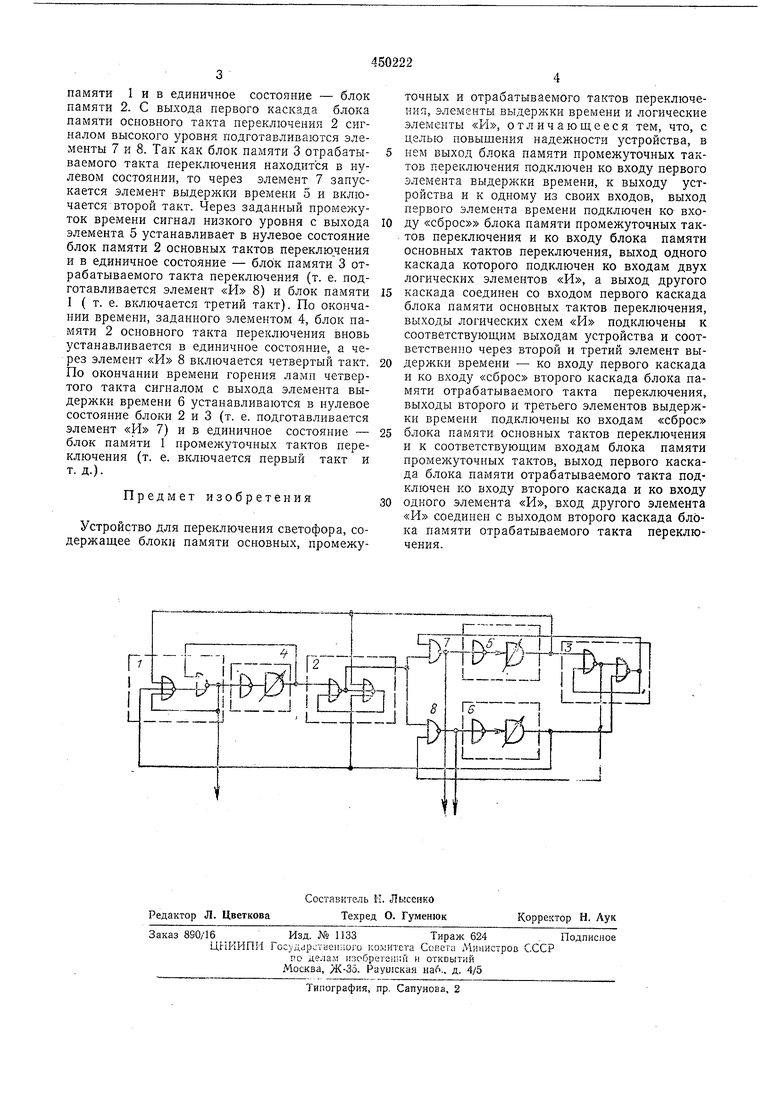

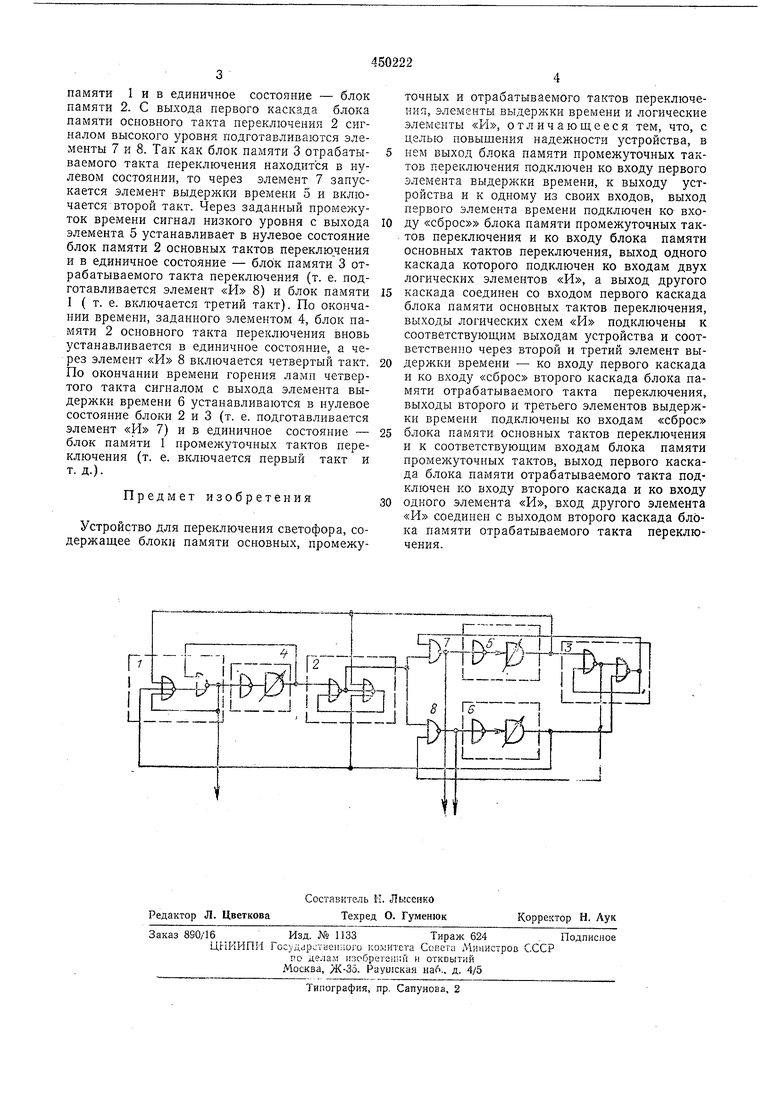

На чертеже представлена схема устройства, содержащего: блок памяти 1 промежуточных тактов переключения; блок памяти 2 основных тактов нереключения; блок памяти 3 отрабатываемого такта переключения; элементы выдержки времени 4-6; логические элементы «И 7, 8.

Устройство работает следующим образом.

Предположим идет первый такт, т. е. блок памяти промежуточного такта переключения формирует на выходе сигнал низкого уровня, т. е. включен элемент выдержки времени 4 и на выходе устройства горят лампы промежуточного такта. Через время, заданное элементом выдержки времени 4, на выходе элемента 4 появляется сигнал низкого уровня, который устанавливает в исходное состояние блок

памяти 1 и в единичное состояние - блок памяти 2. С выхода первого каскада блока памяти основного такта переключения 2 сигналом высокого уровня подготавливаются элементы 7 и 8. Так как блок памяти 3 отрабатываемого такта переключения находится в нулевом состоянии, то через элемент 7 запускается элемент выдержки времени 5 и включается второй такт. Через заданный промежуток времени сигнал низкого уровня с выхода элемента 5 устанавливает в нулевое состояние блок памяти 2 основных тактов переключения и в единичное состояние - блок памяти 3 отрабатываемого такта переключения (т. е. подготавливается элемент «И 8) и блок памяти I ( т. е. включается третий такт). По окончании времени, заданного элементом 4, блок памяти 2 основного такта переключения вновь устанавливается в единичное состояние, а через элемент «И 8 включается четвертый такт. По окончании времени горения ламп четвертого такта сигналом с выхода элемента выдержки времени 6 устанавливаются в нулевое состояние блоки 2 и 3 (т. е. подготавливается элемент «И 7) и в единичное состояние - блок памяти 1 промежуточных тактов переключения (т. е. включается первый такт и т. д.)Предмет изобретения

Устройство для переключения светофора, содержащее блоки памяти основных, промежуточных и отраоатываемого тактов переключения, элементы выдержки времени и логические элементы «И, отличающееся тем, что, с целью повышения надежности устройства, в

нем выход блока памяти промежуточных тактов переключения подключен ко входу первого элемента выдержки времени, к выходу устройства и к одному из своих входов, выход первого элемента времени подключен ко входу «сброс блока памяти промежуточных тактов переключения и ко входу блока памяти основных тактов переключения, выход одного каскада которого подключен ко входам двух логических элементов «И, а выход другого

каскада соединен со входом первого каскада блока памяти основных тактов переключения, выходы логических схем «И подключены к соответствующим выходам устройства и соответственно через второй и третий элемент выдержки времени - ко входу первого каскада и ко входу «сброс второго каскада блока памяти отрабатываемого такта переключения, выходы второго и третьего элементов выдержки времени подключены ко входам «сброс

блока памяти основных тактов переключения и к соответствующим входам блока памяти промежуточных тактов, выход первого каскада блока памяти отрабатываемого такта подключен ко входу второго каскада и ко входу

одного элемента «И, вход другого элемента «И соединен с выходом второго каскада блока памяти отрабатываемого такта переключения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для телеуправления, например, светофором | 1973 |

|

SU445677A1 |

| Цифровой фильтр | 1988 |

|

SU1569966A1 |

| Многоканальное устройство приоритета | 1979 |

|

SU824210A1 |

| УСТРОЙСТВО ТЕСТОВОГО КОНТРОЛЯ КОМПЛЕКТА ЗАЩИТ ФИЛЬТРОВ ВЫСШИХ ГАРМОНИК | 1993 |

|

RU2066867C1 |

| Ультразвуковой датчик производительности горной машины | 1981 |

|

SU956786A1 |

| Устройство для управления процессомСВАРКи | 1979 |

|

SU821098A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| Логический анализатор | 1989 |

|

SU1730627A1 |

| Устройство для считывания изображений | 1986 |

|

SU1429142A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1260961A1 |

А 1 I-: U iR:-T- lP p:iiq-|- У/У i I I ,рч Clj

Авторы

Даты

1974-11-15—Публикация

1973-01-29—Подача