(54) МНОЖИТЕЛЬНОЕ УСТРОЙСТВО ПОСЛЕДОВАТЕЛЬНОГО ДЕЙСТВИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

| Устройство для умножения чисел с плавающей запятой | 1985 |

|

SU1280624A1 |

| Устройство для умножения | 1989 |

|

SU1667061A1 |

| Устройство для умножения чисел в @ -кодах Фибоначчи | 1980 |

|

SU1137459A1 |

| Устройство для умножения | 1976 |

|

SU651341A1 |

| Устройство для умножения чисел | 1988 |

|

SU1658147A1 |

| Устройство для умножения | 1988 |

|

SU1654814A2 |

| Цифровой преобразователь координат | 1985 |

|

SU1290307A1 |

| Устройство для умножения | 1981 |

|

SU1018115A1 |

| Арифметическое устройство | 1984 |

|

SU1236473A1 |

1

Изобретение относится к области вычислительной тезшики и может быть приме нено в цифровых вычислительных машинах последовательного действия.

Известны множительные устройства последовательного действия, содержащие блок управления, выход которого соединен с управляющими входами сумматора и регистра произведения, вход которого подключен к выходу сумматора, первые информационные входы которого соединены соответственно с информационными выходами регистра множимого, а вторые информационные входы - соответственно с информационными выходами регистра множителя, информационный вход которого подключен к выходу первой схемы И, первый вход которой связан с выходом схемы НЕ, вход которой соединен с первым входом устройства, второй вход которого подключен к первому входу второй схемы И, выход которой подключен к информационному входу регистра множимого.

Предлагаемое устройство отличается от известных тем, что, с целью увеличения

быстродействия, оно содержит сдвиговый регистр, вход которого соединен с выходом блока управления, а выходы всех разрядов - с соответствующими входами первого и второго коммутаторов, выходы которых подключены соответственно к информационным входам регистров множимого н множителя, а управляющие входы - соответственно к выходам первой и второй дополнительных схем И, первые входы которых соединены соответственно с первым входом устройства и с выходом дополнительной схемы НЕ,, вход которой связан со вторым входом устройства, приче(л вторые входы первой схемы И и первойхдополнительной схемы И соединены :с первым дополнительным выходом блока управления второй дополнительный выход которого соединен со вторым входом второй схемы И, и второй дополнительной схемы И.

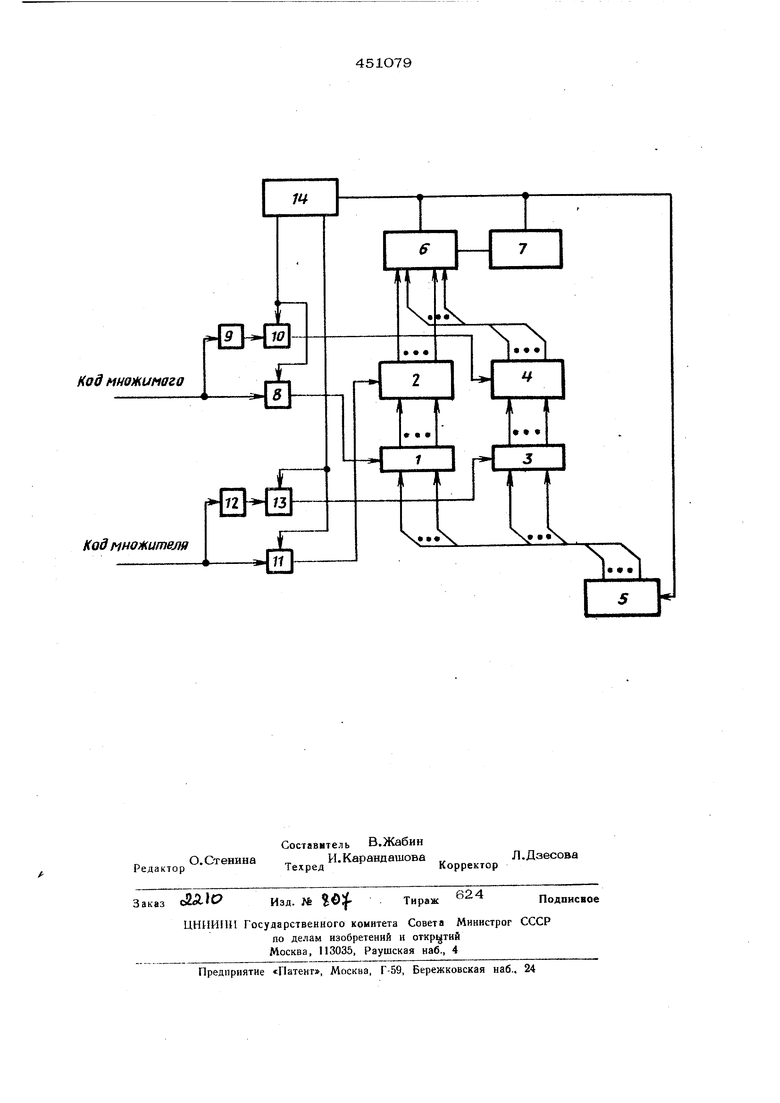

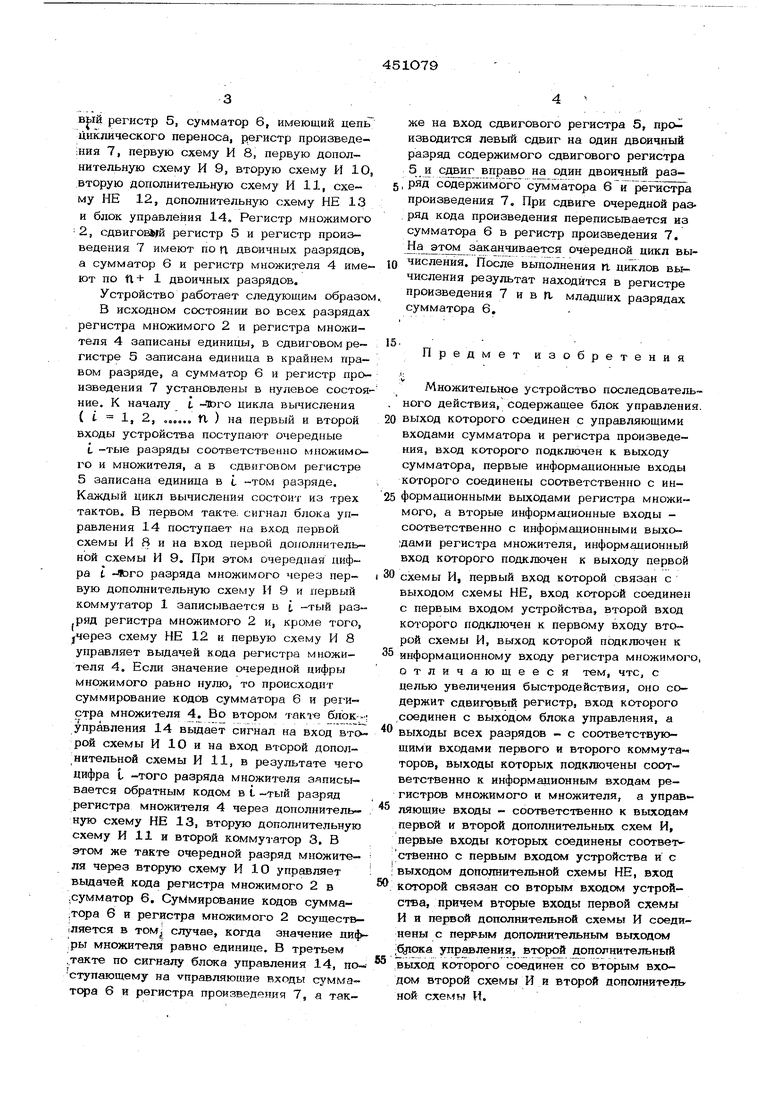

На чертеже приведена структурная схема предлагаемого устройства.

Устройство содержит первый коммутатор 1, регистр множимого 2, второй коммутатор 3, регистр множителя 4, сдвиговый регистр 5, сумматор 6, имеющий цепь циклического переноса, регистр произведе ния 7, первую схему И 8, первую дополнительную схему И 9, вторую схему И 10 вторую дополнительную схему И 11, схему НЕ 12, дополнительную схему НЕ 13 и блок управления 14, Регистр множимого 2, сдвиговой регистр 5 и регистр произведения 7 имеют по п. двоичных разрядов, а сумматор 6 и регистр множителя 4 имеЮт по ft + 1 двоичных разрядов.

Устройство работает следующим образо

В исходном состоянии во всех разрядах регистра множимого 2 и регистра множителя 4 записаны единицы, в сдвиговом ре- гистре 5 записана единица в крайнем пра- вом разряде, а сумматор 6 и регистр произведения 7 установлены в нулевое состояние, К началу L -loro цикла вычисления

( t 1, 2, « П ) на первый и второй

входы устройства поступают очередные

i -тые разряды соответственно множимого и множителя, а в сдвиговом регистре 5 записана единица в с -том разряде. Каждый цикл вычисления состоит из трех тактов. В первом такте; сигнал блока управления 14 поступает на вход первой схемы И 8 и на вход первой дополнительной схемы И 9, При этом очередная цифра I -Чого разряда множимого через первую дополнительную схему И 9 и первый коммутатор 1 записывается в I -тый разряд регистра множил ого 2 и, кроме того, |Через схему НЕ 12 и первую схему И 8 управляет выдачей кода регистра множителя 4, Если значение очередной цифры множимого равно нулю, то происходит суммирование кодов сумматора 6 и регистра множителя 4. Во втором такте блок-управления 14 выдает сигнал на вход вт( рой схемы И 10 и на вход второй дополнительной схемы И 11, в результате чего йифра L -того разряда множителя записывается обратным кодом в i -тый разряд регистра множителя 4 через дополиителькую схему НЕ 13, вторую дополнительную схему И 11 и второй коммутатор 3. В этом же такте очередной разряд множителя через вторую схему И 1О управляет вьщачей кода регистра множимого 2 в

.сумматор 6. Суммирование кодов сумма;тора 6 и регистра множимого 2 осуществ- .ляется в TOMJ случае, когда значение диф,ры множителя равно единице. В третьем ..такте по сигналу блока управления 14, поступающему на управляющие входы сумматора 6 и регистра произведения 7, а так4

же на вход сдвигового регистра 5, производится левый сдвиг на один двоичный разряд содержимого сдвигового регистра 5 и сдаир вправо на один двоичный разряд содержимого сумматора 6 и регистра произведения 7. При сдвиге очередной разряд кода произведения переписывается из сумматора 6 в регистр произведения 7. заканчивается очередной цикл вычисления. После выполнения п. циклов вычисления результат находится в регистре произведения 7 и в (г младших разрядах сумматора 6.

Предмет изобретения

Множительное устройство последовательного действия, содержащее блок управлени выход которого соединен с управляющими входами сумматора и регистра произведения, вход которого подключен к выходу сумматора, первые информационные входы которого соединены соответственно с информационными выходами регистра множимого, а вторые информационные входы соответственно с информационными выходами регистра множителя, информационный вход которого подключен к выходу первой

схемы И, первый вход которой связан с выходом схемы НЕ, вход которой соединен с первым входом устройства, второй вход которого подключен к первому входу второй схемы И, выход которой подключен к информационному входу регистра множимог отличающееся тем, чтс, с целью увеличения быстродействия, оно содержит сдвиговьгй регистр, вход которого соединен с выходом блока управления, а выходы всех разрядов - с соответствующими входами первого и второго коммутаторов, выходы которых подключены соответственно к информационным входам регистров множимого и множителя, а управляющие входы - соответственно к выходам первой и второй дополнительных схем И, первые входы которых соединены соответственно с первым входом устройства и с выходом дополнительной схемы НЕ, вход которой связан со вторым входом устройства, причем вторые входы первой схемы И и первой дополнительной схемы И соединены с первым дополнительным выходом GflOKa управления, второй дополнительный выход которого соединен со вторым входом второй схемы И и второй дополнитель ной схемы И.

Код мно)Кимого

Код мнозиитвля

Авторы

Даты

1974-11-25—Публикация

1973-04-18—Подача