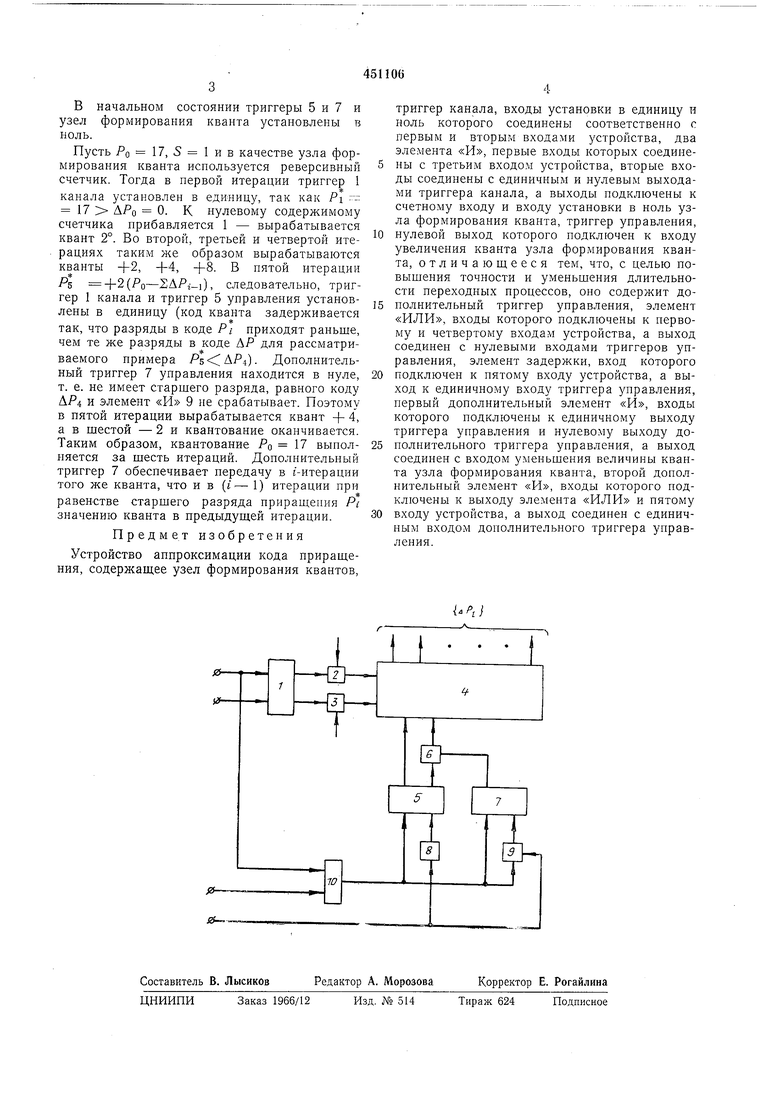

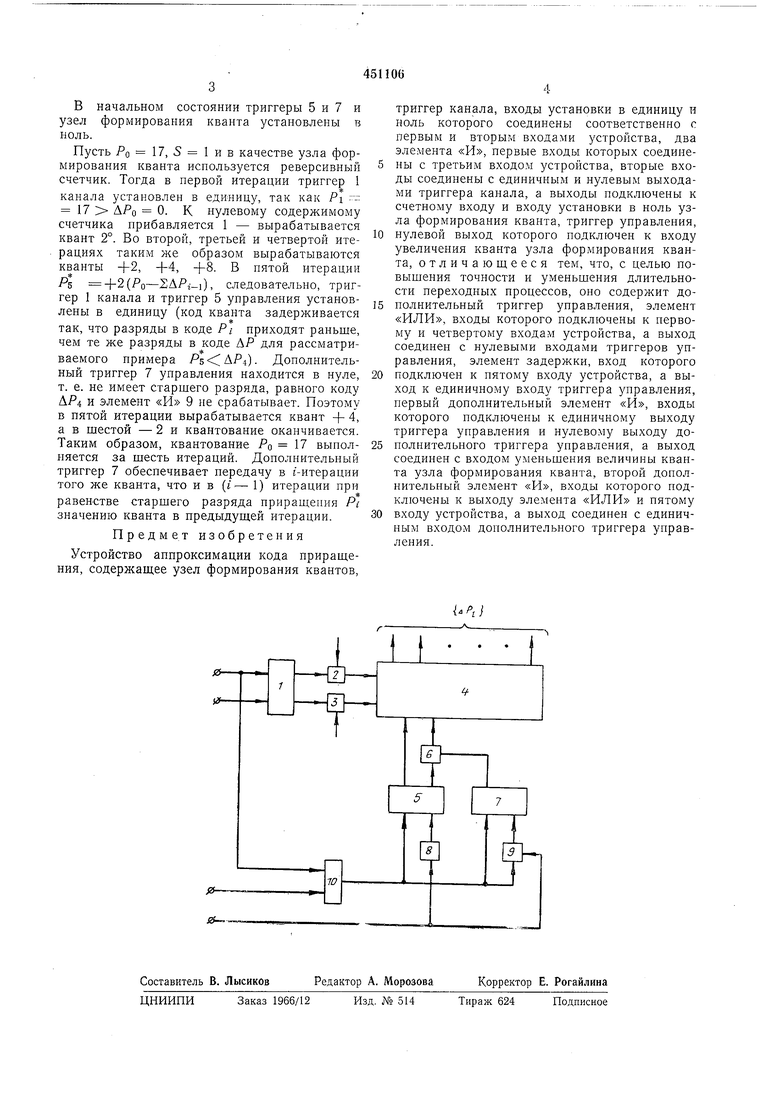

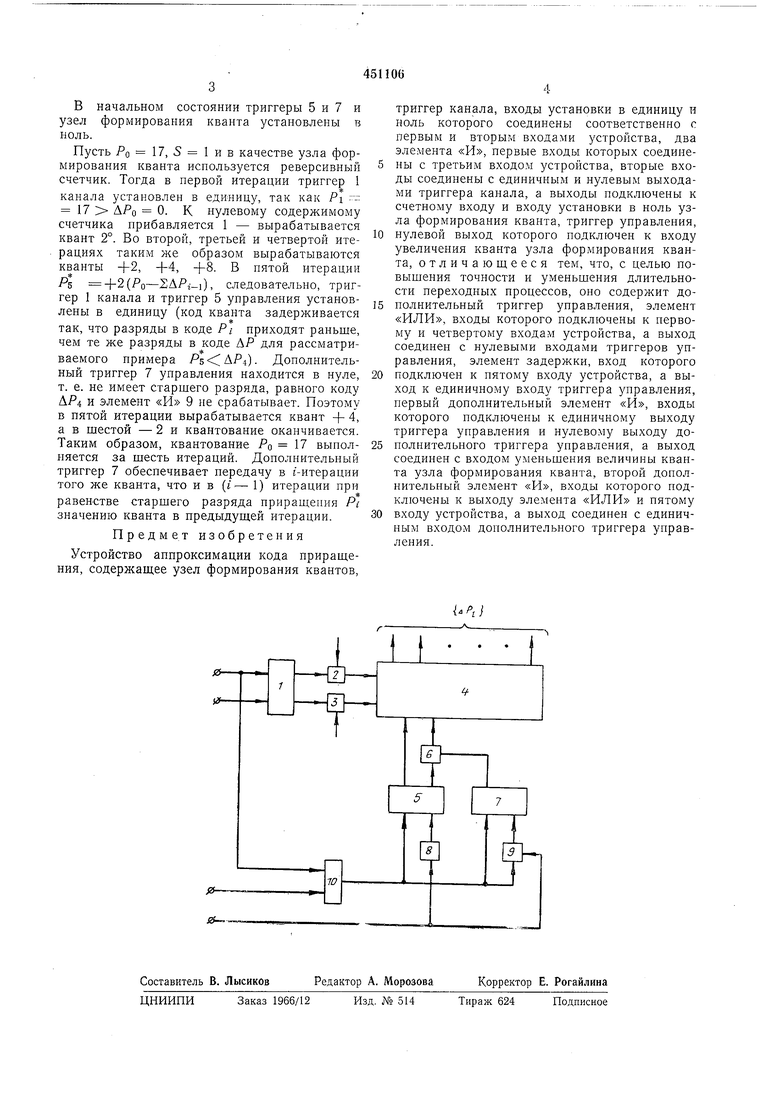

Изобретение относится к вычислительной технике и может быть использовано при построении цифровых интегрирующих машин. Известны устройства аппроксимации кода приращения, содержащие узел формирования квантов, триггер канала, входы установки в единицу и ноль которого соединены соответственно с первым и вторым входами устройства, два элемента «И, первые входы которого соединены с третьим входом устройства, вторые входы соединены с единичным и нулевым выходами триггера канала, а выходы подключены к счетному входу и входу установки в ноль узла формирования квантов, триггер управления, нулевой выход которого подключен к входу увеличения кванта узла формирования кванта. Цель изобретения - повысить точность и уменьщить длительность переходных процессов. Для этого устройство содержит дополнительный триггер управления, элемент «ИЛИ, входы которого подключены к первому и четвертому входам устройства, а выход соединен с нулевыми входами триггеров управления, элемент задержки, вход которого подключен к пятому входу устройства, а выход к единичному входу триггера управления, первый дополнительный элемент «И, входы которого подключены к единичному выходу триггера управления и нулевому выходу дополнительного триггера управления, а выход соединен с входом уменьщения величины кванта узла формирования кванта, второй дополнительный элемент «И, входы которого подключены к выходу элемента «ИЛИ и пятому входу устройства, а выход соединен с единичным входом дополнительного триггера управления. На чертеже показано предлагаемое устройство. УстроР1ство содержит триггер 1 канала, элементы 2 и 3 «И, узел 4 формирования кванта, триггер 5 управления, первый дополнительный элемент 6 «И, дополнительный триггер 7 управления, элемент 8 задержки, второй дополнительный элемент 9 «И, элемент 10 «ИЛИ. Устройство работает следующим образом. На вход триггера 1 канала поступают коды полного приращения: : Р - 5ДЛ-.-Ь где ДРг-1 - значение кванта в (i-1) итерации, i 1, 2 . .. - номер текущей итерации, масщтабного коэффициента 5, что позволяет выявить О (деление производится по модулю старшего разряда S).

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО для АППРОКСИМАЦИИ КОДА ПРИРАЩЕНИЯ | 1973 |

|

SU374634A1 |

| Решающий блок цифровой интегрирующей структуры | 1983 |

|

SU1104514A1 |

| Цифровая интегрирующая структура | 1980 |

|

SU900300A1 |

| Модуль интегрирующей вычислительной структуры | 1982 |

|

SU1101821A1 |

| Устройство для диагностики неисправностей цифровых интеграторов | 1979 |

|

SU877551A1 |

| Модуль интегрирующей вычислительной структуры | 1984 |

|

SU1257641A1 |

| Интегрирующая вычислительная структура | 1981 |

|

SU1257672A1 |

| Устройство управления цифровой интегрирующей структуры | 1978 |

|

SU789993A1 |

| Устройство для сопряжения с датчиками | 1991 |

|

SU1800459A1 |

| Процессор быстрого преобразования Фурье | 1982 |

|

SU1086438A1 |

Авторы

Даты

1974-11-25—Публикация

1972-12-21—Подача