1

Изобретение относится к области вычислительной техники и может быть использовано в запоминающих устройствах цифровых вычислительных машин.

Известно интегральное запоминающее устройство (ЗУ), содержащее накопитель, ячейки памяти которого содержат МДП-транзисторы с изменяемым порогом включения, и дешифраторы 1. Известное устройство имеет низкое быстродействие и требует высоких входных уровней напряжения при записи информации.

Наиболее близким к изобретению является интегральное запоминающее устройство, содержащее матричный накопитель, каждая ячейка памяти которого содержит последовательно включенные МДП-транзистор с изменяемым порогом включения и вентильный МДП-транзистор, затворы вентильных МДПтранзисторов каждой строки подключены к соответствующим выходам дешифратора строк, истоки вентильных МДП-транзисторов - к выходной шине через МДП-транзисторы выборки, затворы которых подсоединены к соответствующим выходам дешифратора столбцов, затворы МДП-транзисторов с изменяемым порогом включения - к управляющей шине, шину питания и шину нулевого потенциала 2.

Недостатками этого устройства являются низкое быстродействие при считывании из-зя

малой крутизны нагрузочного транзистора и повышенная мощность рассеяния при записи вследствие статического характера работы ячеек памяти при записи.

Цель изобретения - повышение быстродействия и уменьшение рассеиваемой мощности интегрального запоминающего устройства.

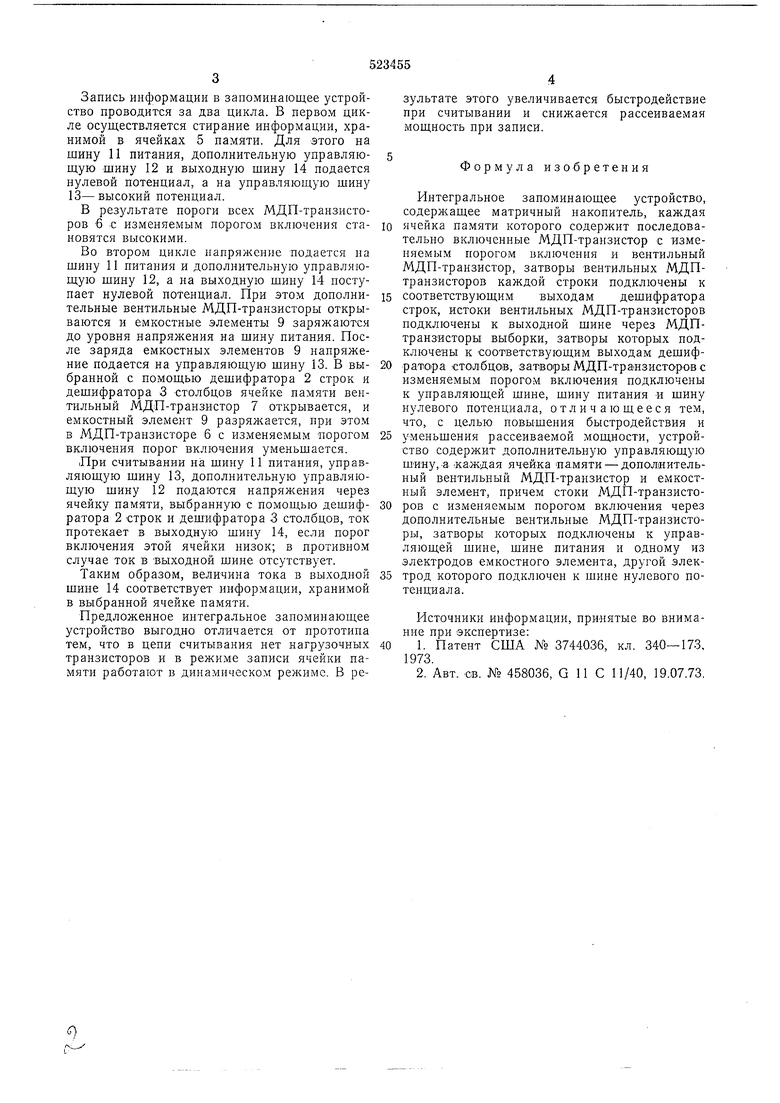

Для этого устройство содержит дополнительную управляющую шину, а каждая ячейка памяти дополйительный вентильный МДП-транзистор и емКостный элемент, стоки МДП-транзисторов с изменяемым порогом включения через дополнительные вентильные МДП-транзисторы, затворы которых подключены к управляющей шине, к шине питания и одному из электродов емкостного элемента, другой электрод которого подсоединен к шине нулевого потенциала. На чертеже представлена схема устройства.

Запоминающее устройство содержит матричный накопитель 1, дешифратор 2 строк, дешифратор 3 столбцов, МДП-транзисторы 4 выборки, ячейки 5 памяти, МДП-транзисторы 6 с изменяемым порогом включения, вентильные МДП-транзисторы 7, дополнительные вентильные МДП-транзисторы в, емкостные элементы 9, шину 10 нулевого потенциала, шину И питания, дополнительную управляющую шину 12, управляющую шину 13 и выходную

шину 14. Запись информации в запоминающее устройство проводится за два цикла. В первом цикле осуществляется стирание информации, хранимой в ячейках 5 памяти. Для этого на шину И питания, дополнительную управляю-s щую шину 12 и выходную шину 14 подается нулевой потенциал, а на управляющую шину 13-высокий потенциал. В результате пороги всех МДП-транзисторов 6 € изменяемым порогом включения ста-ю новятся высокими. Во втором цикле напряжение подается на шину И питания и дополнительную управляющую шину 12, а на выходную шину 14 поступает нулевой потенциал. При этом дополни-is тельные вентильные МДП-транзисторы открываются и емкостные элементы 9 заряжаются до уровня напряжения на шину питания. После заряда емкостных элементов 9 напряжение поддается на управляющую шину 13. В вы-20 бранной с помощью дешифратора 2 строк и дешифратора 3 столбцов ячейке памяти вентильный МДП-транзистор 7 открывается, и емкостный элемент 9 разрялсается, при этом в МДП-транзисторе 6 с изменяемым порогом25 включения порог включения уменьшается. (При считывании на шину И питания, управляющую шину 13, дополнительную управляющую шину 12 подаются напряжения через ячейку памяти, выбранную с помощью дешиф-30 ратора 2 строк и дешифратора 3 столбцов, ток протекает в выходную шину 14, если порог включения этой ячейки низок; в противном случае ток в выходной шине отсутствует. Таким образом, величина тока в выходной35 шине 14 соответствует информации, хранимой в выбранной ячейке памяти. Предложенное интегральное запоминающее устройство выгодно отличается от прототипа тем, что в цепи считывания нет нагрузочных40 транзисторов и в режиме записи ячейки памяти работают в динамическом режиме. В результате этого увеличивается быстродействие при считывании и снижается рассеиваемая мощность при записи. Формула изобретения Интегральное запоминающее устройство, содерлсащее матричный накопитель, каждая ячейка памяти которого содержит последовательно включенные МДП-транзистор с изменяемым порогом включения и вентильный МДП-транзистор, затворы вентильных МДПтранзисторов каждой строки подключены к соответствующим выходам дешифратора строк, истоки вентильных МДП-транзисторов подключены к выходной шине через МДПтранзисторы выборки, затворы которых подключены к соответствующим выходам дешифратора столбцо-в, затворы МДП-транзисторов с изменяемым порогом включения подключены к управляющей шине, шину питания и шину нулевого потенциала, отличающееся тем, что, с целью повышения быстродействия и уменьшения рассеиваемой мощности, устройство содержит дополнительную управляющую шину,.а жаждая ячейка памяти - дополяительный вентильный МДП-транзистор и емкостный элемент, причем стоки МДП-транзисторов с изменяемым порогом включения через дополнительные вентильные МДП-транзисторы, затворы которых подключены к управляющей шине, шине питания и одному из электродов емкостного элемента, другой электрод которого нодключен к шине нулевого потенциала. Источники информации, принятые во внимание при экспертизе: 1. Патент США № 3744036, кл. 340-173, 1973. 2. Авт. св. № 458036, G 11 С 11/40, 19.07.73.

r-T---v

/JH

Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегральное запоминающее устройство на мдп транзисторах | 1973 |

|

SU458036A1 |

| Программируемое постоянное за-пОМиНАющЕЕ уСТРОйСТВО | 1978 |

|

SU809378A1 |

| Запоминающее устройство | 1977 |

|

SU720509A1 |

| Накопитель для полупостоянного запоминающего устройства с электрической перезаписью информации | 1973 |

|

SU519760A1 |

| Матричный накопитель и способ управления записью, считыванием и стиранием информации в накопителе | 1987 |

|

SU1596392A1 |

| НАКОПИТЕЛЬ ЭЛЕКТРИЧЕСКИ ПРОГРАММИРУЕМОГО ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1991 |

|

RU2028676C1 |

| Запоминающее устройство | 1985 |

|

SU1269209A1 |

| Устройство для считывания информации из матричного накопителя | 1978 |

|

SU767834A1 |

| Интегральное запоминающее устройство | 1973 |

|

SU479153A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU841047A1 |

Авторы

Даты

1976-07-30—Публикация

1974-10-04—Подача