13325252

Изобретение относится к импульсной ток от источника питания. Кроме того, технике и может быть использовано как закрытые транзисторы 26 и 27 изоли- усилительное устройство, легко реали- руют шину 21 выходного сигнала от

зуемое в интегральном исполнении, в частности может использоваться в качестве усилителя считывания запоминающих устройств.

Цель изобретения - повьшение быст- родействия.

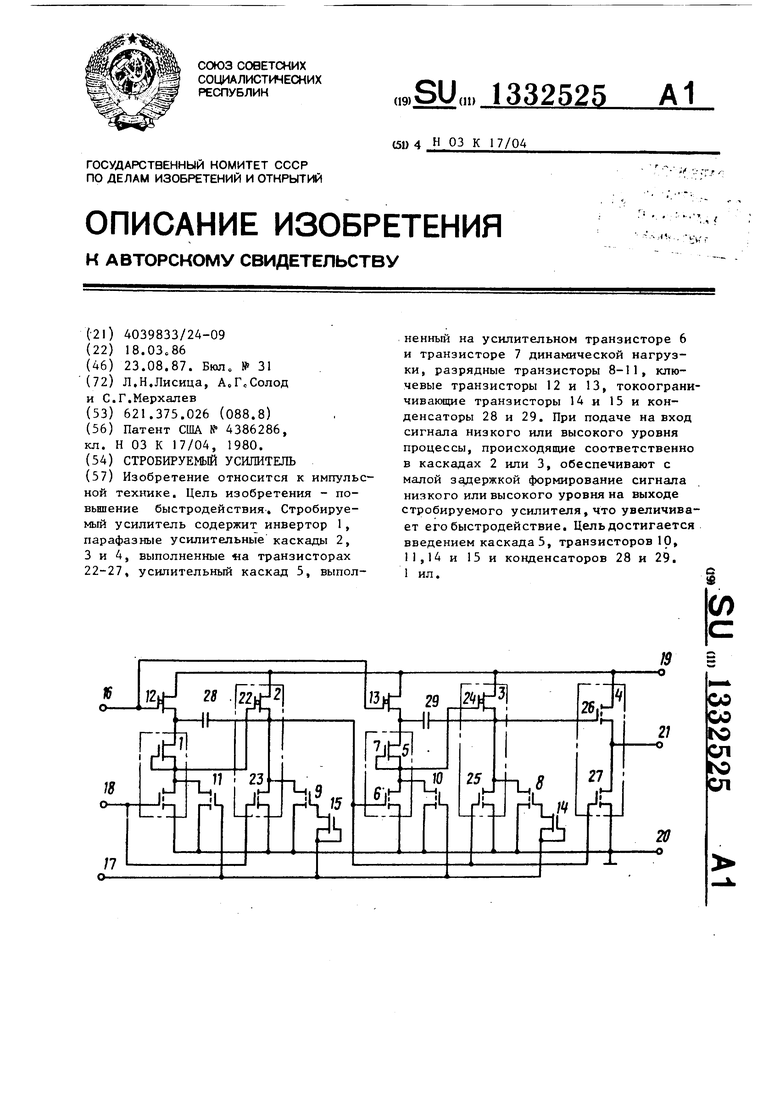

На чертеже представлена принципиальная электрическая схема стробируе- мого усилителя

Стробируемый усилитель содержит входной инвертор 1, первый, второй и третий выходной парафазные усилительные каскады 2-4, усилительный каскад 5, выполненный на усилительном транзисторе 6 и транзисторе 7 динамической нагрузки, первый, второй, тре- 20 конденсаторов 28 и 29 поддерживаеттий и четвертый разрядные.транзисторы 8 - 11, первый и второй ключевые транзисторы 12 и 13, первый и второй токоограничивающие транзисторы 14 и

ся низкий потенциал. Другая обкладка каждого конденсатора заряжается через открытые транзисторы 12 и 13 до потенциала, меньшего, чем потенциал

15, первую и вторую шины 16 и 17 уп- 25 шины 19 источника питания, на величиравления потребляемой мощностью, шину 18 входного сигнала, шины 19 и 20 источника питания, шину 21 выходного сигнала, при этом первый, второй и третий выходной парафазные усилительные каскады 2-4 выполнены на транзисторах 22,23; 24,25 и 26,27 соответственно, первый и второй конденсаторы 28 и 29 о

Стробируемый усилитель работает следующим образом.

В режиме уменьшения потребляемой мощности на второй щине 17 устанавливается высокий потенциал, который открывает транзисторы 8 - 11, а на первой шине 16 устанавливается противофазный сигнал, т.е. низкий потенциал, который закрывает транзисторы 12 и 13. В результате прекращается протекание тока через входной инвертор 1, транзисторы усилительного каскада 5, и на затворах транзисторов 22 и 24 устанавливается низкий потенциал, эти транзисторы закрывану падения напряжения на этих транзисторах.

При подаче на шину 18 входного сигнала сигнала низкого уровня тран- 30 зисторы входного инвертора 1 и 23 (первого парафазного усилительного каскада 2) закрываются и начинается повьш1ение потенциала на выходе входного инвертора 1 и соединенном с 35 ним затворе транзистора 22, который открывается, протекающий через него ток повьаиает потенциал на выходе первого парафазного усилительного каскада 2 и затворе транзистора 27. 40 Это повьш1ение потенциала передается первым конденсатором 28 через транзистор входного интервала 1 на затвор транзистора 22, еще больше увеличивая его потенциал и ускоряя процесс 45 открывания транзистора 22. В самом начале этого процесса первый ключевой транзистор 12 закрывается высо- КИМ потенциалом на его истоке, способствуя сохранению заряда на пер- ются, прекращая прямое протекание то- 50 ° конденсаторе 28. В результате ка через первый и второй парафазные потенциал затвора транзистора 22 превышает потенциал шины 19 питания на величину напряжения предварительного заряда первого конденсатора 28, соп- 55 ротивление транзистора 22 резко уменьшается, через него протекает большой ток заряда входной емкости транзисторов 25,27 и 6, который обеспечивает малое время задержки их включениями

усилительные каскады, потенциалы их выходов понижаются, что приводит к закрыванию транзисторов 26 и 27, т.е. прекращению протекания тока через третий выходной парафазный усилительный каскад 4. Таким образом, в режиме уменьшения потребляемой мощности Стробируемый усилитель не потребляет

шины 19 источника питания и общей шины 20, позволяя объединять выходы нескольких усилителей по схеме ПРОВОДНОЕ ИЛИ, что расширяет функциональные возможности усилителя.

При смене фаз сигнала управления мощностью, на первой шине 16 устанавливается высокий потенциал, открывающий транзисторы 12 и 13, низким потенциалом на второй шине 17 транзисторы 8-11 закрываются. Токоограни- чивающие транзисторы 14 и 15 замедляют процесс закрывания транзисторов 8 и 9, в результате чего на их стоках и присоединенных к ним обкладках

ся низкий потенциал. Другая обкладка каждого конденсатора заряжается через открытые транзисторы 12 и 13 до потенциала, меньшего, чем потенциал

шины 19 источника питания, на величину падения напряжения на этих транзисторах.

При подаче на шину 18 входного сигнала сигнала низкого уровня тран 30 зисторы входного инвертора 1 и 23 (первого парафазного усилительного каскада 2) закрываются и начинается повьш1ение потенциала на выходе входного инвертора 1 и соединенном с 35 ним затворе транзистора 22, который открывается, протекающий через него ток повьаиает потенциал на выходе первого парафазного усилительного каскада 2 и затворе транзистора 27. 40 Это повьш1ение потенциала передается первым конденсатором 28 через транзистор входного интервала 1 на затво транзистора 22, еще больше увеличивая его потенциал и ускоряя процесс 45 открывания транзистора 22. В самом начале этого процесса первый ключевой транзистор 12 закрывается высо- КИМ потенциалом на его истоке, спо3133252

формирования выходного сигнала на шине 21 выходного сигнала, т,во высокое быстродействие устройства. Открывание транзисторов 6 и 25 формирует низкие потенциалы на затворе транзистора 2А , выходе второго парафазного усилительного каскада 3 и соединенном с ним затворе транзистора 26, закрывание последнего способствует ю формированию выходного сигнала низкого уровня, синфазного входному сигналу.

При подаче на шину 18 входного сигнала сигнала высокого уровня 15 описанные выше процессы происходят во втором парафазном усилительном каскаде 3, обеспечивая повьшение потенрого соединен с неинвертирующим входом третьего выходного папафазно- го усилительного каскада и через первый разрядный транзистор - с общей шиной, инвертируюпщй вход третьего выходного парафазного усилительного каскада соединен с выходом первого парафазного усилительного каскада и через второй разрядный транзистор- с общей шиной, а также первый и второй ключевые транзисторы, стоки которых соединены с соответствующей шиной источника питания, а затворы - с первой шиной сигнала управления потребляемой мощностью, отлича ющийся тем, что, с целью увели чения быстродействия, введены усилительный каскад, выполненный на посциала на затворе и открывание транзистора 26 большим током, протекающим 20 ледовательно соединенных относитель- через транзистор 24, эффективно отк- но источника питания усилительном рытый высоким потенциалом на его затворе. При этом с малой задержкой на выходе усилителя формируется сигнал высокого уровня о

За счет этого увеличивается быстротранзисторе и транзисторе динамической нагрузки, третий и четвертый раз рядные транзисторы, первый и второй 25 конденсаторы, первый и второй токо- ограничивающие транзисторы, при этом

действие усилителя: увеличиваются вход усилительного каскада и инвер- амплитуды и уменьшаются фронты вход- тирующий вход второго парафазного ных и выходных сигналов парафазных усилительного каскада соединены с усилительных каскадов. Введение ключе-30 выходом первого парафазного усилитель вых транзисторов не в парафазные кас- ного каскада, выход усилительного кады, а в цепи управления ими совместно с дополнительными разрядными и токоограничивающими транзисторами обеспечивает эффективное управление

35

каскада соединен с неинвертирующим входом второго парафазного усилительного каскада и через третий разрядный транзистор - с общей шиной, исток первого ключевого транзистора соединен с соответствующим выводом питания входного инве этора и через первый конденсатор - с выходом перпотребляемой мощностью, устранив его негативное влияние на быстродействие предлагаемого усилителя, характерно для известного

Увеличение быстродействия расширяет сферу применения предлагаемого усилителя и повьш1ает технические характеристики аппаратуры, в которой он используется.

Формула изобретения Стробируемый усилитель, выполненный на полевых транзисторах, содержа- 50 затворами третьего и четвертого щий входной инвертор, вход и выход которого соединены с инвертирующим входом и неинвертирующим входом первого парафазного усилительного каскада соответственно, второй парафаз- ный усилительный каскад, выход которазрядных транзисторов и через первый токоограничиваюрдий транзистор - с затвором первого разрядного транзистора, а через второй токоограничива- 55 ющий транзистор - с затвором второго разрядного транзистора.

ВНИИПИ

Здказ 38А8/55

Произв.-полигр. пр-тие, г. Ужгород, ул. Проектная, 4

рого соединен с неинвертирующим входом третьего выходного папафазно- го усилительного каскада и через первый разрядный транзистор - с обще шиной, инвертируюпщй вход третьего выходного парафазного усилительного каскада соединен с выходом первого парафазного усилительного каскада и через второй разрядный транзистор- с общей шиной, а также первый и второй ключевые транзисторы, стоки которых соединены с соответствующей шиной источника питания, а затворы - с первой шиной сигнала управления потребляемой мощностью, отличающийся тем, что, с целью увеличения быстродействия, введены усилительный каскад, выполненный на последовательно соединенных относитель- но источника питания усилительном

0 ледовательно соединенных относитель- но источника питания усилительном

транзисторе и транзисторе динамической нагрузки, третий и четвертый раз-; рядные транзисторы, первый и второй 25 конденсаторы, первый и второй токо- ограничивающие транзисторы, при этом

вход усилительного каскада и инвер- тирующий вход второго парафазного усилительного каскада соединены с выходом первого парафазного усилитель ного каскада, выход усилительного

каскада соединен с неинвертирующим входом второго парафазного усилительного каскада и через третий разрядный транзистор - с общей шиной, исток первого ключевого транзистора соединен с соответствующим выводом питания входного инве этора и через первый конденсатор - с выходом первого парафазного усилительного каскада, исток второго ключевого транзистора соединен со стоком транзистора- динамической нагрузки усилительного каскада и через второй конденсатор с выходом второго парафазного усилительного касакада, выход инвертора через четвертый разрядный транзистор соединен с общей шиной, вторая шина сигнала управления мощности соедине50 затворами третьего и четвертого

разрядных транзисторов и через первый токоограничиваюрдий транзистор - с затвором первого разрядного транзистора, а через второй токоограничива- 55 ющий транзистор - с затвором второго разрядного транзистора.

Тираж 901

Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Усилитель-формирователь выходных сигналов постоянных запоминающих устройств на МОП-Транзисторах | 1983 |

|

SU1140245A1 |

| Усилитель-формирователь | 1982 |

|

SU1065883A1 |

| Выходной усилитель | 1981 |

|

SU1015436A1 |

| Усилитель считывания | 1981 |

|

SU970461A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Усилитель-формирователь импульсов | 1980 |

|

SU944110A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU841047A1 |

| Формирователь выходного сигнала на МДП-транзисторах | 1986 |

|

SU1338055A1 |

| Элемент памяти для регистра сдвига | 1978 |

|

SU706880A1 |

| Формирователь импульсов на МОП-транзисторах | 1984 |

|

SU1236604A1 |

Изобретение относится к импульсной технике. Цель изобретения - по- вьнпение быстродействия, Стробируе- мый усилитель содержит инвертор 1, парафазные усилительные каскады 2, 3 и 4, выполненные «а транзисторах 22-27, усилительный каскад 5, выполненный на усилительном транзисторе 6 и транзисторе 7 динамической нагрузки, разрядные транзисторы 8-11, ключевые транзисторы 12 и 13, токоограни- чивающие транзисторы 14 и 15 и конденсаторы 28 и 29. При подаче на вход сигнала низкого или высокого уровня процессы, происходящие соответственно в каскадах 2 или 3, обеспечивают с малой задержкой формирование сигнала низкого или высокого уровня на выходе стробируемого усилителя, что увеличивает его быстродействие. Цель достигается введением каскада 5, транзисторов 10, 11,14 и 15 и конденсаторов 28 и 29. 1 ил.

| Патент США N 4386286, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-08-23—Публикация

1986-03-18—Подача