i

Изобретение относится к импульсной технике и предназначено для работы в цифровых устройствах на МОП транзисторах в качестве формирователя командных и тактовых импульсов.

Цель изобретения - повьппение быстродействия устройства и уменьшение его входной емкости.

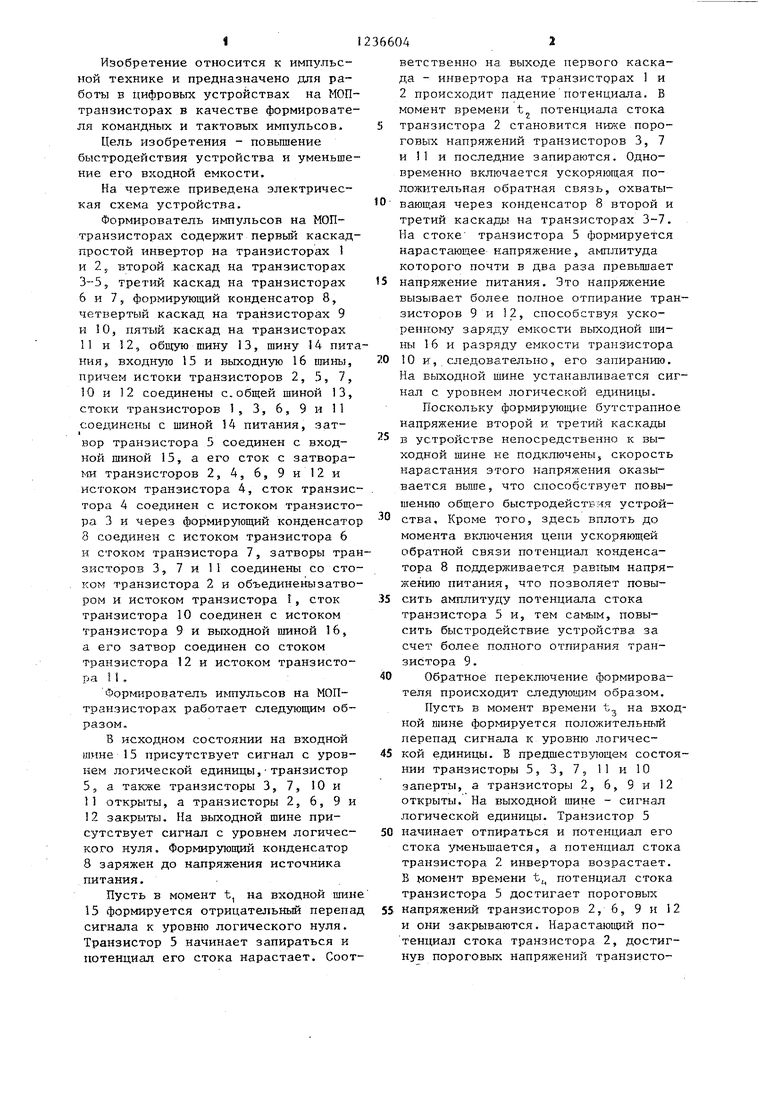

На чертеже приведена электрическая схема устройства.

Формирователь импульсов на МОП- транзисторах содержит первьш каскад простой инвертор на транзисторах 1 и 2 J второй каскад на транзисторах 3-5, третий каскад на транзисторах 6 и 7 формирующий конденсатор 8, четвертый каскад на транзисторах 9 и 10, пятый каскад на транзисторах 11 и 52, общую шину 13, шину 14 питния J, входную 15 и выходную 16 шины, причем истоки транзисторов 2, 5, 7, 10 и 12 соединены с. общей шиной 13, стоки транзисторов 1, 3, 6, 9 и П соединены с шиной 14 питания, затвор транзистора 5 соединен с входной шиной 15, а его сток с затвора- f-ffl транзисторов 2, 4, 6, 9 и 12 и истоком транзистора 4, сток транзистора 4 соединен с истоком транзистора 3 и через формирутощий конденсато 8 соединен с истоком транзистора 6 и стоком транзистора 7, затворы тразисторов 3, 7 и 11 соединены со стоком транзистора 2 и объединенызатвором и истоком транзистора I, сток транзистора 10 соединен с истоком транзистора 9 и выходной шиной 16, а его затвор соединен со стоком транзистора 12 и истоком транзистора 11 .

Формирователь импульсов на МОП- транзисторах работает следующим образом,

В исходном состоянии на входной шине 15 присутствует сигнал с уровнем логической единицы,транзистор 5,, а также транзисторы 3, 7, 10 и 11 открыты, а транзисторы 2, 6, 9 и 2 закрыты. На выходной шине присутствует сигнал с уровнем логического нуля. Формирующий конденсатор 8 заряжен до напряжения источника питания.

Пусть в момент t, на входной шин 15 формируется отрицательньм перепа сигнала к уровню логического нуля. Транзистор 5 начинает запираться и потенциал его стока нарастает. Соот

5

0

5

ветственно на выходе первого каскада инвертора на транзисторах 1 и 2 происходит падение потенциала. В момент времени t потенциала стока транзистора 2 становится ниже поро- говытс напряжений транзисторов 3, 7 и 11 и последние запираются. Одновременно включается ускоряющая положительная обратная связь, охватывающая через конденсатор 8 второй и третий каскад на транзисторах 3-7. На стоке транзистора 5 формируется нарастгиощее напряжение, амплитуда которого почти в два раза превьшает напряжение питания. Это напряжение вызывает более полное отпирание транзисторов 9 и 12, способствуя ускоренном заряду емкости выходной шины 16 и разряду емкости транзистора 10 и, следовательно, его запиранию. На выходной шине устанавливается сигнал с уровнем логической единицы.

Поскольку фopмиpyюш гe бутстрапное напряжение второй и третий каскады в устройстве непосредственно к выходной шине не подключены, скорость нарастания этого напряжения оказывается вьппе, что способствует повы- шен1-по общего быстродействия устройства. Кроме того, здесь вплоть до мом€шта включения цепи ускоряющей обратной связи потенциал конденсатора 8 поддерживается равным напряжению питания, что позволяет повысить амплитуду потенциала стока транзистора 5 и, тем самым, повысить быстродействие устройства за счет более полного отпирания транзистора 9.

Обратное переключение формирова- тел5 происходит след ующим образом.

Пусть в момент времени t на входной шине формируется положительный перепад сигнала к уровню логической единицы. В предшествующем состоянии транзисторы 5, 3, 7, 11 и 10 заперты, а транзисторы 2, 6, 9 и 12 открыты. На выходной шине - сигнал логической единицы. Транзистор 5 начинает отпираться и потенциал его стока уменьшается, а потенциал стока транзистора 2 инвертора возрастает. В момент времени t потенциал стока транзистора 5 достигает пороговых 55 напряжений транзисторов 2, 6, 9 и 12 и они закрываются. Нарастающий потенциал стока транзистора 2, достигнув пороговых напряжений транзисто0

5

0

5

50

3

ров 3, 7 и П, вызывает отпирание последних. Начинается процесс заряда емкости затвора выходного транзистора 10 через транзистор II. Тран зистор 10 открывается и разряжает емкость выходной шины 16, устанавливая на ней сигнал с уровнем логического нуля.

Повышение быстродействия переключения формирователя в состояние логического нуля на выходе происходит по двум причинам: заряд ёмкости затвора выходного транзистора 10 происходит через отдельный транзистор 1I, размеры которого могут обеспечить больший зарядный ток, и введение развязывающего пятого каскада между первым каскадом и инвертором и треть им (выходным) каскадом позволяет повысить скорость нарастания потенциа ла стока транзистора 2, а следовательно, ускорить процессы отпирания транзистора П и, в конечном итоге, транзистора 10.

Что касается уменьшения входной емкости формирования, то она обеспечивается за счет более полной развязки входной и выходной шин.

По сравнению с известным предлагаемое изобретение обладает при равных токах потребления и емкостях нагрузки в 1,5 раза большим быстродействием и меньше нагрзгжает источник входного сигнала.

Ф о рмула изобрет е н и я

Формирователь импульсов на МОП- транзисторах ,содержащий первый каскад - простой инвертор, включенньй между шиной питания и общей шиной, второй каскад на трех соединенных

-

Редактор Е. Папп

Составитель С. Агеев Техред Н.ГГоповкч

Заказ 3098/58Тираж 816-Подписное

БНИРШИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

-10

15

20

2366044

последовательно по току транзисторах, у которых сток первого соединен с шиной питания, его затвор - со стоком ключевого транзистора пер- 5 вого каскада, затвор которого соединен с затвором второго транзистора, а исток третьего - с общей шиной, третий каскад на двух соединенных последовательно по току транзисторах, у которых сток первого соединен с шиной питания, его затвор - с истоком второго транзистора второго каскада, сток которого через формирующий .конденсатор соединен с истоком этого транзистора, исток второго соединен с общей шиной, а его затвор - со стоком ключевого транзистора первого каскада, и четвер- тьп каскад на транзисторе, сток которого соединен с шиной питания, исток - с выходной шиной, а затвор - с затвором второго транзистора второго каскада, отличающий- с я тем, что, с целью повьш ения

25 .быстродействия и уменьшения входной емкости, в него введены второй транзистор в четвертый каскад, у которого исток соединен с общей шиной, а сток - с выходной шиной, и пятьш

30 каскад на двух соединенных последовательно по току транзисторах, у ко- торых сток первого соединен с шиной питания, его затвор - со стоком ключевого транзистора первого каскада, исток второго - с общей шиной, его затвор - со стоком третьего транзистора второго каскада, а сток - с затвором второго транзистора четвертого каскада, причем затвор третьего

40 транзистора второго каскада соединен с входной шиной., а его сток - с затвором второго транзистора того же каскада.

35

Корректор Л. Пилипенко

| название | год | авторы | номер документа |

|---|---|---|---|

| Усилитель-формирователь на МОП-транзисторах | 1984 |

|

SU1221740A1 |

| Усилитель-формирователь выходных сигналов постоянных запоминающих устройств на МОП-Транзисторах | 1983 |

|

SU1140245A1 |

| Устройство для выборки адресов из блоков памяти | 1976 |

|

SU744722A1 |

| Усилитель-формирователь | 1982 |

|

SU1065883A1 |

| ЛОГИЧЕСКОЕ КОНВЕЙЕРНОЕ УСТРОЙСТВО | 2000 |

|

RU2175811C1 |

| Формирователь парафазных импульсов | 1981 |

|

SU984013A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU841047A1 |

| Стробируемый усилитель | 1986 |

|

SU1332525A1 |

| ВЫХОДНОЙ ФОРМИРОВАТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ С УСТРОЙСТВОМ ЗАЩИТЫ ОТ ЭЛЕКТРОСТАТИЧЕСКИХ РАЗРЯДОВ ДЛЯ КМОП МИКРОСХЕМ | 2013 |

|

RU2540813C1 |

| Формирователь импульсов на МОП-транзисторах | 1988 |

|

SU1653142A1 |

Изобретение относится к импульсной технике и может быть использовано в цифровых устройствах на МОП- транзисторах в качестве формирователя командных и тактовых импульсов. Целью изобретения является повьшение быстродействия формирователя и уменьшение его входной емкости,- Для достижения цели в формирователь введены второй транзистор 10 в четвертый каскад и пятый каскад на транзисторах 11 и 12, Формирователь содержит также первьй каскад на транзисторах 1 и 2, второй каскад на транзисторах 3, 4 и 5, третий каскад на транзисторах 6 и 7, формирующий конденсатор В, четвертьй на транзисторах 9 и 10 шины: общуто 13, питания 14, входную 15 и выходную 16. По сравнению с базовым объектом предложенный формирователь обладает при равных токах потребления и емкостях нагрузки в 1,5 раза большим быстродействием и меньше нагружает источник входного сигнала. 1 ил. S (Л с: / i//rJ го оо О5 О5

| Авторское свидетельство СССР № 820618, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Electronics, 1981, v | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Сепаратор-центрофуга с периодическим выпуском продуктов | 1922 |

|

SU128A1 |

Авторы

Даты

1986-06-07—Публикация

1984-11-30—Подача