1

Изобретение относится к области вычислительной техники.

Известны устройства для синхронизации вычислительной системы, предполагающие наличие в системе единого генератора тактирующих импульсов.

Однако при использовании известных устройств отсутствует программный переход на синхронную работу распределителей тактовых сигналов процессоров со сдвигом, определяемым рабочей программой системы, и не обеспечивается возможность синхронной работы двух процессоров с совмещением временных диаграмм приема .кода в одном л выдачи кода в другом процессоре, т. е. невозможен межпроцессорный обмен информацией без промежуточного ее запоминания, что требует дополнительного оборудования. Кроме того, известные устройства требуют .много време.ни на вхождение в синхро.низм.

Цель изобретения - сокращение количества оборудования и уменьщение времени вхожде.ния системы в синхронизм.

Цель достигается тем, что в предлагаемое устройство введен блок программного задания сдвига, вход которого соединен с входом устройства, выходы подключены соответствеЕНО к пер.вым входам схем управления, вторые входы -которых соединены с выходами соответствующих распределителей тактовых импульсов, выход каждой схемы управления подключен к входу соответствующего формирователя контрольных сигналов, первый вход каждого фазового дискриминатора подключен к выходу соответствующего формирователя контрольных сигналов, вторые входы фазовых дискриминаторов объединены и подключены к выходу формирователя контрольных сигналов центрального процессора, а выходы через

схемы «И, вторые входы которых соединены с выходом генератора тактирующих импульсов, подключены соответственно к входам распределителей тактовых импульсов.

При этом обеспечивается возможность исключения подачи тактирующих импульсов на входы распределителей всех процессоров системы кроме распределителя процессора, выполняющего функции программного управления синхронизацией в случае, если контрольные сигналы, характеризующие состояния распределителей процессора, .не совпадают во времени с ко.нтроль.ньп1 сигналом центрального (управляющего) процессора. Величина необходимого сдвига одноименных тактов

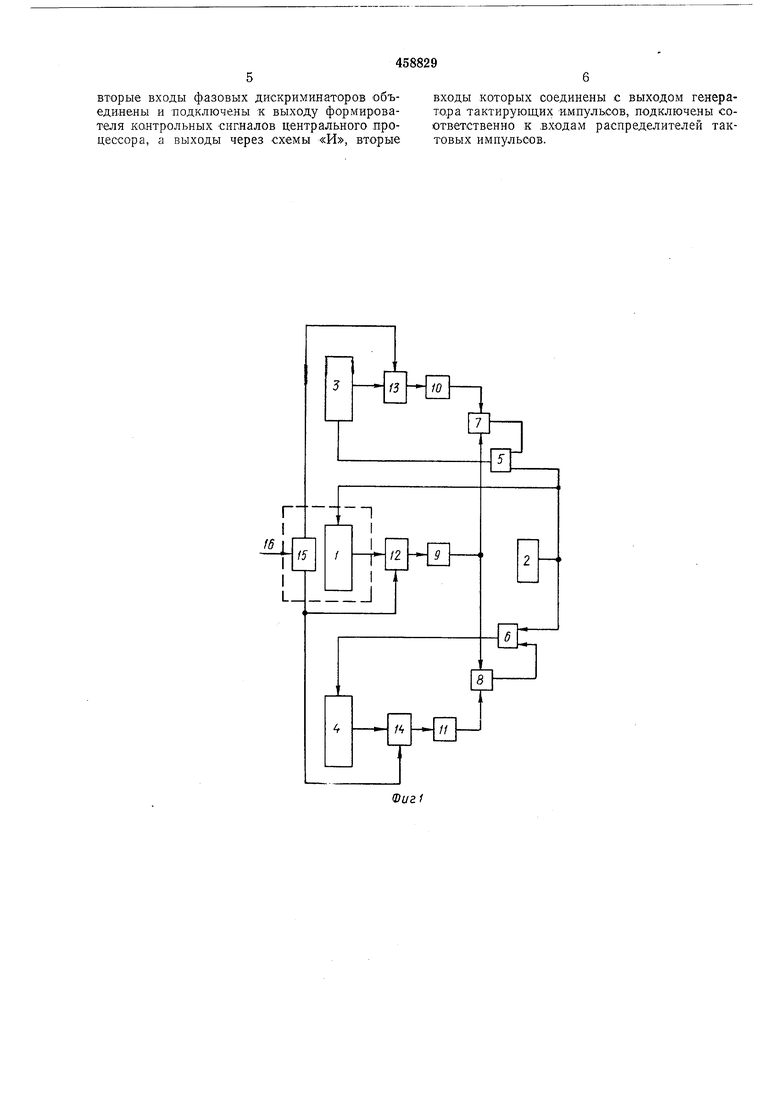

центрального и управляемых процессоров задается блоком программного задания сдвига и схемами управления формирователями контрольных сигналов каждого из процессоров. На фиг. 1 приведена блок-схема предлагаемого устройства; на фиг. 2 - схема управления формирователем контрольного сигнала одного из управляемых процессоров; на ф,иг. 3 - схема фазового дискриминатора.

Предлагаемое устройство содержит распределятель тактовых импульсов 1 центрального (управляющего) процессора; генератор тактовых импульсов 2; распределители тактовых импульсов 3, 4 управляемых процессоров; схемы «И 5, 6; фазовые дискриминаторы 7, 8; ф.ормирователи 9-II контрольных сигналов; схемы управления 12, 13, 14 формирователями 9-11; блок 15 программного задания сдвига; вход 16 устройства.

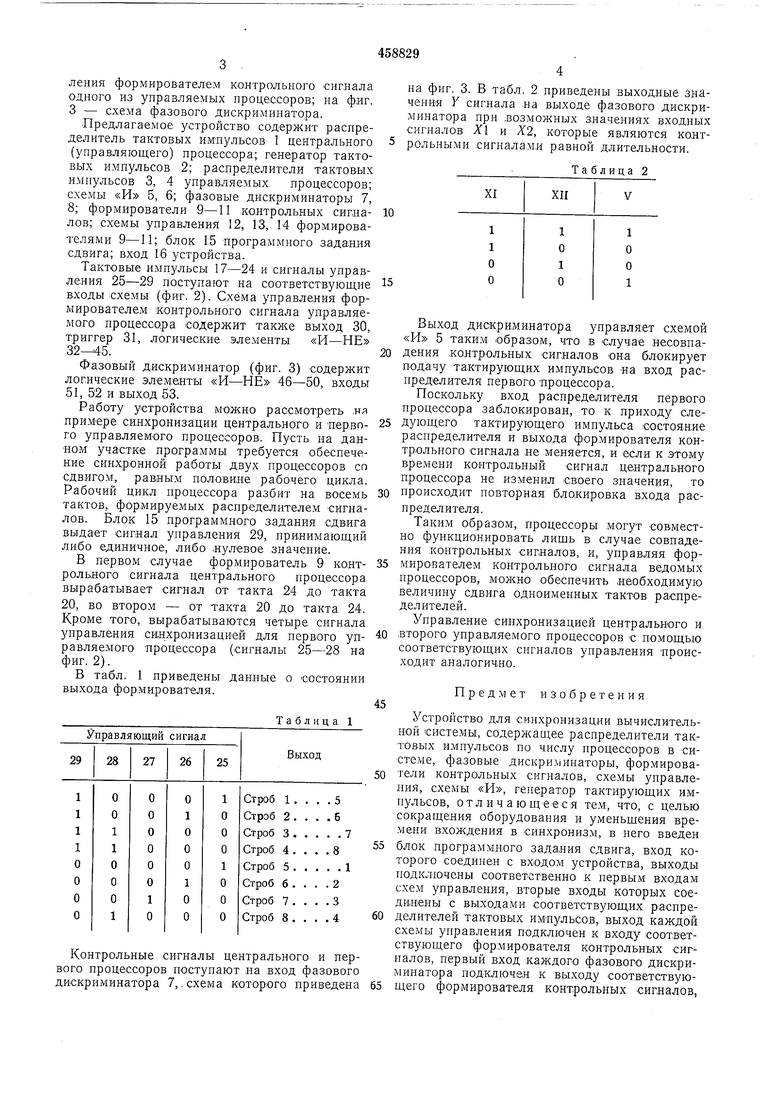

Тактовые импульсы 17-24 и сигналы управления 25-29 поступают на соответствующие входы схемы (фиг. 2). Схема управления формирователем контрольного сигнала управляемого процессора содержит также выход 30, триггер 31, логические элементы «И-НЕ 32-45.

Фазовый дискриминатор (фиг. 3) содержит логические элементы «И-НЕ 46-50, входы 51, 52 и выход 53.

Работу устройства можно рассмотреть ля примере синхронизации центрального и пер.впго управляемого процессоров. Пусть на данном участке программы требуется обеспечение синхронной работы двух процессоров сп сдвигом, равным поло.вине рабочего цикла. Рабочий цикл процессора разбит на восемь тактов, фор.мируемых распределителем сигналов. Блок 15 программного задания сдвига выдает сигнал управления 29, принимающий либо единичное, либо нулевое значение.

В первом случае формирователь 9 контрольного сигнала центрального процессора вырабатывает сигнал от такта 24 до такта 20, во втором - от такта 20 до такта 24. Кроме того, вырабатываются четыре сигнала управления синхролизацисй для первого управляемого Процессора (сигналы 25-28 на фиг. 2).

В табл. 1 приведены данные о состоянии выхода формирователя.

Таблица 1

Управляющий сигнал

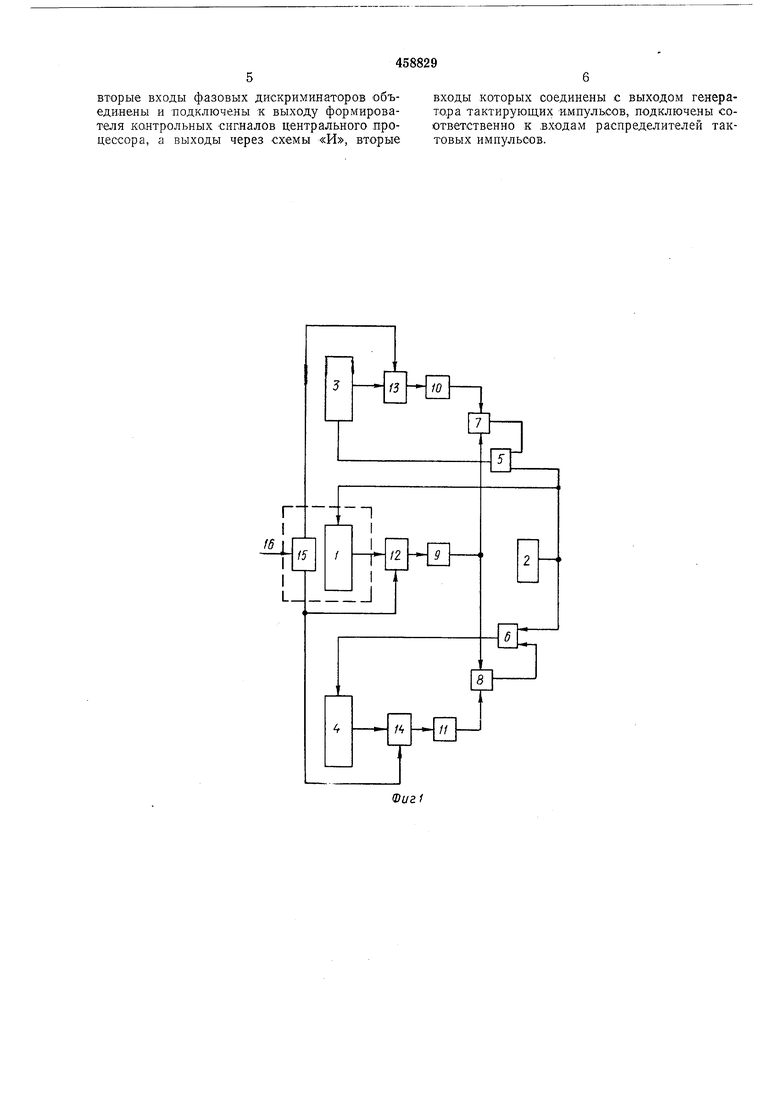

Контрольные сигналы центрального и первого процессоров поступают на вход фазового дискриминатора 7,.схема которого приведена

на фиг. 3. В табл. 2 приведены выходные значенИЯ F сигнала на выходе фазов ого дискриминатора при .возможных значениях входных сигналов XI и Х2, которые являются контрольными сигналами равной длительности.

Таблица 2

Выход дискриминатора управляет схемой «И 5 таким образом, что в случае несовпадения контрольных сигналов она блокирует подачу тактирующих импульсов на вход распределителя первого процессора.

Поскольку вход распределителя первого процессора заблокирован, то к приходу следующего тактирующего импульса состояние распределителя и выхода формирователя контрольного сигнала не меняется, и если к этому времени контрольный сигнал центрального пр:0цессора не изменил своего значения, то

происходит повторная блокировка входа распределителя.

Таким образом, процессоры .могут совместно функционировать лишь в случае совпадения контрольных сигналов, и, управляя формирователем контрольного сигнала ведомых процессоров, можно обеспечить необходимую величину сдвига одноименных тактов распределителей. Управление синхронизацией центрального и

второго управляемого процессоров с помощью соответствующих сигналов управления пронсходит аналогично.

Предмет изобретения

Устройство для синхронизации вычислительной системы, содержащее распределители тактовых импульсов по числу процессоров в системе, фазовые дискри.минаторы, формирователи контрольных сигналов, схемы управления, схемы «И, генератор тактирующих импульсов, отличающееся тем, что, с целью сокращения оборудования и уменьшения времени вхождения в синхронизм, в него введен

блок программного задания сдвига, вход которого соединен с входом устройства, выходы подключены соответственно к первым входам схем управления, вторые входы которых соединены с выходами соответствующих распределителей тактовых импульсов, выход каждой схемы управления подключен к входу соответствующего формирователя контрольных сигналов, первый вход каждого фазового дискриминатора подключен к выходу соответствующего формирователя контрольных сигналов,

вторые входы фазовых дискриминаторов объединены и подключены к выходу формирователя контрольных Сигналов центрального процессора, а выходы через схемы «И, вторые

входы которых соединены с выходом генератора тактирующих импульсов, подключены соответственно к .входам распределителей тактовых импульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации | 1978 |

|

SU943737A1 |

| Устройство для сопряжения цифровой вычислительной машины с каналом связи | 1991 |

|

SU1837301A1 |

| Устройство для синхронизации вычислительной системы | 1980 |

|

SU940148A1 |

| Устройство синхронизации в одночастотных многоканальных адресных системах с временным разделением каналов | 1989 |

|

SU1811018A1 |

| Устройство для синхронизации вычис-лиТЕльНОй СиСТЕМы | 1978 |

|

SU809132A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Цифровое устройство фазовой синхронизации | 1984 |

|

SU1225034A1 |

| Устройство тактовой синхронизации | 1989 |

|

SU1720162A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2020565C1 |

25 17

fa

n

Ii

/,

fS

ru

Л/

45

f 53

fO

4

Авторы

Даты

1975-01-30—Публикация

1973-04-09—Подача