(54) УСТРОЙСТВО ДЛЯ СИНХРОНЮАНИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Телемеханическая система | 1983 |

|

SU1211783A1 |

| Вычислительная система "Антикон" для предотвращения столкновения судов | 1983 |

|

SU1136178A1 |

| Устройство для контроля памяти | 1983 |

|

SU1280459A1 |

| Устройство для вывода информации | 1983 |

|

SU1137475A1 |

| Устройство цикловой синхронизации | 1980 |

|

SU924892A1 |

| Устройство для централизованного управления вычислительной системой | 1985 |

|

SU1259261A1 |

| Устройство для контроля электронных устройств | 1984 |

|

SU1231505A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Устройство для цикловой синхронизации | 1981 |

|

SU1107317A1 |

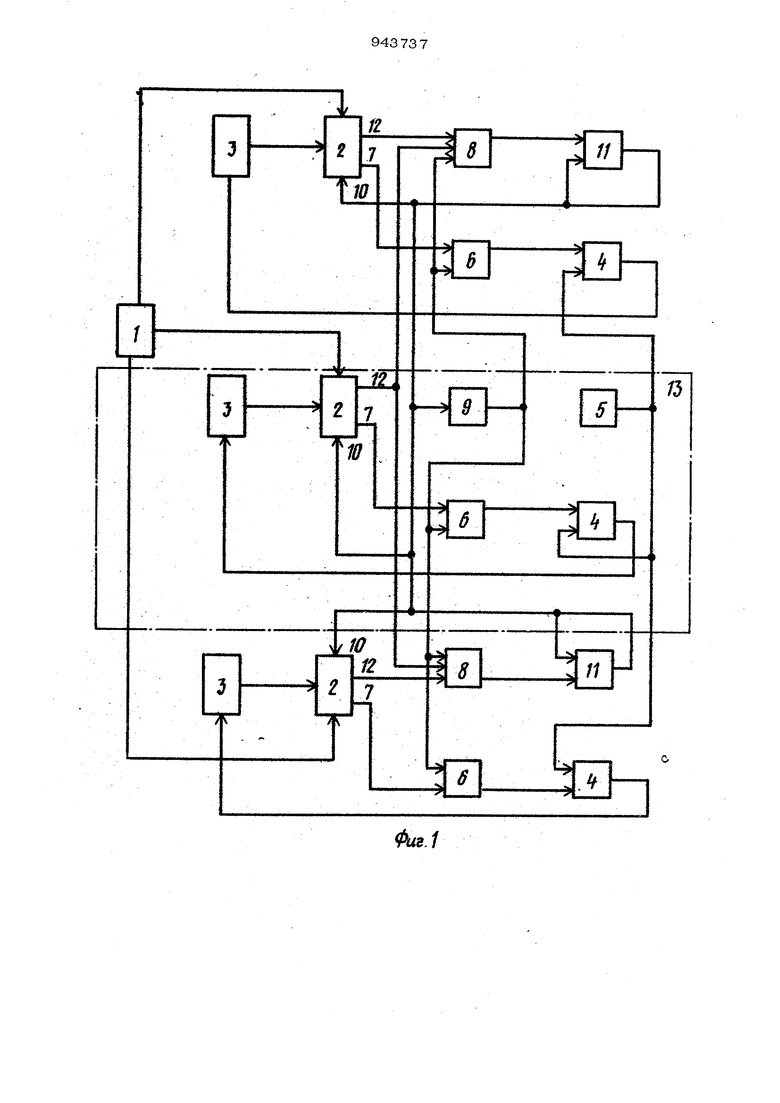

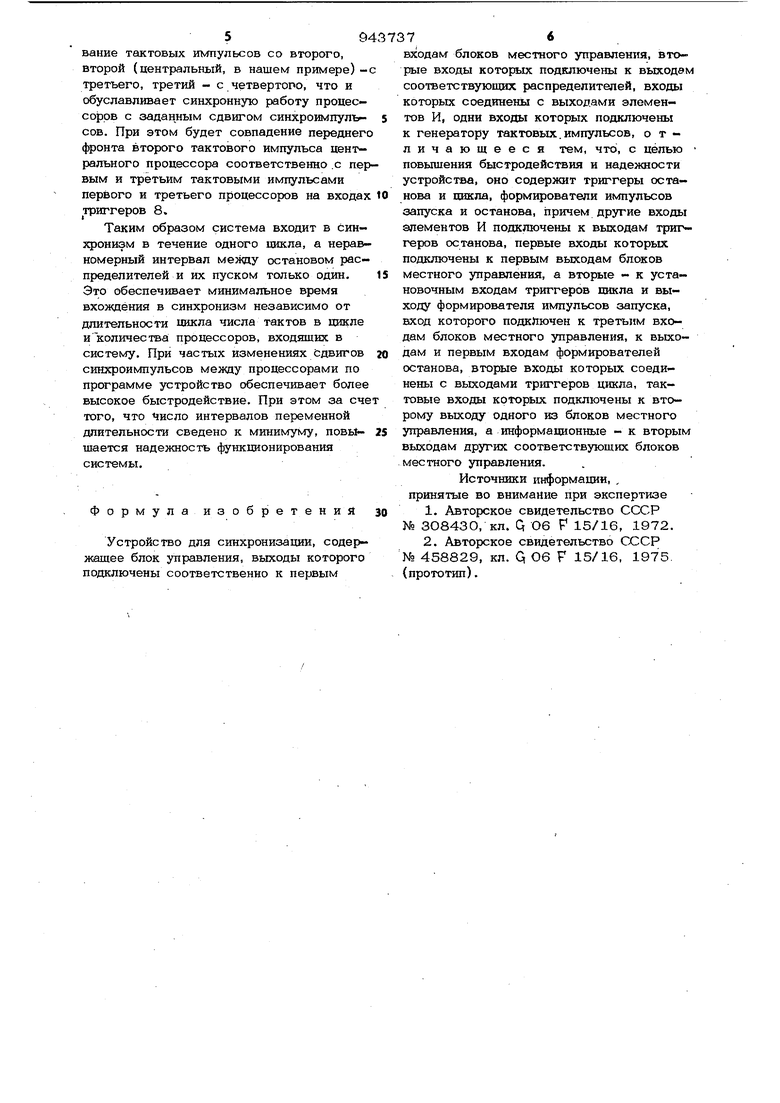

Изобретение относится к вычиспителЕ ной технике и может б5,1ть использовано при проектировании многопроцессорных систем. Известно устройство синхронизации вычислительных систем, обеспечивающее синхронную работу процессоров с постоян ным Взаимным расположением синхросигналов Г . Однако это устройство отличается недостаточной гибкостью, так как в многопроцессорных системах желательно иметь возможность по программе менять взаимное расположение синхросигналов. Наиболее близким к данному изобретению является устройство, отличающееся наличием одного генератора тактирующих импульсов и блока программного задания сдвига синхроимпульсов различных процессоров, входящих в систему 2 . Однако это устройство имеет большое время вхождения в синхронизм (несколь ко Циклов), увеличивающееся с ростом числа тактов, на которые разбит рабочий цикл. Кроме того, во время вхождения в синхронизм образуются переменные интервалы между соседними тактами в процессорах, что может привести к сбою при обмене информацией между ними в данный момент, так как таких переменных интервалов много. Целью изобретения является повышение быстродействия и надежности устройства. Цель достигается тем, что ввод в синхронизм производится путем останова устройства после формирования соответствук щих тактовых импульсов, определяемых блоком управления, в каждом процессоре с последукяцим одновременным запуском, в устройство для синхронизации, содержащее блок управления, выходы которого подключены соответственно к первым вхо-. дам блоков местного управления, вторые входы которых подключены к выходам соответствующих распределителей, входы которых соединены с выходами элементов И, одни входы которых подключены к выходу генератора тактовых импульсов. .введены триггеры останова и триггер щжпа, формирователи импульсов запуска и останова, причем другие входы элементов И подключены к выходам триггеров останова, первые входы которых подклк чены к первым выходам блоков местного управления, а вторые - к единичным входам триггера шжла и выходу формирователя импульсов запуска, вход которого подключен.: к третьим входам блоков местного управления, к выходу и первым входам формирователей останова, вторые входы триггеров останова соединены с вы ходами триггера цикла, тактовые входы триггеров останова подключены ко второму входу второго блока местного управления, а информационные - ко вторым выходам первого и третьего блоков мест ного управления. На фиг. 1 приведена блок-схема устройства; на фиг. 2 - блок-схема блока местного управления. Работа устройства поясняется на примере системы, состоящей из 3-х процессоров с восьмитактной синхронизацией соответственно. Устройство содержит блок управления 1, выходы которого подключены к первым входам блоков местного управления 2, расположенных в каждом процессоре. Вто рые входы блоков 2 соединены с выходами распределителей 3, входы которых соединены с выходами схем 4 (элементы и). Первые входы схем 4 объединены и подключены к генератору тактовых импульсов 5, а другие входы подключены к выходам триггеров останова 6. Перюые входы триггеров останова б подключены к выходам 7 блоков местного управлешш 2, а вторые объединены между собой и установочными входами триггеров цикЛ 8 и подключены к выходу формирователя запуска 9, вход которого подключен к объединённым между собой третьим входам 1О блоков 2, выходам и первым вхо дам формирователей останова 11. Другие входы формирователей останова 11 подключены к выходам триггеров 8, тактовые входы которых объединены и подключены к выходу 12 блока местного управления 2 центрального процессора 13, а информационные входы подключены к выходам 12 блоков 2 своих процессоров. На блок местного управления 2 (см. фиг. 2) поступа от тактовые импульсы 14 - 21 от распределителя и управляющие сигналы 22 - 29. Блок местного управления состоит из восьми ,элементов 30 И - по числу тактовых импульсов в одном рабочем цикле, элемента 31 1-1ЛИ и элемента 32 И. Рассмотрим работу системы без сдвига синхроимпульсов в разных, процессорах. Для этого необходимо подать управляющий сигнал на одноименные входы блоков местного управления 2 всех процессоров, например, на входы 29. В этом случае на выход 12 поступает каждый восьмой тактовый импульс. При синхронной работе передний .4ронт импульсов иа тактовых входах триггеров 8 (D-триггера с динамическим управлением, т. е. занесением |по фронту синхросигнала) устанавливается внутри импульсов, поступающих на информационные входы, и на выходах триггеров 8 будет постоянный уровень (например, уровень логической единицы). Триггеры 6 установлены в состояние, при котором импульсы генератора 5 через схемы 4 И поступают на распределители 3. При рассинхронизадии любого процессора с центральным передний фронт сигнала на тактовом входе одного, из триггеров 8 не совпадает с импульсом на информационном входе, триггер 8 переключается и запускает формирователь останова 11, который формирует импульс длительностью рав;ной времени одного рабочего цикла. При совпадении этого импульса с восьмым тактовым импульсом на входах элемента 32 И в каждом процессоре на вькоде 7 формируется импульс, переключающий соответствующий триггер 6, запрещая прохождение импульсов генератора 5 на распределитель 3. Одновременно сигнал с выхода формирователя 11 блокирует по входам формирователи 11 от повторного запуска. Таким образом все распределители останавливаются после выдачи восьмого тактового импу/1ьса. Далее формирователь 11 задним фронтом запускает формирователь 9, устанавливающий триггеры 6 и 8 в исходное состояние. Тем самым разрешается прохождение импульсов генератора 5 на распределители 3, которые начинают формирование импульсов с первого такта. При задании сдвига работа устройства происходит аналогично. Например, если на блоки местного управления 2 раз1Пз1х процессоров подать управляющие сигналы соответственно на 22, 23 и 24 входы, то при рассинхронизации первый процессор остановится после выдачи первого тактового }1мпульса, второй - пЪсле второго, третий - после третьего, и при запуске первый процессор начинает формирование тактовых иктупЕзСов со второго, второй (центральный, в нашем примере) -с третьего, третий - с четвертопо, что и обуславливает синхронную работу процессоров с заданным сдвигом синхроимпулъ- s сов. При этом будет совпадение переднего фронта второго тактового импульса центрального процессора соответственно .с первым и третьим тактовыми импульсами первого и третьего процессоров на входах to триггеров 8.

Таким образом система входит в синзфонизм в течение одного цикла, а неравномерный интервал между остановом распределителей и их пуском только один. 15 Это обеспечивает минимальное время вхождения в синхронизм независимо от длительности дикла числа тактов в цикле и количества процессоров, вход5пиих в систему. При частых изменениях Сдвигов гО синхроимпульсов между процессорами по программе устройство обеспечивает более высокое быстродействие. При этом за счет того, что Число интервалов переменной длительности сведено к минимуму, повы- 2S шается надежность функционирования системы.

ФормулаизобретениЯ зо

Устройство для синхронизации, содержащее блок управления, выходы которого подключены соответственно к первым

входам блоков местного управления, вторые входы которых подключены к выхода соответствующих распределителей, входы которых соединены с выходами элементов И, одни входы которых подключены к генератору тактовых, импульсов, отличающееся тем, что, с целью повышения быстродействия и надежности устройства, оно содержит триггеры останова и цикла, формирователи импульсов запуска и останова, причем другие входы элементов И подключены к выходам триггеров останова, первые входы которых подключены к первым выходам блоков местного управления, а вторые - к установочным входам триггеров цикла и выходу формирователя импульсов запуска, вход которого подключен к третьим входам блоков местного управления, к выходам и первым входам формирователей останова, вторые входы которых соединены с выходами триггеров цикла, тактовые входы которых подключены к второму выходу одного из блоков местного управления, а информационные - к вторым выходам других соответствующих блоков местного управления.

Источники информации, , принятые во внимание при экспертизе

Фиг.2

Авторы

Даты

1982-07-15—Публикация

1978-05-03—Подача