Изобретение относится к области вычислительной техники и предназначено для преобразования двоично-коднровапных чисел из позиционной системы счисления с любым основанием в двоичную систему счисления.

Известны преобразователи кодов, содержащие /5-ичные регистры коэффициентов а, (t О, 1, 2, .. ., п) двоичный регистр, вход которого соединен с выходом младшего разряда р-ичного регистра коэффициента а, и схему управления, первый выход которой подключен к цепям сдвига / -ичных и двоичных регистров. Известные устройства содержат сложные цепи коррекции и требуют больших аппаратурных затрат.

Целью настояш,его изобретения является упрощение устройства при преобразовании двоично-кодированных чисел из позиционной системы счисления с любым основанием в двоичную систему счисления.

Поставленная цель достигается тем, что устройство содержит регистр основания, выходы которого соединены со входами /7-ичных регистров всех коэффициентов я;, кроме коэффициента йп, второй выход схемы управления подключен к цепям выдачи кода регистра основания, выходы младших разрядов каждого р-ичного регистра коэффициента иг подключены к цепям приема кода р-тиого регистра коэффициента .

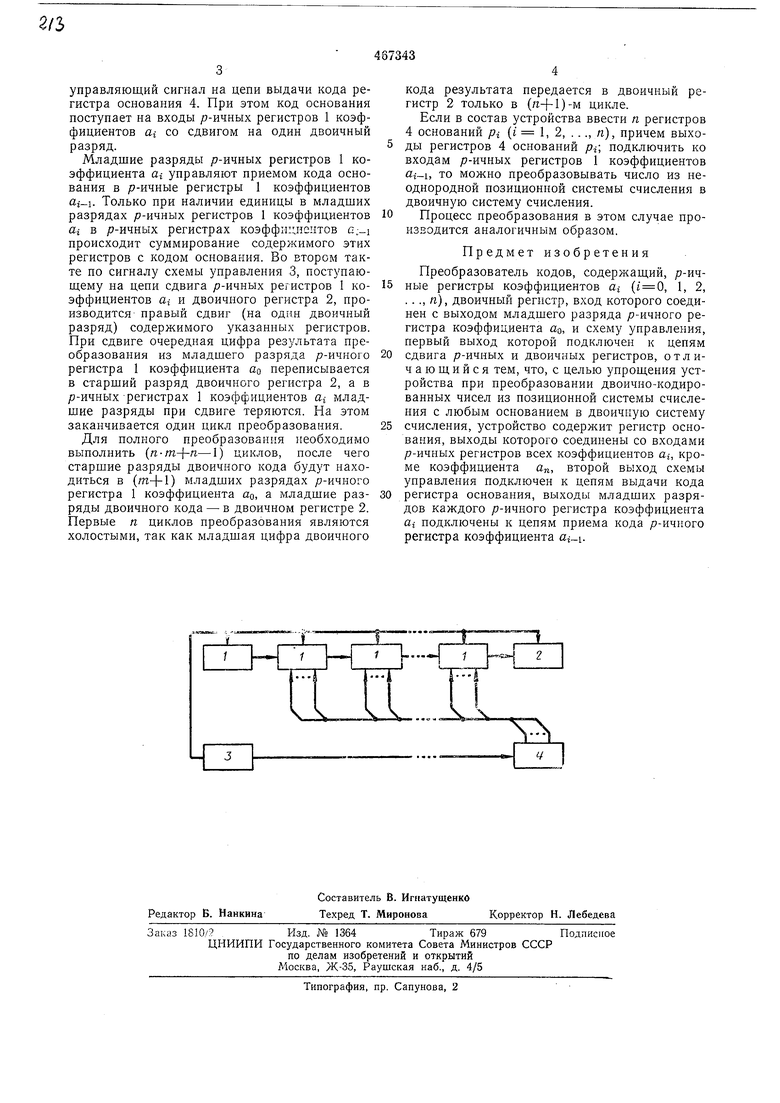

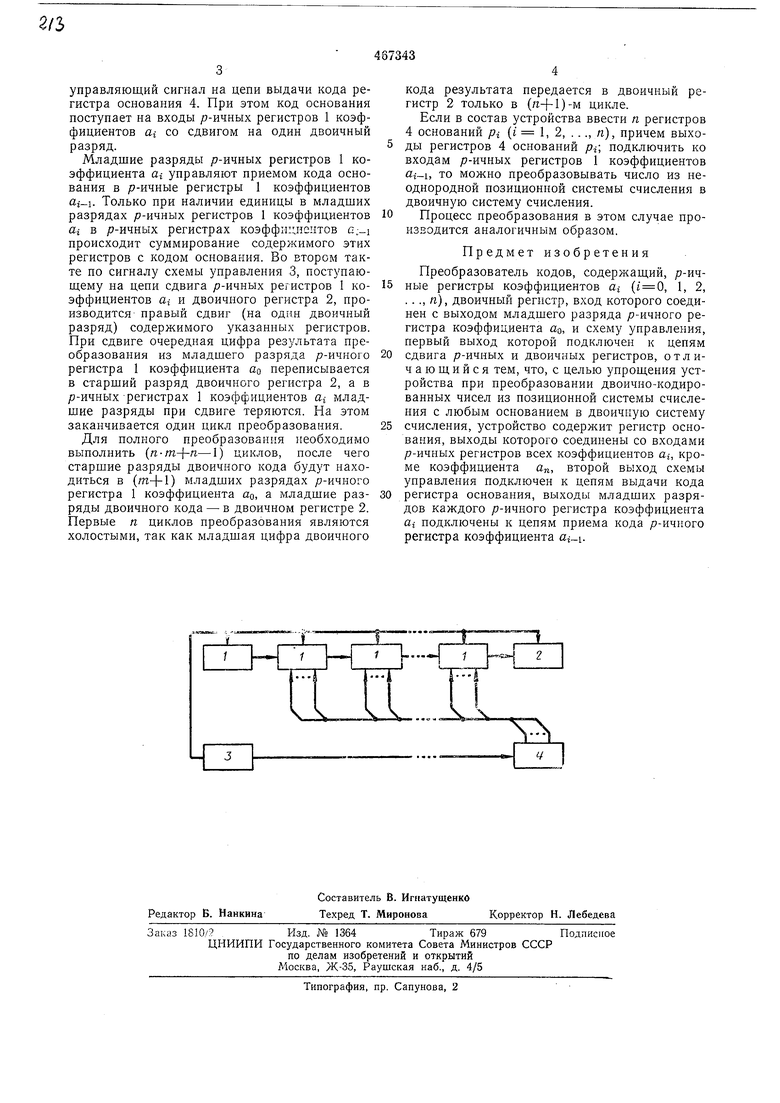

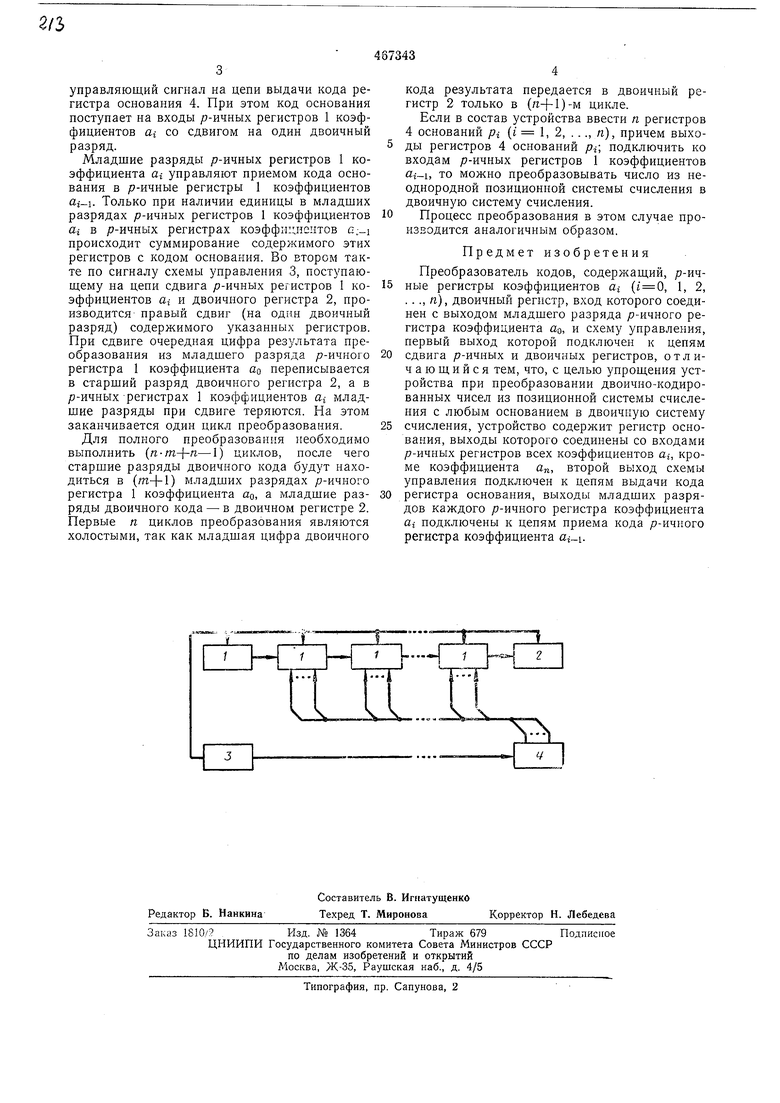

Схема преобразователя кодов приведена на чертеже.

Устройство содержит р-ичные регистры 1 коэффициентов GJ (i О, 1, 2, . . ., /г), двоичный регистр 2, схему управления 3 и регистр основания 4. Регистр 1 коэффициента йп и регистр основания 4 имеют по т двоичных разрядов. Величина m выбирается из соотношения rn logzp, где р - основание системы счисления.

Двоичный регистр 2 имеет (пт-1) разрядов, /5-ичные регистры 1 коэффициентов а, обладают свойством сумматора и имеют по () двоичных разрядов, а регистр 1 коэффициента On-i содержит также дополнительный разряд переполнения.

Устройство работает следующим образом.

Пусть необходимо преобразовать двоичнокодированное число

N а„-р + + ... а,-р + а,-р.

из позиционной системы счисления с основанием р в двоичную систему счисления. В исходном состоянии в регистре основания 4 записан двоичный код основания р, в m старших разрядах р-ичных регистров 1 записаны коды коэффициентов Сг, а двоичный регистр 2 установлен в нулевое состояние. Каждый цикл преобразования состоит из двух тактов.

В первом такте схема управления 3 выдает

управляющий сигнал на цепи выдачи кода регистра основания 4. При этом код основания поступает на входы р-ичных регистров 1 коэффициентов ui со сдвигом на один двоичный разряд.

Младшие разряды /7-ичных регистров 1 коэффициента иг управляют приемом кода основания в р-ичные регистры 1 коэффициентов Сг-ь Только при наличии единицы в младших разрядах /э-ичных регистров 1 коэффициентов ui в р-ичных регистрах коэффициентов происходит суммирование содержимого этих регистров с кодом основания. Во втором такте по сигналу схемы управления 3, поступаюш;ему на цепн сдвига р-ичных регистров 1 коэффициентов иг и двоичного рвгистра 2, производится правый сдвиг (на один двоичный разряд) содержимого указанных регистров. При сдвиге очередная цифра результата преобразования из младшего разряда р-ичного регистра 1 коэффициента Оо переписывается в старший разряд двоичного регистра 2, а в р-ичных -регистрах 1 коэффициентов а, младшие разряды при сдвиге теряются. На этом заканчивается один цикл преобразования.

Для полного преобразования необходимо выполнить (п-т-{-п-I) циклов, после чего старшие разряды двоичного кода будут находиться в (от+1) младших разрядах р-ичного регистра 1 коэффициента ао, а младшие разряды двоичного кода - в двоичном регистре 2. Первые п циклов преобразования являются холостыми, так как младшая цифра двоичного

кода результата передается в двоичный регистр 2 только в ()-M цикле.

Если в состав устройства ввести п регистров 4 оснований pi (i 1, 2, ..., п), причем выходы регистров 4 оснований подключить ко входам р-ичных регистров 1 коэффициентов , то можно преобразовывать число из неоднородной позиционной системы счисления в двоичную систему счисления.

Процесс преобразования в этом случае производится аналогичным образом.

Предмет изобретения

Преобразователь кодов, содержащий, р-ичные регистры коэффициентов а (, 1, 2, .. .,п), двоичный регистр, вход которого соединен с выходом младшего разряда р-ичного регистра коэффициента ао, и схему управления, первый выход которой подключен к цепям сдвига р-ичных и двоичных регистров, отличающийся тем, что, с целью упрощения устройства при преобразовании двоично-кодированных чисел из позиционной системы счисления с любым основанием в двоичную систему счисления, устройство содержит регистр основания, выходы которого соединены со входами р-ичных регистров всех коэффициентов а,, кроме коэффициента а„, второй выход схемы управления подключен к цепям выдачи кода регистра основания, выходы младших разрядов каждого р-ичного регистра коэффициента ui подключены к цепям приема кода р-ичного регистра коэффициента .

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь @ -ичного позиционного кода в двоичный код | 1983 |

|

SU1115045A1 |

| Преобразователь двоичного кода в р-ичный позиционный код | 1983 |

|

SU1163479A1 |

| Устройство для умножения | 1982 |

|

SU1038937A1 |

| Преобразователь позиционного кода в код с большим основанием | 1977 |

|

SU732852A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Устройство для преобразования избыточного двоичного кода в код со смешанным основанием | 1975 |

|

SU618737A1 |

| Устройство для умножения чисел с плавающей запятой | 1985 |

|

SU1280624A1 |

| Преобразователь позиционного кода с одним основанием в позиционный код с другим основанием | 1977 |

|

SU734667A1 |

| Устройство для умножения | 1981 |

|

SU1032453A1 |

| Последовательное множительное устройство | 1985 |

|

SU1307455A1 |

Авторы

Даты

1975-04-15—Публикация

1973-09-27—Подача