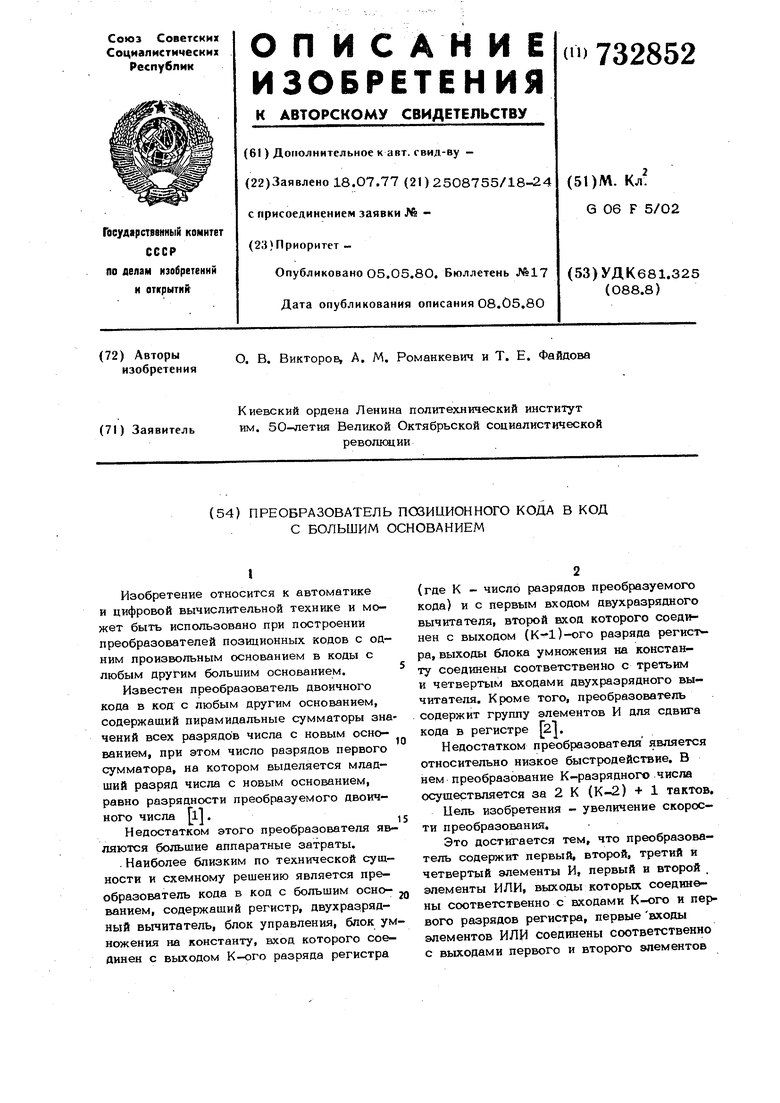

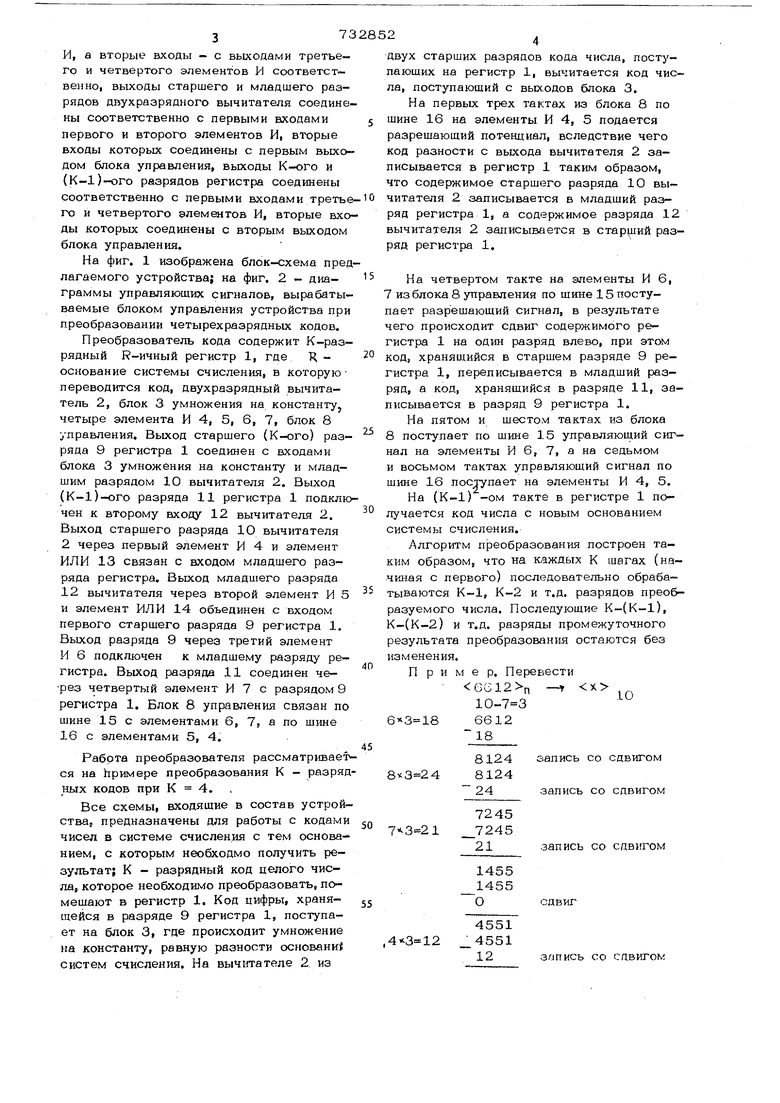

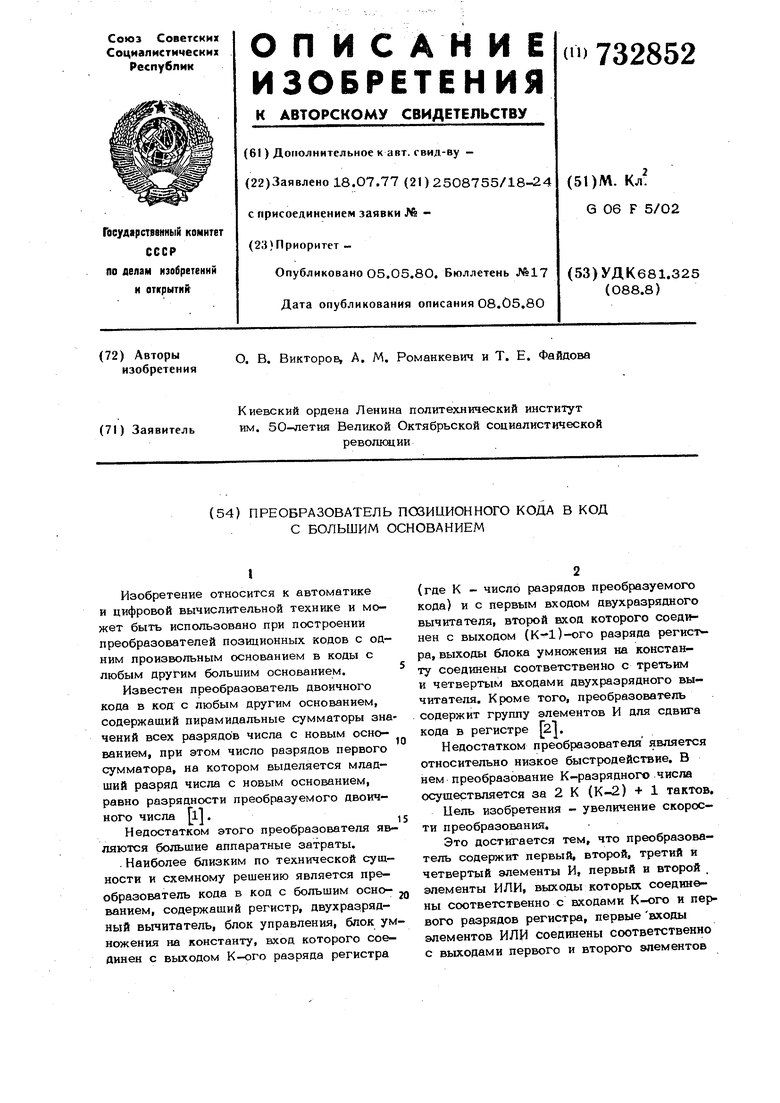

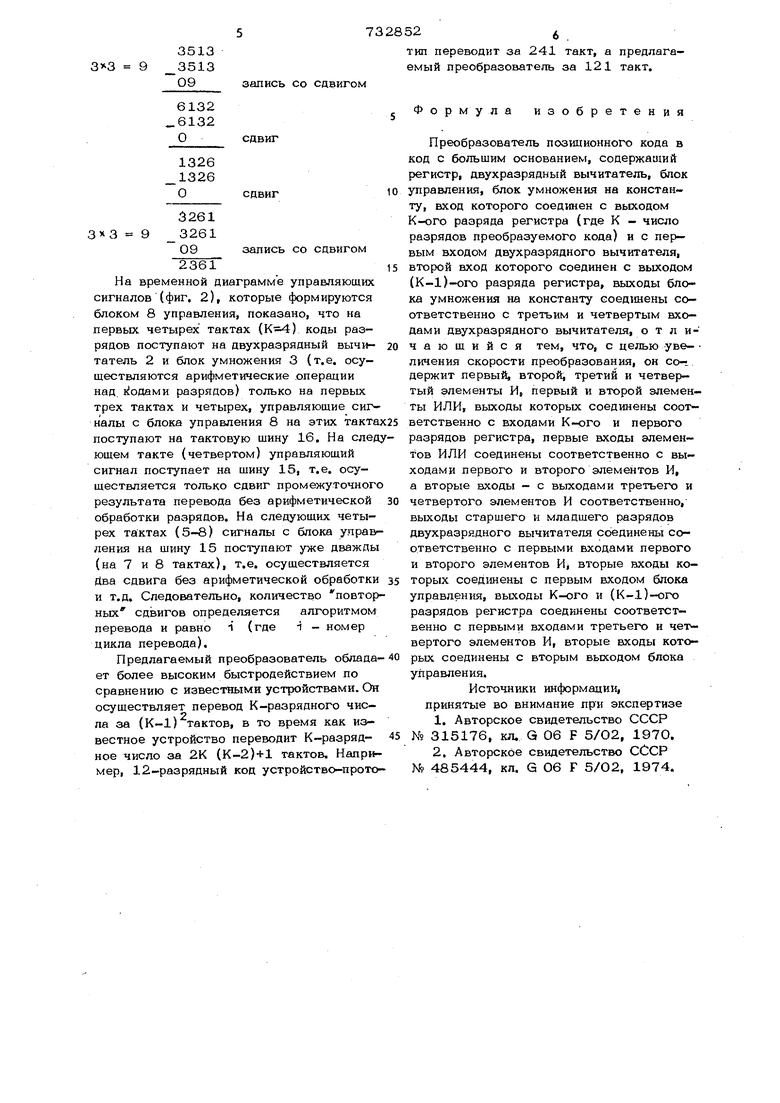

И, а вторые входы - с выходами третьего и четвертого элементов И соответственно, выходы старшего и младшего разрядов двухразрядного вычитателя соедине ны соответственно с первыми входами первого и второго элементов И, вторые входы которых соединены с первым выхо дом блока управления, выходы К-ого и (K-l)-oro разрядов регистра соединены соответственно с первыми входами треть го и четвертого элементов И, вторые вхо ды которых соединены с вторым выходом блока управления. На фиг. 1 изображена блок-схема пре лагаемого устройства; на фиг. 2 - диаграммы управляющих сигналов, вырабаты ваемые блоком управления устройства при преобразовании четырехразрядных кодов. Преобразователь кода содержит К-раз рядный R-ичный регистр 1, где К основание системы счисления, в которую переводится код, двухразрядный вычитатель 2, блок 3 умножения на константу, четыре элемента И 4, 5, 6, 7, блок 8 управления. Выход старшего (К-ого) разряда 9 регистра 1 соединен с входами блока 3 умножения на константу и младшим разрядом 10 вычитателя 2. Выход (K-l)-oro разряда 11 регистра 1 подклю чен к второму входу 12 вычитателя 2. Выход старшего разряда 10 вычитателя 2 через первый элемент И 4 и элемент ИЛИ 13 связан с входом младшего разряда регистра. Выход младшего разряда 12 вычитателя через второй элемент И 5 и элемент ИЛИ 14 объединен с входом первого старшего разряда 9 регистра 1. Выход разряда 9 через третий элемент И 6 подключен к младшему разряду регистра. Выход разряда 11 соединен через четвертый элемент И 7 с разрядом 9 регистра 1. Блок 8 управления связан по шине 15 с элементами 6, 7, а по шине 16 с элементами 5, 4. Рабрта преобразователя рассматривает ся на Ьримере преобразования К - разря ных кодов при К 4. Все схемы, входящие в состав устрой ства, предназначены для работы с кодами чисел в системе счислен.ия с тем основанием, с которым необходмо получить результат; К - разрядный код целого числа, которое необходимо преобразовать, помешают в регистр 1. Код цифры, хранящейся в разряде 9 регистра 1, поступает на блок 3, где происходит умножение на константу, равную разности оснований систем счисления. На вычитателе 2 из двух старших разрядов кода числа, поступающих на регистр 1, вычитается код числа, поступающий с выходов блока 3. На первых трех тактах из блока 8 по шине 16 на элементы И 4, 5 подается разрешающий потенциал, вследствие чего код разности с выхода вычитателя 2 записывается в регистр 1 таким образом, что содержимое старшего разряда 10 вы- читателя 2 записывается в младший разряд регистра 1, а содержимое разряда 12 вычитателя 2 записывается в стар1лий разряд регистра 1. На четвертом такте на элементы И 6, 7из блока 8 управления по шине 15 поступает разрешающий сигнал, в результате чего происходит сдвиг содержимого регистра 1 на один разряд влево, при этом код, хранящийся в старшем разряде 9 регистра 1, переписывается в младший разряд, а код, хранящийся в разряде 11, записывается в разряд 9 регистра 1. На пятом и шестом тактах из блока 8поступает по шине 15 управляющий сигнал на элементы И 6, 7, а на седьмом и восьмом тактах управляющий сигнал по шине 16 поступает на элементы И 4, 5. На (К-1) -ом такте в регистре 1 получается код числа с новым основанием системы счисления. Алгоритм преобразования построен таким образом, что на каждых К шагах (начиная с первого) последовательно обрабатываются К-1, К-2 и т.д. разрядов преобразуемого числа. Последующие К-(К-1), К-(К-2) и т.д. разряды промежуточного результата преобразования остаются без изменения. Пример. ПереЕ1ести - 6612 запись со сдвигом запись со сдвигом 7245 7245 21 запись со сдвигом 1455 О .запись со cnBKTOt.. 3513 9 3513 О9 запись со сдвигом 6132 .6132 О 1326 .1326 3261 9 09 запись со сдвигом 2361 На временной диаграмме управляющих сигналов (фиг, 2), которые формируются блоком 8 управления, показано, что на первых четырех тактах () коды разрядов поступают на двухразрядный вычитатель 2 и блок умножения 3 (т,е, осуществляются арифметические .операции над Годами разрядов) только на первых трех тактах и четырех, управляющие сигналы с блока управления 8 на этих такта поступают на тактовую шину 16, На след ющем такте (четвертчзм) управляющий сигнал поступает на шину 15, т,е, осуществляется только сдвиг промежуточног результата перевода без арифметической обработки разрядов. Ни следующих четырех тактах (5-8) сигналы с блока управ ления на щину 15 поступают уже дважды (на 7 и 8 тактах), т,е, осуществляется Два сдвига без арифметической обработки и т,д. Следовательно, количество повтор ных сдвигов определяется алгоритмом перевода и равно i (где i - номер цикла перевода). Предлагаемый преобразователь облада ет более высоким быстродействием по сравнению с известными устройствами. Он осуществляет перевод К-разрядного числа за (К-1) тактор, в то время как известное устройство переводит К-разрядное число за 2К (К-2)+1 тактов. Напри мер, 12-разрядный код устройство-прото 7 24 тип переводит за 241 такт, а предлагаемый преобразователь за 121 такт. Формула изобретения Преобразователь позиционного кода в код с большим основанием, содержащий регистр, двухразрядный вычитатель, блок управления, блок умножения на константу, вход которого соединен с выходом К-ого разряда регистра (где К - число разрядов преобразуемого кода) и с пер вым входом двухразрядного вычитателя, второй вход которого соединен с выходом (K-l)-oro разряда регистра, выходы блока умножения на константу соед1шены соответственно с третьим и четвертым входами двухразрядного вычитателя, отличающийся тем, что, с целью уве- личения скорости преобразования, он со- держит первый, второй, третий и четвертый элементы И, первый и второй элементы ИЛИ, выходы которых соединены соответственно с входами К-ого и первого разрядов регистра, первые входы элементов ИЛИ соединены соответственно с выходами первого и второго элементов И, а вторые входы - с выходами третьего и четвертого элементов И соответственно, выходы старшего и младшего разрядов двухразрядного вычитателя соединены соответственно с первыми входами первого и второго элементов И| вторые входы которых соед1шены с первым входом блока управления, выходы К-ого и (K-l)-oro разрядов регистра соединены соответственно с первыми входами третьего и четвертого элементов И, вторые входы которых соединены с вторым выходом блока управления. Источники информации, принятые во внимание при экспертизе 1,Авторское свидетельство СССР № 315176, кл. G 06 F 5/02, 1970, 2,Авторское свидетельство СССР NO 485444, кл. G Об F 5/О2, 1974.

UJ

л

и

±1

{.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь кода в код с большим основанием | 1976 |

|

SU581469A1 |

| Преобразователь кода в код с большим основанием | 1973 |

|

SU485444A1 |

| Преобразователь кодов | 1977 |

|

SU779998A1 |

| Преобразователь кодов | 1973 |

|

SU526884A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1979 |

|

SU877521A1 |

| Функциональный преобразователь | 1982 |

|

SU1100621A1 |

| Преобразователь двоичного кода в р-ичный позиционный код | 1983 |

|

SU1163479A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Преобразователь правильной двоично-десятичной дроби в двоичную дробь и целых двоичных чисел в двоично-десятичные | 1978 |

|

SU741260A1 |

| Реверсивный преобразователь двоичного кода в двоично-десятичный код | 1978 |

|

SU771661A1 |

Тактовые

П П П П П П ri П

itMne/fibCbl

inn П П

1i

14

J I .Г

15 i6

Фиг 1

n

П П

n

Фиг. 2

Авторы

Даты

1980-05-05—Публикация

1977-07-18—Подача