ферного регистра, а выход второй схемы совпадения связан с третьи1М входом схемы двоично-десятичного сложения.

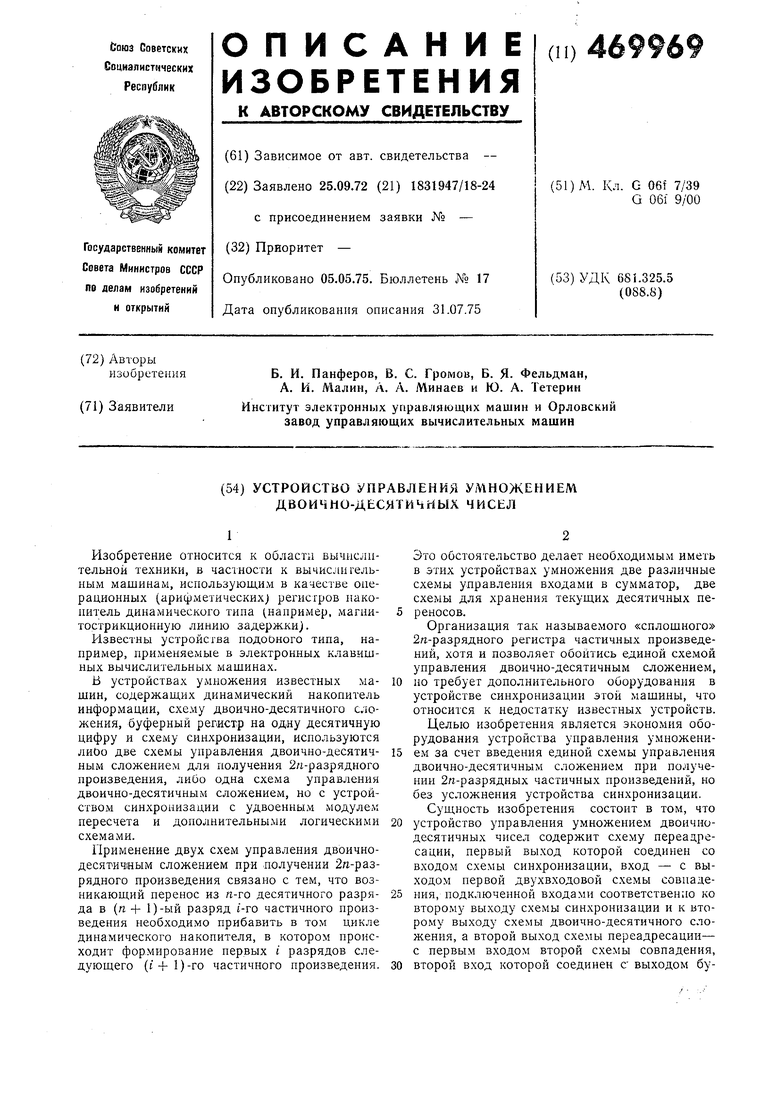

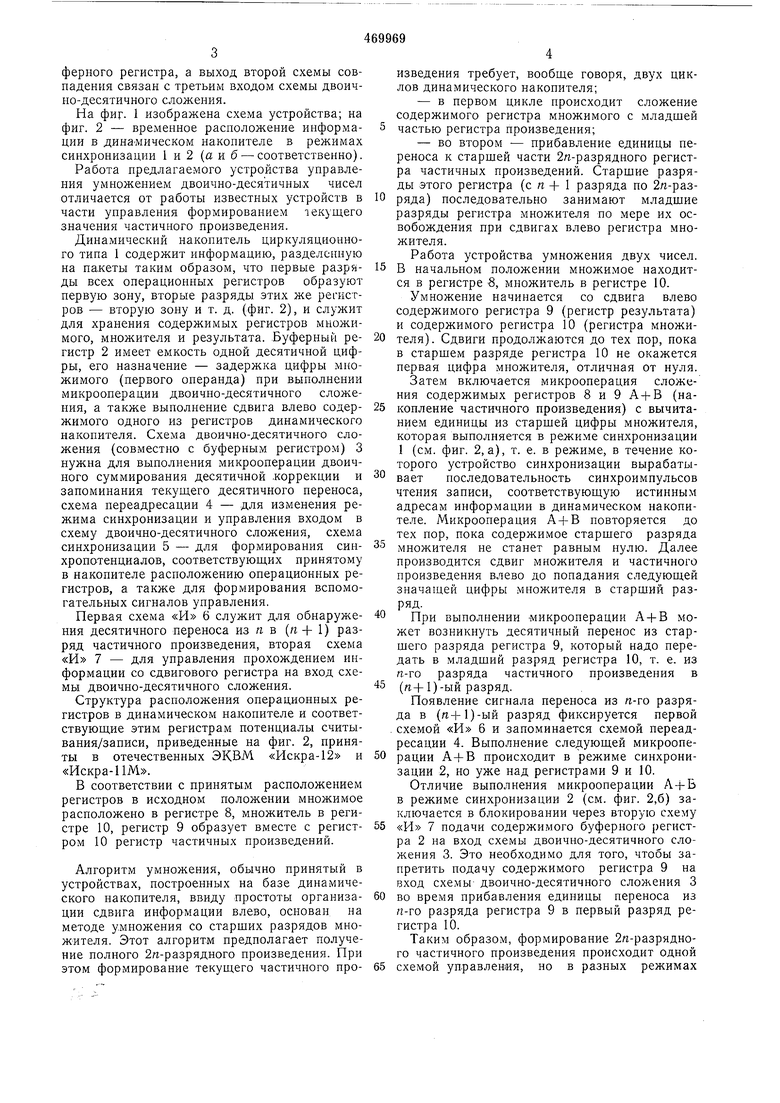

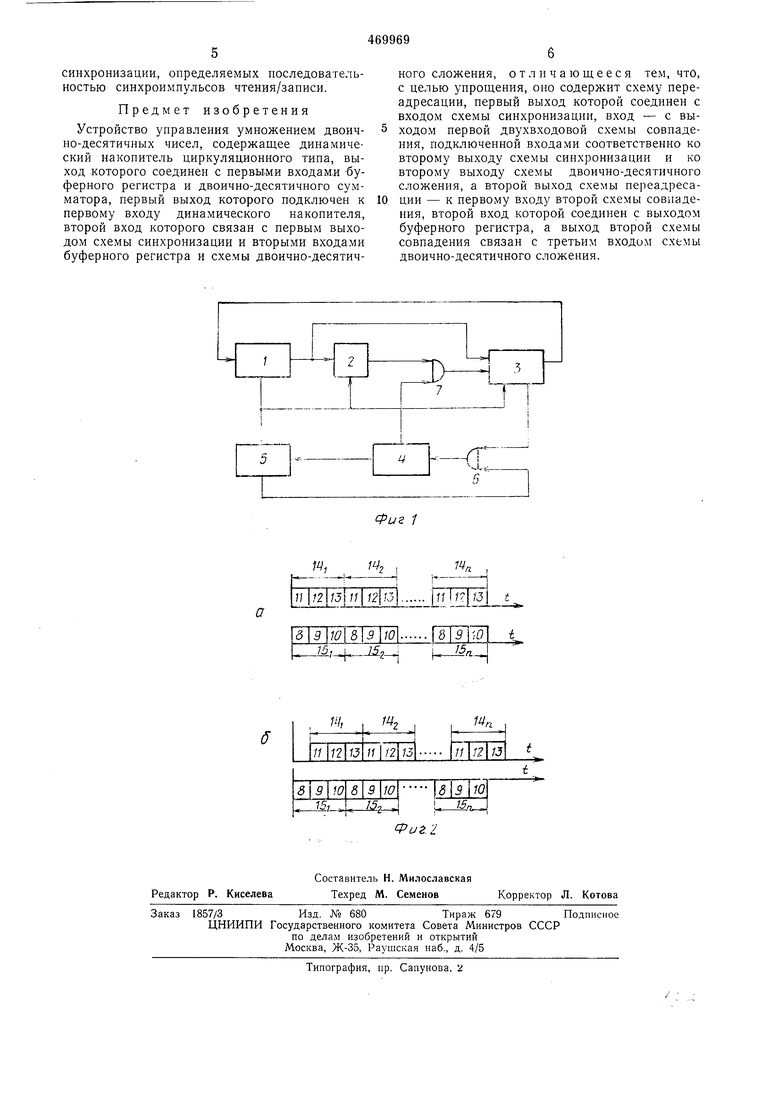

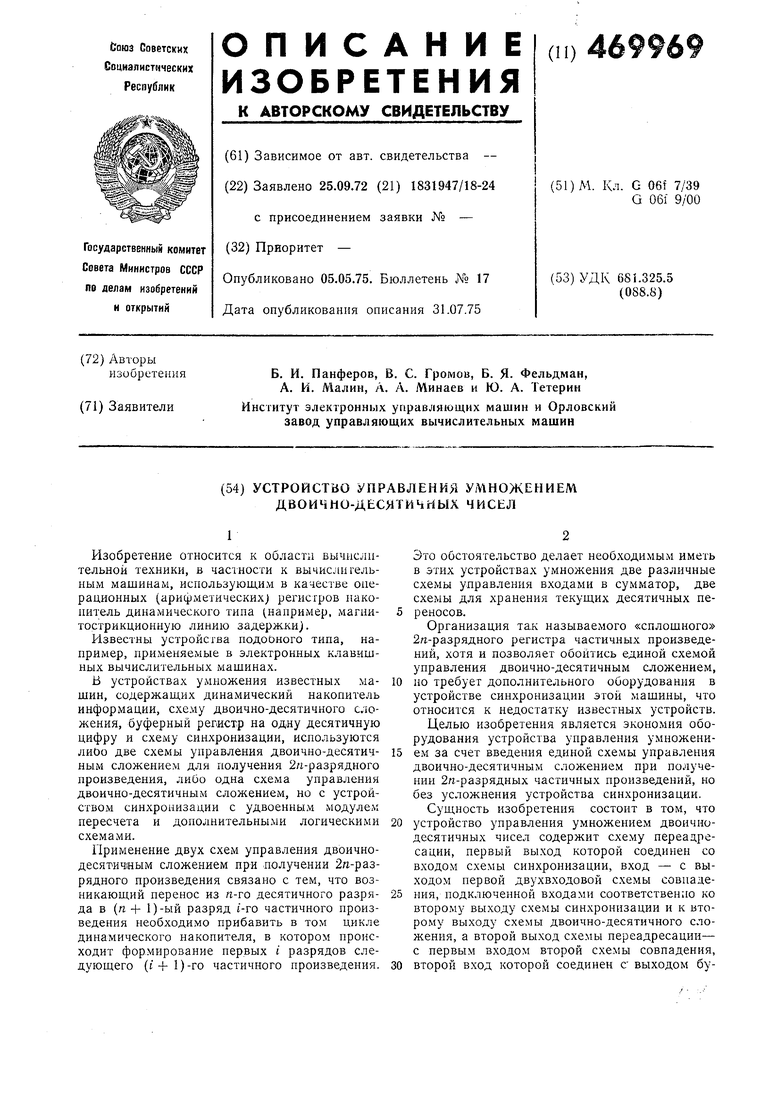

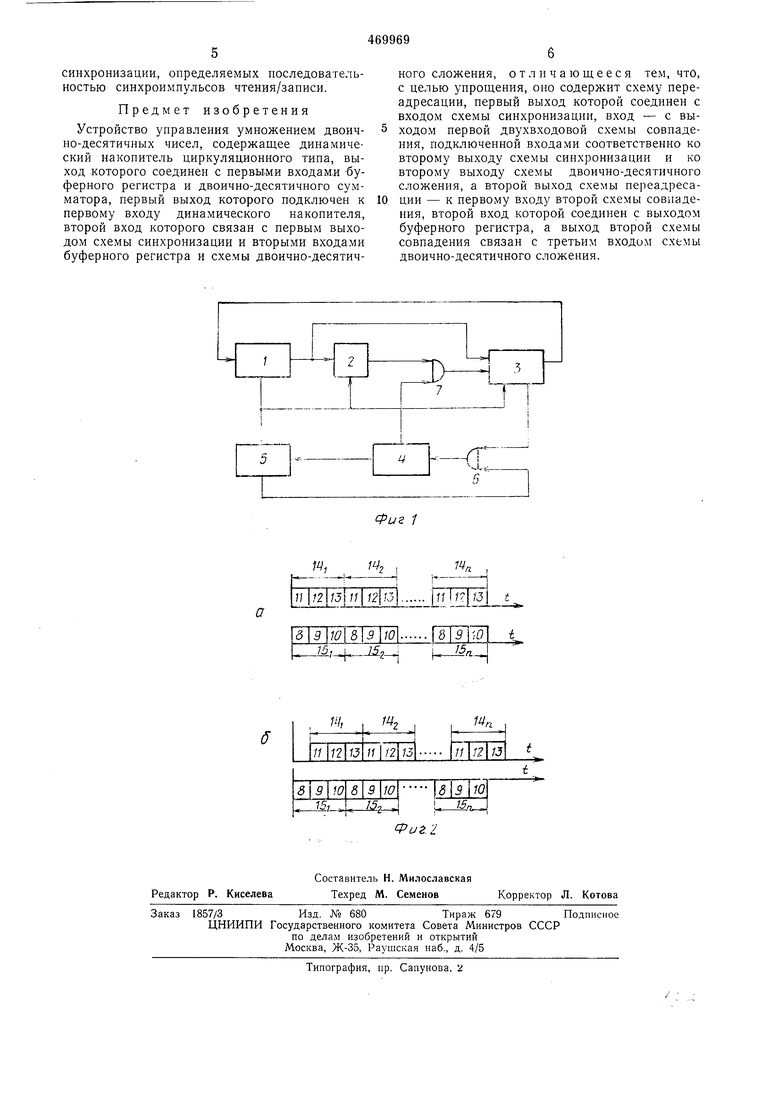

На фиг. 1 изображена схема устройства; на фиг. 2 - временное расположение информации в динамическом накопителе в режимах синхронизации 1 и 2 (а и б - соответственно).

Работа предлагаемого устройства управления умножением двоично-десятичных чисел отличается от работы известных устройств в части управления формированием текущего значения частичного произведения.

Динамический накопитель циркуляциопного типа 1 содержит информацию, разделенную на пакеты таким образом, что первые разряды всех операционных регистров образуют первую зону, вторые разряды этих же регистров - вторую зону и т. д. (фиг. 2), и служит для хранения содержимых регистров множимого, множителя и результата. Буферный регистр 2 имеет емкость одной десятичной цифры, его назначение - задержка цифры множимого (первого операнда) при выполнении микрооперации двоично-десятичного сложения, а также выполнение сдвига влево содержимого одного из регистров динамического накопителя. Схема двоично-десятичного сложения (совместно с буферным регистром) 3 нужна для выполнения микрооперации двоичного суммирования десятичной .коррекции и запоминания текущего десятичного переноса, схема переадресации 4 - для изменения режима синхронизации и управления входом в схему двоично-десятичного сложения, схема синхронизации 5 - для формирования синхропотенциалов, соответствующих принятому в накопителе расположению операционных регистров, а также для формирования вспомогательных сигналов управления.

Первая схема «И 6 служит для обнаружения десятичного переноса из д в (п+ 1) разряд частичного произведения, вторая схема «И 7 - для управления прохождением информации со сдвигового регистра на вход схемы двоично-десятичного сложения.

Структура расположения операционных регистров в динамическом накопителе и соответствующие этим регистрам потенциалы считывания/записи, приведенные на фиг. 2, приняты в отечественных ЭКВМ «Искра-12 и «Искра-ИМ.

В соответствии с принятым расположением регистров в исходном положении множимое расположено в регистре 8, множитель в регистре 10, регистр 9 образует вместе с регистром 10 регистр частичных произведений.

Алгоритм умножения, обычно принятый в устройствах, построенных на базе динамического накопителя, ввиду простоты организации сдвига информации влево, основан на методе умножения со старших разрядов множителя. Этот алгоритм предполагает получение полного 2п-разрядного произведения. При этом формирование текущего частичного произведения требует, вообще говоря, двух циклов динамического накопителя;

-в первом цикле происходит сложение содержимого регистра множимого с младщей

5 частью регистра произведения;

-во втором - прибавление единицы переноса к старщей части 2/г-разрядного регистра частичных произведений. Старщие разряды этого регистра (с п + 1 разряда по 2/г-раз0 ряда) последовательно занимают младшие разряды регистра множителя по мере их освобождения при сдвигах влево регистра множителя. Работа устройства умножения двух чисел.

5 В начальном положении множимое находится в регистре 8, множитель в регистре 10.

Умножение начинается со сдвига влево содержимого регистра 9 (регистр результата) и содержимого регистра 10 (регистра множи0 теля). Сдвиги продолжаются до тех пор, пока в старшем разряде регистра 10 не окажется первая цифра множителя, отличная от нуля. Затем включается микрооперация сложения содержимых регистров 8 и 9 А + В (накопление частичного произведения) с вычитанием единицы из старшей цифры множителя, которая выполняется в режиме синхронизации 1 (см. фиг. 2,а), т. е. в режиме, в течение которого устройство синхронизации вырабатывает последовательность синхроимпульсов чтения записи, соответствующую истинным адресам информации в динамическом накопителе. Микрооперация А + В повторяется до тех пор, пока содержимое старшего разряда

5 множителя не станет равным нулю. Далее производится сдвиг множителя и частичного произведения влево до попадания следующей значащей цифры множителя в старщий разряд.

При выполнении микрооперации А + В может возникнуть десятичный перенос из старшего разряда регистра 9, который надо передать в младший разряд регистра 10, т. е. из п-то разряда частичного произведения в

5 (tt+1)-ый разряд.

Появление сигнала переноса из п-го разряда в (/г+1)-ый разряд фиксируется первой схемой «И 6 и запоминается схемой переадресации 4. Выполнение следующей микрооперации А+В происходит в режиме синхронизации 2, но уже над регистрами 9 и 10.

Отличие выполнения микрооперации А + Ь в режиме синхронизации 2 (см. фиг. 2,6) заключается в блокировании через вторую схему

5 «И 7 подачи содержимого буферного регистра 2 на вход схемы двоично-десятичного сложения 3. Это необходимо для того, чтобы запретить подачу содержимого регистра 9 на вход схемы двоично-десятичного сложения 3

0 во время прибавления единицы переноса из п-го разряда регистра 9 в первый разряд регистра 10.

Таким образом, формирование 2п-разрядного частичного произведепия происходит одной

схемой управления, но в разных режимах

синхронизации, определяемых последовательностью синхроимпульсов чтения/записи.

Предмет изобретения

Устройство управления умножением двоично-десятичных чисел, содержащее динамический накопитель циркуляционного типа, выход которого соединен с первыми входами буферного регистра и двоично-десятичного сумматора, первый выход которого подключен к первому входу динамического накопителя, второй вход которого связан с первым выходом схемы синхронизации и вторыми входами буферного регистра и схемы двоично-десятичного сложения, отличающееся тем, что, с целью упрощения, оно содержит схему переадресации, первый выход которой соединен с входом схемы синхронизации, вход - с выходом первой двухвходовой схемы совпадения, подключенной входами соответственно ко второму выходу схемы синхронизации и ко второму выходу схемы двоично-десятичного сложения, а второй выход схемы переадресации - к первому входу второй схемы совпадения, второй вход которой соединен с выходом буферного регистра, а выход второй схемы совпадения связан с третьим входом схемы двоично-десятичного сложения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения чисел | 1989 |

|

SU1817091A1 |

| ПРОЦЕССОР ДЛЯ ЦИФРОВОЙ СИСТЕМЫ ОБРАБОТКИ ДАННЫХ | 1971 |

|

SU305477A1 |

| Устройство для умножения двоично- десятичных чисел | 1977 |

|

SU748409A1 |

| Цифровая вычислительная машина | 1970 |

|

SU366782A1 |

| Множительное устройство | 1982 |

|

SU1053104A1 |

| Устройство для умножения | 1985 |

|

SU1278838A1 |

| Десятичное множительное устройство | 1972 |

|

SU468239A1 |

| Устройство для умножения | 1989 |

|

SU1668979A1 |

| Множительное устройство | 1982 |

|

SU1116427A1 |

| Арифметическое устройство | 1971 |

|

SU522497A1 |

W

УПТтзГг /2 оI i;),

а

.,Ji27 /г

Авторы

Даты

1975-05-05—Публикация

1972-09-25—Подача