(54) УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ ЧИСЕЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1982 |

|

SU1157542A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Множительное устройство | 1982 |

|

SU1116427A1 |

| Устройство для умножения | 1987 |

|

SU1509875A1 |

| Множительное устройство | 1982 |

|

SU1053104A1 |

| УСТРОЙСТВО для УМНОЖЕНИЯ ДЕСЯТИЧНЫХ ЧИСЕЛ | 1973 |

|

SU390525A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для умножения десятичных чисел | 1981 |

|

SU1016780A1 |

| Арифметическое устройство | 1971 |

|

SU522497A1 |

| Матричное устройство для умножения двоичных и десятичных чисел | 1983 |

|

SU1200282A1 |

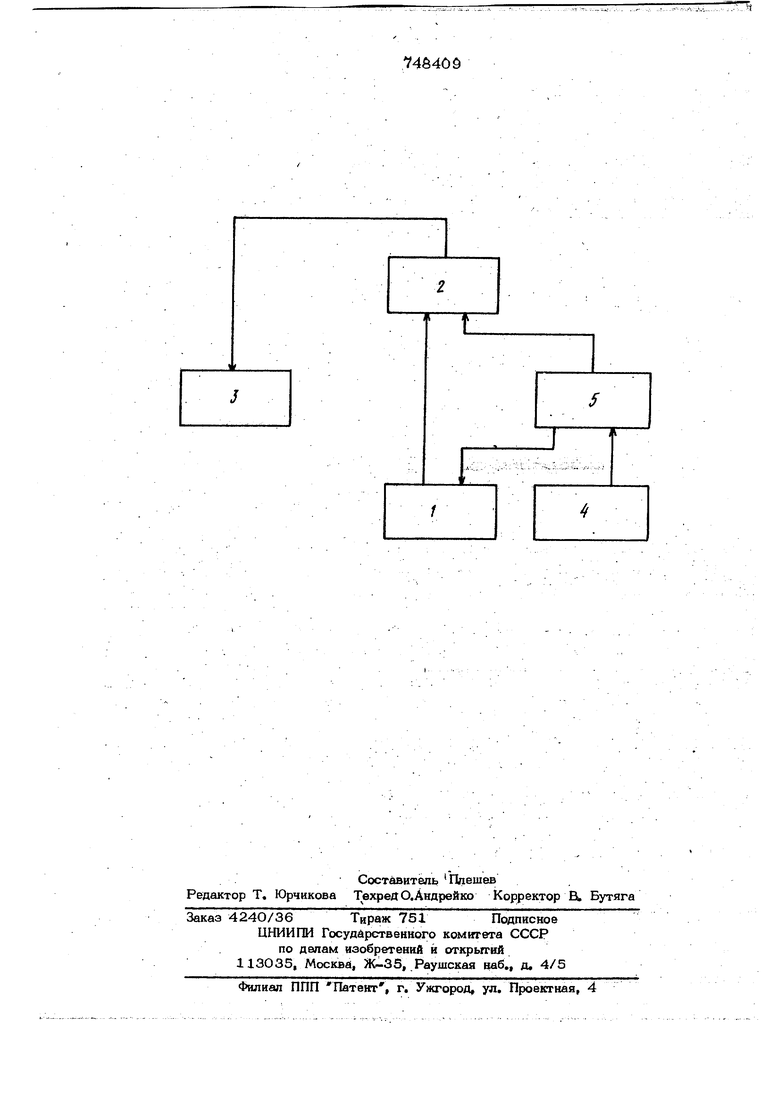

Изобретение относится к области вычислительной техники и предназначено для использования в специализированных вычис лительных машинах. Известно устройство умножения двоичных чисел l , в котором десятичное умножение осуществляется с помощью последовательного сложения, множимое прибавляется к частичному произведению столько раз, какова цифра множителя. Быстродейст вие такого устройства низкое, так как при умножении на h -разрядный множитель нуж но сделать 4,5 и сложений.. Наиболее близким техническим решением к изобретению является устройство для умножения двоично-десятичных чисел 2, содержащее регистр множителя, сумматор частичных произведений, блоки сдвига и определения очередности цифр, причем разрядные выходы регистра множителя подключены к входам блока определейия оч&гредности цифр, выходы которого подключены к управляющим входам блока сдвига. ВЫХОДЫ блока сдвига подключены к входам сумматора частичньрс произведений. Однако известное устройство требует значительных аппаратурных затрат и обла-. дает недостаточным быстродействием при проведении операций с числами, разрядность которых п 4 13. Целью изобретения является повышение быстродействия устройства и снижение аппаратурных затрат. Цель достигается тем, что предложенное устройство дополнительно содержит блок удвоения множимого, разрядные в 1ходы которого соединены с разрядными входами блока сдвига, выход блока определения очередности цифр подключен к входу сдвига блока удвоения множителя, состоящего из h +3 разряда. На чертеже представлена структурная схема устройства умножения двоично-десятичНых чисел. Устройство содфжит блок 1 удвоения множимого блок 2 сдвига, сумматор 3 частичных произведений, регистр 4 множителя, блок 5 определения очередности ЦИФР (БООЦ). В исходном состоянии в блок 1 удвоения множимого и регистр 4 множителя занесены коды сомножителей. В первом цикле умножения в БООЦ-5 определяются тетрады множителя, содержащие единицы в разряде 2°, Так, если множитель представлен числом 1ООО 10О1 О01О, 0001 ООН 0001, то первой будет отмечена первая тетрада (счет тетрад справа налево), в нулевом разряде которой записана единица. В данном случае БООЦ выдает сигналы по которым множимое передается на блок сдвига 2; а затем без проведения микрооперации сдвига на сумматор 3 частичных произведений. Далее в БООЦ определяется единица во второй тетраде и вьщаются сиг налы передачи множимого из блока 1 удвоения множимого через блок сдвига на сумматор частичных произведений со сдви гом на один десятичный разряд влево. В результате последующего анализа тетрад множителя обнаруживаются единицы . в третьей и пятой тетрадах и множимое лередается на сумматор частичных произведений со сдвигом соответственно на два и четьфе десятичных разряда влево. После нахождения всех тетрад множителя, со держащих единицы в разряде 2 , БООЦ дает разрешение на проведение второго ци ла умножения.. . В начале второго цикла по сигналу БООЦ 5 осуществляется удвоение содерж мого блока 1 Удвоения множимого . Удвоение осуществляется сдвигом кода множимого на один двоичный разряд влево и последующей коррекцией полученного при сдвиге числа. Коррекция заключается в п прибавлении числа 6 (ОНО) к содержимому тех тетрад, где имеет место или наличие в тетраде числа больше девяти, или пераход единичного сигнала из млад шей тетрады в старшую. Затем аналогично предыдущему циклу определяются тетрады, содержащие единицы в разряде 2, В приведённс)ы( множителе такими тетрадами являются вторая и четвертая, что соответствует передаче содержащего, блока 1 удвоения множимого в сумматор со сдвигом на один и три соответственно разряда влево в блоке сдвига 2,после чегю дается разрешение БООЦ 5 на про- 55 ведение третьего числа умножения. Третий и четвертый циклы умножения осуществляются аналогично второму циклу.

74640S Итак, для получения чисел, кратных множимому, нужно осуществить три операции сдвига вместо восьми операций сложения, как в прототипе. Для умножения на п -разрядный множитель требуется осуществить три сдвига и 1,5п сложений. Время осуществления операции сдвига меньше времени осуществления операции сложения более чем в два раза. Среднее время умножения на п -разрядный множитель в предлагаемом устройстве T.y--.5UM.5 n:t в прототипе , &tcft 4A где - время осуществления операции сложения.. Из уравнения 1,.+ t л1 П fi находим, что время выполнения операции умножения в предлагаемом устройстве « меньше, чем в прототипе, если копичество десятичных разрядов множителя п 4 13. В частности, для Т 9i. I -lit. .11 7СсЛ ) ПС-м , . для 0 Устройство можно выполнить на современных интегральных микросхемах. Его использование дает возможность уменьшить конструктивные размеры вычислительной мащшы и повысить ее быстродействие. Фо рмула изобретения Устройство для умножения двоичнодесятичных чисел, содержащее регистр множителя, сумматор частичных произведений, блок сдвига и блок определения очерёдности цифр, причем разрядные выходы регистра множителя подключены к аходам блока определения очередности цифр, выходы которого подключены к управляющим входам блока сдвига, выходы блока сдвига подключены к. входам сумматора частичных, произведений, о т л и чающееся тем, что,с целью повыщения быстродействия устройства и снижения аппаратурных затрат, в него введен блок удвоения множимого, содержащий П +3 разряда, где п - количество разрядов множимого, при этом разрядные выходы блока удвоения множимого соединены с разрядными в ходами блока сдвига, выход блока определения очередности цифр подключен к входу сдвига блока удвоения множимого. Источники информации, принятые во внимание при экспертизе 1. Майоров С. А. Принципы организации цифровых машин. Ленинград, Машиностроение, 1974, с. 322-323. 2. Авторское свидетельство СССР № 510714, кл. q 06 F 7/52, 05,05.74 (прототип).

Авторы

Даты

1980-07-15—Публикация

1977-03-28—Подача