1

Изобретение относится к области вычислительной техники.

Известны устройства, совмещающие функции записи и считывания, содержащие два транзистора записи, эмиттеры которых соединены с шиной записи-воспроизведения, базы - с шиной записи, и два дополнительных транзистора.

Недостатком таких устройств является ограниченное быстродействие из-за значительной паразитной емкости на шине записи-воспроизведения, за счет подключения к ней большого количества ячеек запоминания на МОП-структурах, имеющих значительное выходное сопротивление, сигналы считывания которых лежат в области микротоков. В таких устройствах при отсутствии сигнала потенциал шины записи-воспроизведения находится в неопределенном состоянии относительно шины нулевого потенциала.

При появлении тока считывания в шине записи-воспроизведения выходной транзистор не открывается до тех пор, пока не перезарядится паразитная емкость этой шины до величины отпирания перехода эмиттер - база одного из транзисторов записи. В результате происходит задержка выходного сигнала воспроизведения относительно сигнала считывания.

Целью изобретения является повышение быстродействия и помехозащищенности устройства.

Эта цель достигается тем, что между шиной 5 записи-воспроизведения и источником питания включены последовательно соединенные резистор и диод, общая точка которых соединена с коллектором входного транзистора, а база выходного транзистора через -резистор под0 ключена к источнику питания.

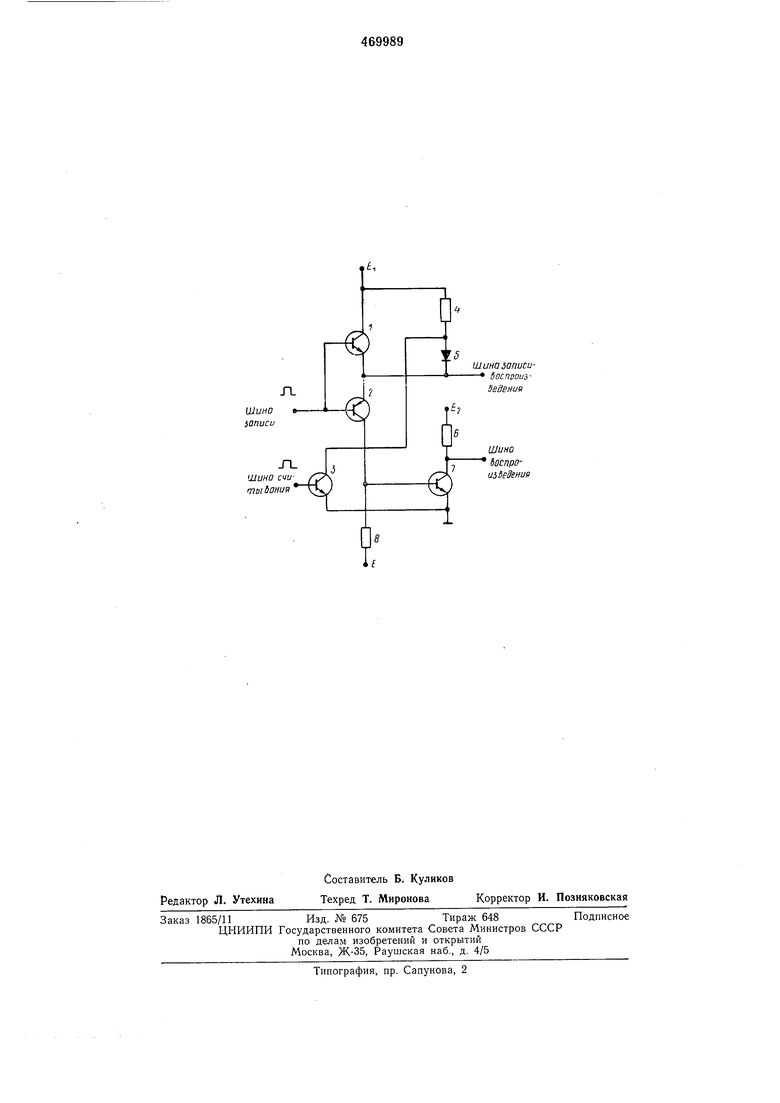

На чертеже представлена принципиальная электрическая схема устройства для записи и считывания.

Устройство содержит транзисторы 1, 2, вы5 полняющие функцию записи, которые объединены базами в общую точку на шине записи, а эмиттерами - в общую точку на шине записи-воспроизведения. Коллектор транзистора 1 находится под потенциалом Ei источника ;на0 пряжения.

Кроме того, устройство содержит транзистор 3, резистор 4, диод 5, резистор 6, соединенный с коллектором транзистора 7, и резистор 8, соединенный с коллектором транзистора 2. 5 Устройство работает следующим образом.

Источник напряжения EZ, питающий транзистор 7, выполняет функцию согласования по амплитуде выходного сигнала воспроизведения с последующим логическим элементом.

Источник иапряжения Ei является общим для накопителя и для устройства записи и считывания. Источйик иапряжения -Ьсм через резистор 8 на базу транзистора подает запирающее напряжение.

В исходном состоянии на шину записи и щину считывания подаются нулевые потенциалы, при этом транзисторы 1 и 3 заперты, а транзисторы 2 и 7 открыты. Через резистор 4 и диод 5 В цепь эмиттера транзистора 2 протекает ток, в результате чего фиксируется потенциал щины записи-воспроизведения. Протекая через эмиттерно-коллекторную цепь транзистора 2, этот ток вызывает на резисторе 8 падение напряжения, комиенсирующее «апряжение источника ом и отпирающее транзистор 7.

В режиме записи логической единицы «а щину записи подается положительный импульс. В результате транзистор 2 закрывается, а транзистор 1 открывается.

В режиме считываиня ключевой транзистор также открыт, а потенциал щины записи близок к нулю.

При считывании логической единицы через транзистор 2 в шину записи-.воспроизведения течет ток. При подаче стробирующего импульса на шину считывания отпирается транзистор 3, и ток через резистор 4 начинает протекать через коллекторно-эмиттерный переход этого транзистора, а диод 5 запирается. В результате в эмиттерно-коллекторной цепи транзистора 2 протекает только ток считывания логической единицы, который продолжает поддерЖ|Ивать выходной транзистор 7 в открытом состоянии, и на шине воспроизведения держится низкий потенциальный уровень. При этом по шине воспроизведения происходит передача логической единицы в инверсной форме.

Перед считыванием логической единицы за счет протекания тока через резистор 4 и диод 5 в цепи эмиттера транзистора 2 происходит подзарядка паразитной емкости, поэтому исключается задержка сигнала логической единицы на шине записи-воспроизведения.

При считывании логического нуля подается стробирующий импульс на щину считывания.

В результате транзистор 3 открывается, а диод 5 и транзистор 7 запираются. Через эмиттерно-коллекторный переход транзистора 2 в установившемся режиме протекают ток считывания логического нуля и ток утечки остальных элементов. Величина этих токов не позволяет скомпенсировать напряжение источника ECU и открыть транзистор 7 даже при условии действия синфазной помехи, в цепи передачи, сигнала. Следовательно, при считывании логического нуля транзистор 7 запирается, и на щпне воспроизведения появляется высокий потенциальный уровень, близкий к напряжению источника EZ, т, е. передается логический

5 нуль в инверсной форме. Время передачи логического нуля относительно переднего фронта строб-импульса на щине считывания определяется в основном временем разряда паразитной емкости на щине записи-воспроизведеQ ния. Это время очень мало, так как емкость разряжается через транзистор 2, который ло отнощению к емкостной нагрузке включен по схеме с общей базой, имеющей входное сонротивление несколько десятков Ом.

Предмет изобретения

Устройство для записи и считывания, содержащее два транзистора записи, эмиттеры .которых .соединены с щиной записи-воспроизвеQ дения, базы - с щиной записи, коллектор одного из транзисторов записи соединен с источником пита.ния, коллектор другого-с базой выходного транзистора, коллектор выходного транзистора соединен с щиной воспроизведения и через резистор с источником питания выходного транзистора, входной транзистор, база которого соединена с щиной считывания, эмиттеры входного ;и выходного транзисторов соединены с щиной нулевого потенциала, отличающееся тем, что, с целью повыщения быстродействия и помехозащищенности устройства, между щиной записи-воспроизведения и источ.ником иитания включены последовательно соединенные резистор и диод,

с- общая точка которых соединена с коллектором входного транзистора, а база выходного транзистора .через резистор подключена к источнику смещения.

шиназаписи боспроизУедениа

Шино

SocnpffuiteScHUfi

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обращения к памяти (его варианты) | 1982 |

|

SU1092561A1 |

| Постоянное запоминающее устройство | 1982 |

|

SU1112411A1 |

| Устройство для записи и считывания информации | 1972 |

|

SU499584A1 |

| Инвертор | 1976 |

|

SU615604A1 |

| Стробируемый формирователь с парафазными ттл-выходами | 1978 |

|

SU758502A1 |

| РЕВЕРСИВНЫЙ РЕГИСТР СДВИГА | 1973 |

|

SU389548A1 |

| Усилитель записи и считывания для запоминающего устройства с произвольной выборкой | 1983 |

|

SU1091223A1 |

| Запоминающее устройство | 1985 |

|

SU1269208A1 |

| ПЬЕЗОТРАНСФОРМАТОРНОЕ ЗАПОЛИШАЮЩЕЕ УСТРОЙМТ?|11е0-1ЕЛКГ1:: | 1972 |

|

SU331421A1 |

| Преобразователь уровня сигнала для усилителя считывания | 1983 |

|

SU1134966A1 |

Авторы

Даты

1975-05-05—Публикация

1973-01-09—Подача