1

Изобретение относится к области вычисли. тельной техники.

При управлении реальными физическими процессами с помощью вычислительной машины (ВМ) в нее необходимо вводить oneративную информацию, характеризующую изменение ряда параметров процесса, причем часто такая, информация представляется в виде последовательности приращений параметров, в частности в число-импульсном коде.

Известны устройства для сопряжения ВМ с датчиками приращений, содержащие-буферный регистр, информационные входы которого соединены со входами устройства, и вентили.

Первичная обработка введенной с помощью известных устройств информации - формирование текущего значения каждого параметра как суммы поступающих приращений, приведение этого параметра к стандартному формату операнда, используемому в данной мащине распределение каждого из параметров по отдельным адресам и т. д. осуществляемая программным путем, может потребовать недопустимо больщих затрат машинного времени. Попытки сократить затраты мащннного времени приводят к тому, что для каждого параметра осуществляют предварительное накопление суммы поступивших приращений по каждому параметру в буферном запоминающем устройстве, которое в простейшем случае может представлять собой набор счетчиков, по одному для каждого из каналов поступления приращепий, совокупность которых и представляет собой буферный регистр. Частота опроса буферного регистра при этом может быть снижена за счет существенного увеличения затрат оборудования в буферном регистре.

Целью изобретения является сокращение затрат машинного времени на ввод и первичную обработку информации.

Эта цель достигается за счет того, что в предложенном устройстве каждый выход буферного регистра соединен через вентиль с соответствующими разрядами сумматора ВМ. Управляющие входы вентилей и вход установки в исходное состояние буферного регистра подключены к выходу блока управления ВМ.

Это дает возможность суммировать приращеппя от группы датчиков с помощью сумматора арифметического блока машины одновременно с их вводом, хранить частичные суммы в оперативной памяти мащины и понизить частоту последующей первпчной обработки но сравнению с частотой ввода приращений.

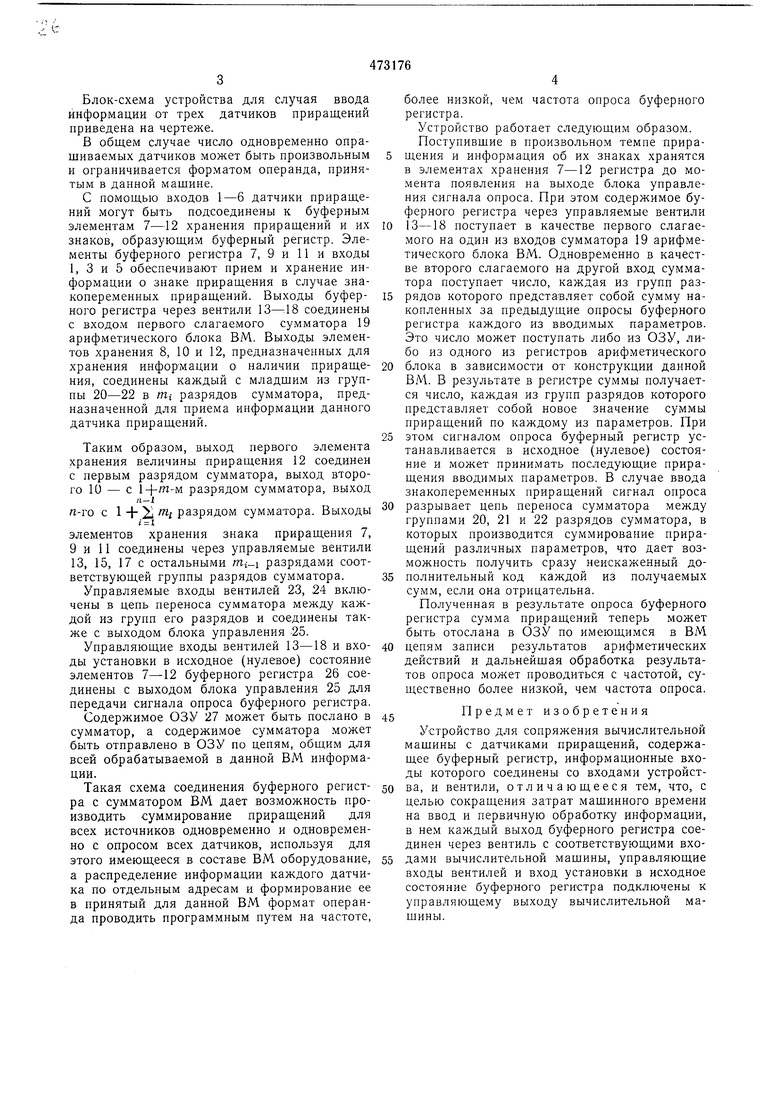

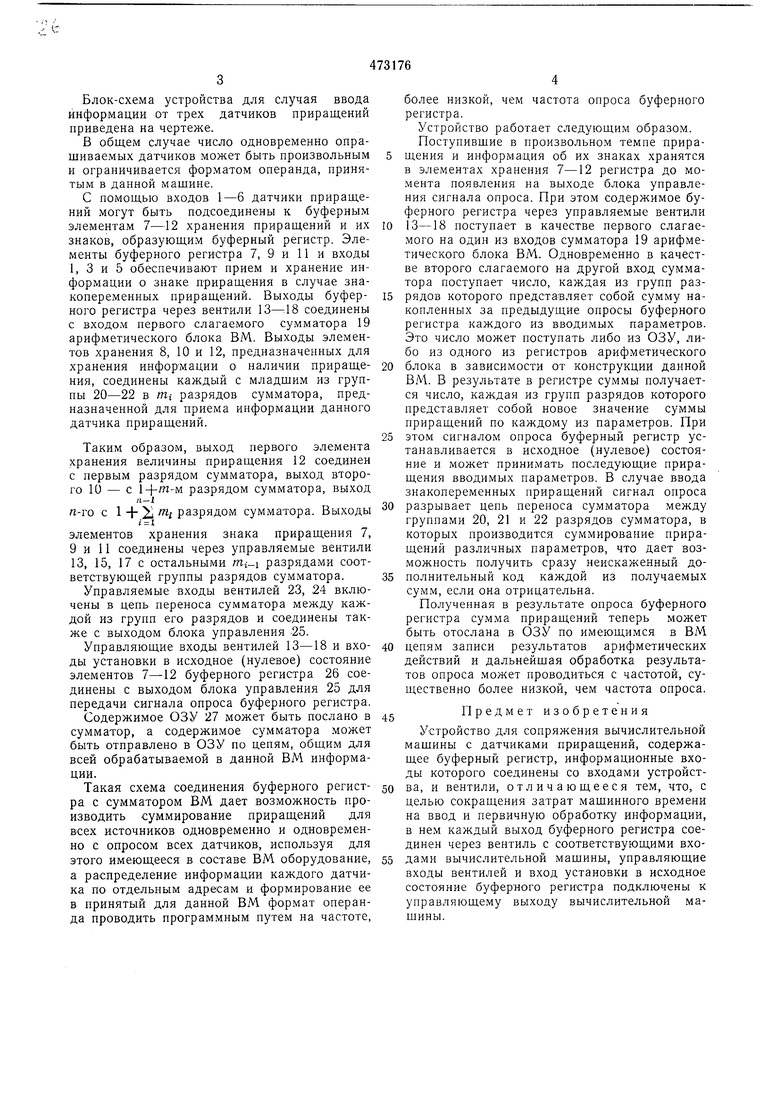

Блок-схема устройства для случая ввода информации от трех датчиков приращений приведена на чертеже.

В общем случае число одновременно опрашиваемых датчиков может быть произвольным и ограничивается форматом операнда, принятым в данной машине.

С помощью входов 1-6 датчики приращений могут быть подсоединены к буферным элементам 7-12 хранения приращений и их знаков, образующим буферный регистр. Элементы буферного регистра 7, 9 и 11 и входы 1, 3 и 5 обеспечивают прием и хранение информации о знаке приращения в случае знакопеременных приращений. Выходы буферного регистра через вентили соединены с входом первого слагаемого сумматора 19 арифметического блока ВМ. Выходы элементов хранения 8, 10 и 12, предназначенных для хранения информации о наличии приращения, соединены каждый с младшим из группы 20-22 в tUi разрядов сумматора, предназначенной для приема информации данного датчика приращений. Таким образом, выход первого элемента

хранения величины приращения 12 соединен с первым разрядом сумматора, выход второго 10 - с 1-|-яг-м разрядом сумматора, выход

i-l

rt-го с I -{- Щ разрядом сумматора. Выходы

элементов хранения знака приращения 7, 9 и 11 соединены через управляемые вентили 13, 15, 17 с остальными разрядами соответствующей группы разрядов сумматора.

Управляемые входы вентилей 23, 24 включены в цепь переноса сумматора между каждой из групп его разрядов и соединены также с выходом блока управления -25.

Управляющие входы вентилей 13-18 и входы установки в исходное (нулевое) состояние элементов 7-12 буферного регистра 26 соединены с выходом блока управления 25 для передачи сигнала опроса буферного регистра.

Содержимое ОЗУ 27 может быть послано в сумматор, а содержимое сумматора может быть отправлено в ОЗУ по цепям, общим для всей обрабатываемой в данной ВМ информации.

Такая схема соединения буферного регистра с сумматором ВМ дает возможность производить суммирование приращений для всех источников одновременно и одновременно с опросом всех датчиков, используя для этого имеющееся в составе ВМ оборудование, а распределение информации каждого датчика по отдельным адресам и формирование ее в принятый для данной ВМ формат операнда проводить программным путем на частоте,

более низкой, чем частота опроса буферного регистра.

Устройство работает следующим образом.

Поступившие в произвольном темпе приращения и информация об их знаках хранятся в элементах хранения 7-12 регистра до момента появления на выходе блока управления сигнала опроса. При этом содержимое буферного регистра через управляемые вентили 13-18 поступает в качестве первого слагаемого на один из входов сумматора 19 арифметического блока ВМ. Одновременно в качестве второго слагаемого на другой вход сумматора поступает число, каждая из групп разрядов которого представляет собой сумму накопленных за предыдущие опросы буферного регистра каждого из вводимых параметров. Это число может поступать либо из ОЗУ, либо из одного из регистров арифметического блока в зависимости от конструкции данной ВМ. В результате в регистре суммы получается число, каждая из групп разрядов которого представляет собой новое значение суммы приращений по каждому из параметров. При этом сигналом опроса буферный регистр устанавливается в исходное (нулевое) состояние и может принимать последующие приращения вводимых параметров. В случае ввода знакопеременных приращений сигнал опроса разрывает цепь переноса сумматора между группами 20, 21 и 22 разрядов сумматора, в которых производится суммирование приращений различных параметров, что дает возможность получить сразу неискаженный дополнительный код каждой из получаемых сумм, если она отрицательна.

Полученная в результате опроса буферного регистра сумма приращений теперь может быть отослана в ОЗУ по имеющимся в ВМ цепям записи результатов арифметических действий и дальнейшая обработка результатов опроса может проводиться с частотой, существенно более низкой, чем частота опроса.

Предмет изобретения

Устройство для сопряжения вычислительной машины с датчиками приращений, содержащее буферный регистр, информационные входы которого соединены со входами устройства, и вентили, отличающееся тем, что, с целью сокращения затрат мащинного времени на ввод и первичную обработку информации, в нем каждый выход буферного регистра соединен через вентиль с соответствующими входами вычислительной машины, управляюшие входы вентилей и вход установки в исходное состояние буферного регистра подключены к управляюшему выходу вычислительной машины.

| название | год | авторы | номер документа |

|---|---|---|---|

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ЦИФРОВОЙ МОДЕЛИ | 1967 |

|

SU223472A1 |

| Вычислительное устройство | 1975 |

|

SU705478A1 |

| ЛОГИЧЕСКИЙ БЛОК АРИФМЕТИЧЕСКОГО УСТРОЙСТВА | 1969 |

|

SU241108A1 |

| Устройство для считывания графической информации | 1973 |

|

SU667976A1 |

| Устройство для обработки и передачи информации учета товарной нефти | 1983 |

|

SU1129625A1 |

| Устройство для предварительной обработки информации | 1991 |

|

SU1837274A1 |

| КОМБИНИРОВАННАЯ ЦИФРОВАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА | 1966 |

|

SU224910A1 |

| Вычислительная система | 1977 |

|

SU692400A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1700558A1 |

| Устройство для умножения | 1976 |

|

SU651341A1 |

Авторы

Даты

1975-06-05—Публикация

1973-07-26—Подача