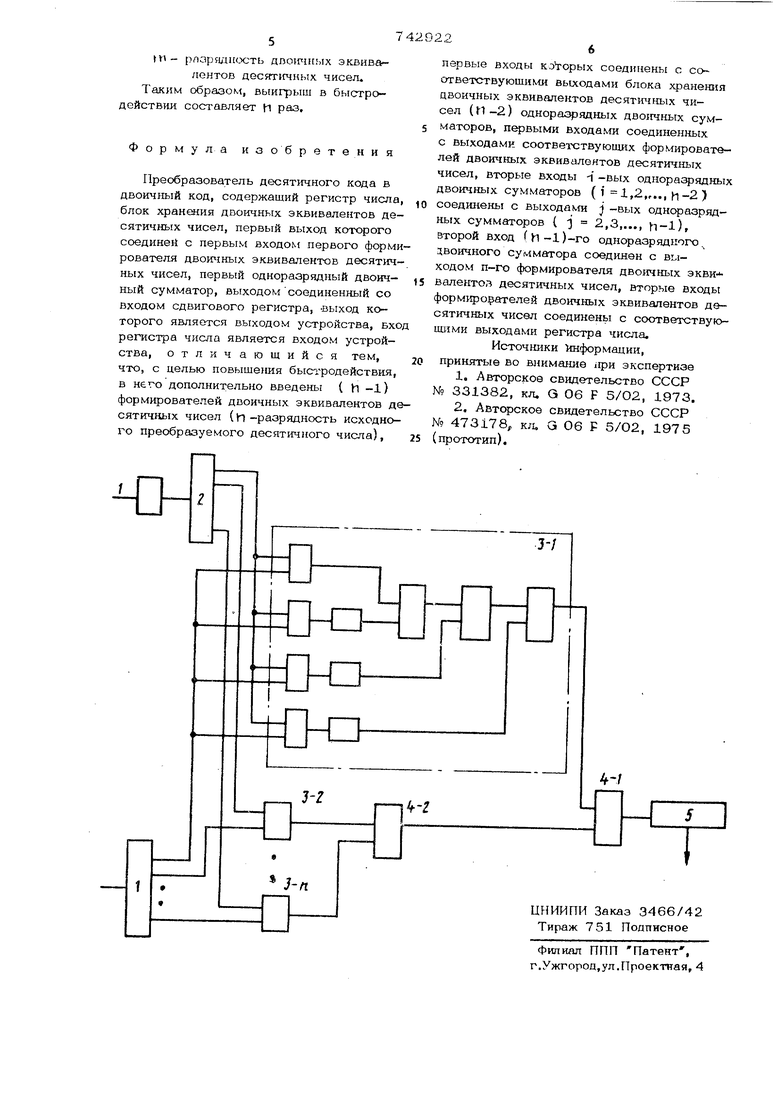

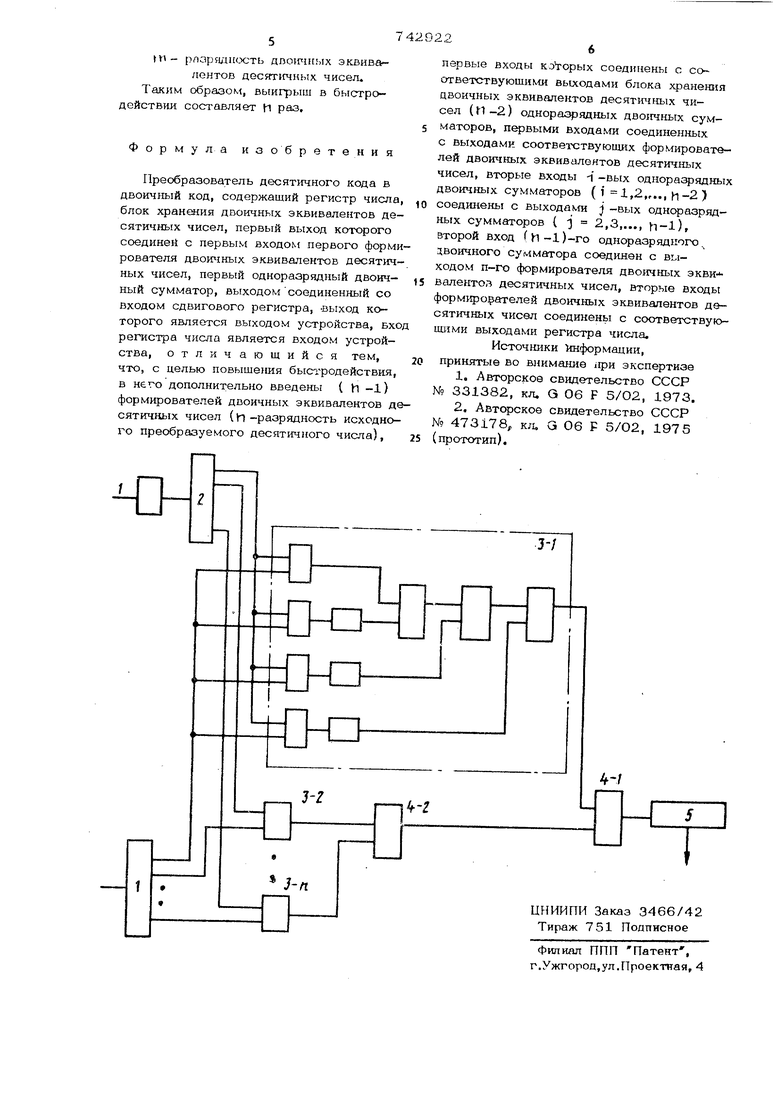

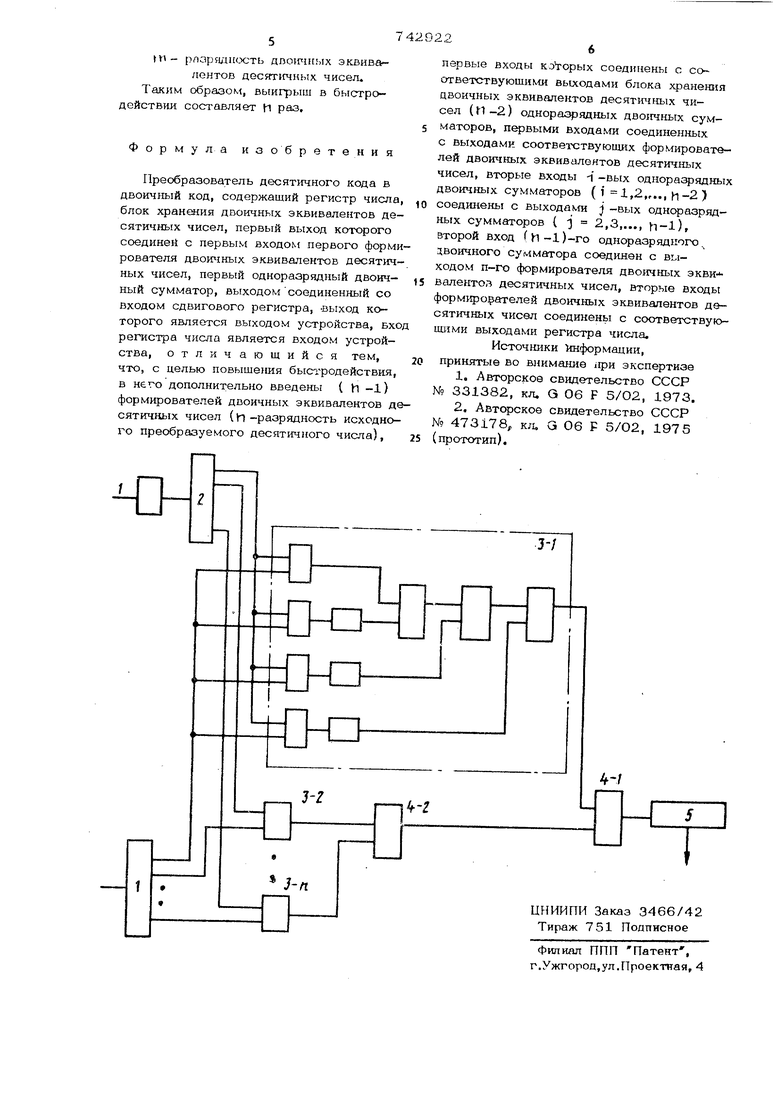

Изобретение относится к автоматике и вычислительной технике и может быть использовано для преобразования дробных чисел, представленных в двоичнодесятичном коде, в двоичный код. Известен преобразователь десятичного кода в двоичный код, содержащий регистр числа, распределитель двоичных разр5щов по весам, блок управления, переключатель эквивааентов, запоминающее устройство, одноразрядный двоичный сумматор и сдви гающий регистр l. Это устройство использует метод суммирования двоичных эквивалентов разрядов. На преобразовани W разрядов двоично-десятичного числа в двоичное число требуется hi циклов, где KW число разрядов в тетраде двоично-деся тичного числа. Наиболее близким к данному изобретению техническим решением является универсальный преобразователь двоичнодесятичных чисел в двоичные, содержащий регистр тетрады и переключатель эквивалентов, входы которых соединены с управляющей шиной, выходы регистра тетрады соединены со входами дешифратора, выходы переключателя эквивалентов соединены со входами блоха хранения двоичных эквивапенггов десятичных чисел, одноразрадный двоичный сумматор, выход которого соедин н со входом регистра сдвига, выход последнего соединен со входом одноразрядного двоичного сумматора ключ, формирователь двоичных эквивалентов десятичных чисел, вьптолненный на одноразрядных двоичных сумматорах и линии задержки, выход блока зфанения двоичных эквивалентов десятичных чисел соединен со входами линии задержки и первого одноразрядного двоичного сумматора формирователя двоичных эквивалентов десятичных чисел, выход первого одноразрядного двоичного сумматсфа соединен со входом второго одноразрядного двоичного сумматора того же формирователя, выходы линии задержки и всех одвс ах ядных двоичных сумматоров фор ищзователя двоичных аквивалеггтов десятичных чисел соединены со входами клю чей, faropbie входы соединены с соответс вуюшимк выходеми дешифратора, выходы ключей соединены со вкоцом одноразрядного двоичного сумматора 21, Одёгако и это устройство использующ метод косвешюго умножения т- той пре образуемой тетрады на соответствующий дво1«Шз1й эквивалент 1U, имеет низкое быстродействие, так как длл преобрвхзова Тетрад необходимо затратить время прямо пропорциональное чиапу разрядов .uecaTJf4Horo ч1ксла T -t-K-m, где с - длительность тшсгирующего импульсарК - число разрядов двоичного экви-Валента вида Цель предлагаемого изобретения повышение быстродействия, Это достигается тем что в преобразователь дополнительно введены (VI -1) (|юрмирователей двоичных чисел ( разрядность преобразуемого десят ного числа), лервые входы которых сое- дю1ены с соответствующими вь(ходами блока храиепшя двоилных эквивалектов десятич11ых чисел, ( одноразрядных двоичных сумматоров, первыми входами сое динен.ных с выходами соответствующи 4юрм5фователей двоичных эквивапентов десяти:ч..ных чисел,, вторые входы -1-ых одноразрядных двоичных сумматоров ( 1-1,2,,,,, 1-1) соединены с выходам i -ьх одноразр.ядных сумматоров ( 2,3,... и-1). второй вход (S-vl)-ro одноразрядного двоичного сумматора соедине с выходом п-го формирователя эквивалентов десят1-г ных чисел, вторые входы формирователей двоичнЕ11х эквивалентов десятичных чисеэт соединены с соот ветствующими выходами регистра числа. На. чертеже представлена блок-схема предлагаемого устройства. Устройство содержит регистр 1 числа блок 2 хранения двоичных эквивалеьгтов десятичных чисел, формирователи 3-1, 3-2„„.311 Двоичных эквивалентов десятич чисел, одноразрядные двоичные cytv маторы4-1, 4-2,,„, 4-(и-1) сдвиговьЕй регистр 5е Преобразование осуществляется путем одновременного суммировашш двоичных эквивалентов считываемых тетрад двоично-десятичного кода и осуществляется в соответствии ио следующим алгоритмом Л.,,Т,, iH 2 npeo6pa3OBajaioe дво1гчное число:двоичный эквивалент вида 10; Т тетрада двоично-десятичного чис/ui, lATpoftcTBo работает следуюишм обраВ регистр 1 числа заносятся тетрады преобраауемого двоично-десятичного кода Одновременно в устройство начинакзт поступать управляющие сигналы, распределеш1ые во времени, число которых определяется числом разрядов двоичшях экзявачентов вида , Из блока хранения двоичных эквивалентов десятичных чисел считываются одновременно i дво -иных эквивал.ентов вида , которые поступают на первые входы формирователей 3 двоичных эквивштентов десятичк1ях чисел, на вторые входы которых поступают коды ДВОИЧ.НО-,десятичных чисел, считываемых с регистра 1 числа, эквиваленты, снимаемые с выходом первого и второго формирователя 3-1 и 3-2 двоичных эквивалентов десятичньгх чисел поступают на первые входы первого и второго одноразрядных двоичных сумматоров 4-1 и 4-2. На второй вг.од первого одноразрядного двоичного сумматора 4-1 инфopмaJiия поступает с выхода второго одноразрядного двоичного сумматора 4-2. На второй вход ( -i -1)-го одноразрядного двоичного сумматора 4 информация поступает с выхода i -того формирователя двоичных эквивалентов десятичных чисел. Результат суммирования всех двоиг ных чисел захшсывается с первого одноразрядного двоичного сумматора 4-1 на сдвигающий регистр 5. Преобразованная двоичная 1шформация снимается с его выхода. Таким образом, процесс преобразования двоично-десятичного числа заключается в одновременном суммировании 1 двоичных эквивапентов десятичных чисел, поступающих последовательным кодом на j одноразрядных двоичных сумматора 4, Время преобразования i тетрад двоично-десятичного числа в известном преобразователе определяется соотношением Y-t-VY -n(д) Время работрл данного устройства определяется выражением (2) где -t - длительность тшстирующего импульса; VI - число преобразуемых разрядов;

Авторы

Даты

1980-06-25—Публикация

1977-12-12—Подача