второго элемента задержки, а выходы подсоединены к информационнЫМ входам блока триггеров. Вход вто:р ого формдрОВателя двоичных эквивалентов соединен с выходом первого элемента задержки, а выходы (подключены к вторым входам блока элементов «И.

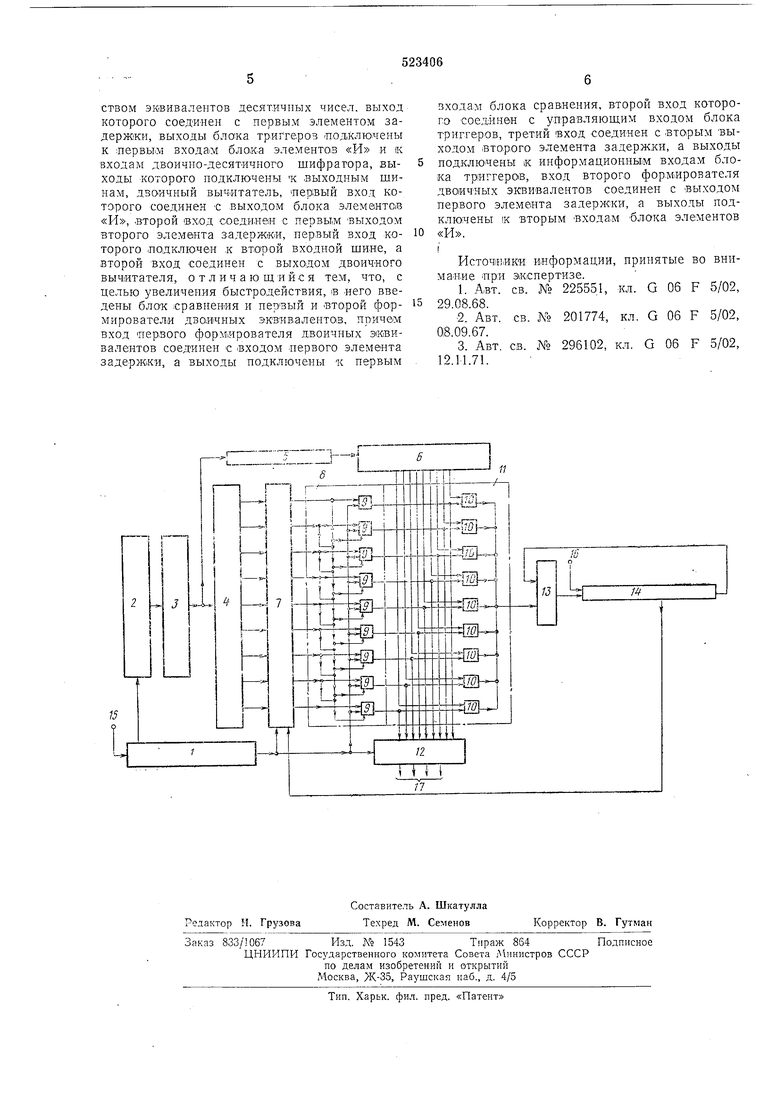

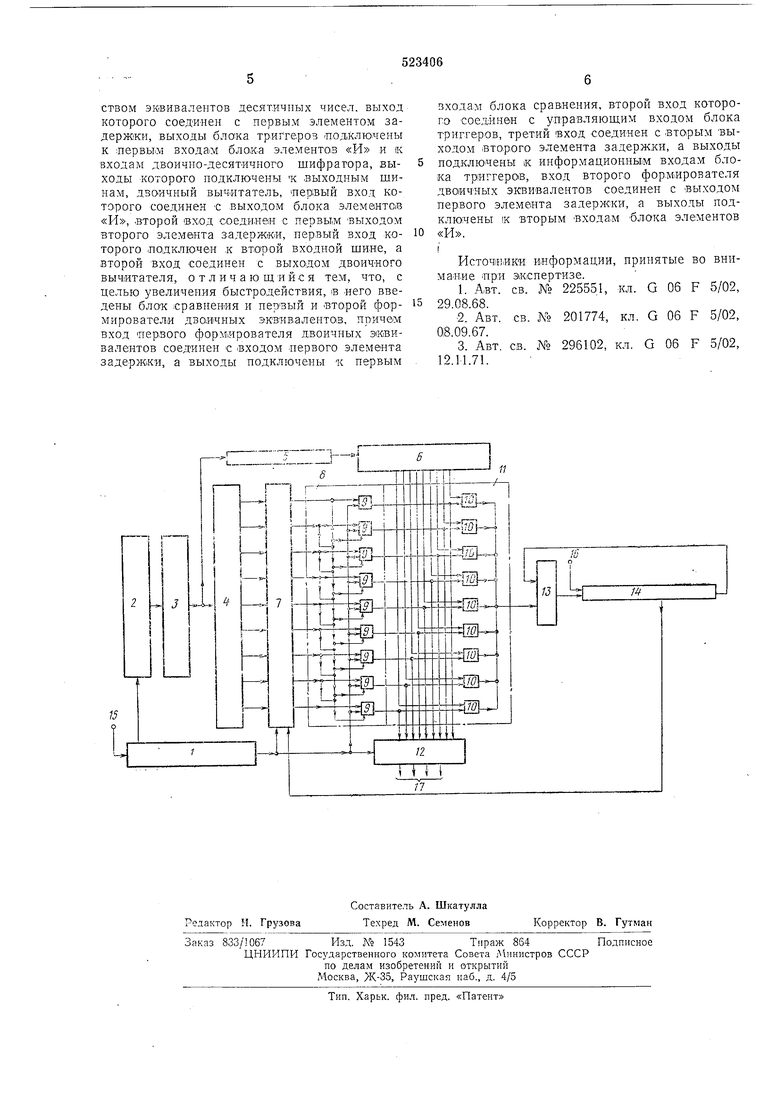

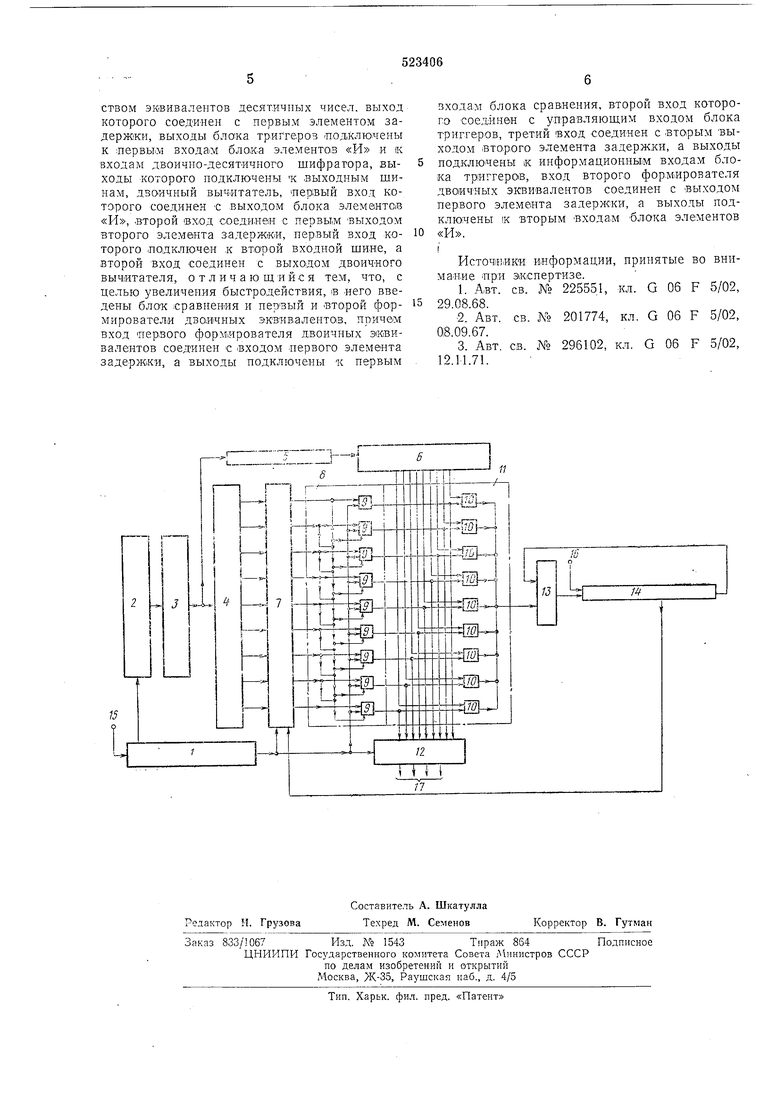

На чертеже представлепа блок-схел1а преобразо-вателя.

Преобразователь содержит блок / управления, атереключатель 2 эквивалейтов, запоминающее устройство 3 экзивалентоБ десятичпых чисел, первый формирователь 4 двоичных эквивалентов, первый элемент 5 задержки, второй формирователь 6 двоич.ных эквивалентов, блок 7 сравнения, бло,к 5 триггеров, состоящий из триггеров 9, элементы «И 7(9 блока J1, двоИчно-десятичиый гаифратор 12, двоичпый вычитатель 13, второй элемент 14 задерЖКи, первую 15 и вторую 16 входные щины, выходную ши.ну 17.

Работает преобразователь следующим образом.

По 1входпой шине 15 на устройство поступает управляющий имлульс, запускаюпщн блок / управления, жоторый начинает вырабатывать импульсы, необходимые ,для автоHOMiHoro фунг-сционирования преобразователя.

Одновременно .по входной щине 16 последовательно поступает исходное двоичное число А, -подлежащее преобразованию. Циркуляционный регистр, образованный элементом 14 задержки и одноразрядны.м вычитателем 13. обеспечивает хранение и выдачу на третий вход бло1ка 7 сравнения .исходного двоичного числа А, а далее - частичных разностей AJ. На Первый вход схем .сравнения блоха 7 в каждом цикле одновремеиио подаются девять двоичных э.квявалентов десятичных чисел вида: Bij (bi- 10 + )э.

Эти эквиваленты вырабатываются форм.ирователем 4 из эквивалентов вида (, хранящихся в запо минающем устройстве . Выборкой этих эквивалентов упра1вляет перВключатель импульсов. В исходном положении этот переключатель установлен на выборку макоимально.го двоичного Эквйвалента. Затем возбуждаются щины .меньщ.их по алгебраической величине эжвИваленто В. Последовательность .выдачи Эквивалентов определяется значениями k: для лравильных дробей -1; -2; -3; ...; -k, для целых чисел k; (k-1); (k-2); . .. ; О, для смещанных дробей /; (/-);...; 0;-а;-2;...;-/.

Применение формирО|Вателей позволяет использовать заиоминающее устройство 3 меньшей емкости. Она определяется количеством разрядов k преобразованпого десятичного числа. В противном .случае емкость ЗУ необходимо было бы увеличить иа порядок. Во столько же возросло бы и время преобразования.

С помощью блока 7 определяются те двоИчные эквиваленты, для которых справедливо

неравенство Л/ BIJ, где / - определяет номер десятичного разряда; а i - десятичную цифру f6i I, 2, ..., 9).

Бло1к 7 для КОДОВ, при которых удовлетворяется указа.иное условие, вырабатывает импульсы, поступающие иа и;нформащион нь:е входы соответствующих триггеров 9 блола 8. Однако пр.и этом запускается только.один, самый старший по весу, триггер, поскольку выходы блока 7 связаны с запускающими входа;ми триггеров 9 того же веса и с запрещающими входами более низких по весу триггеров..

Тот триггер, который переходит в состоя5 ;ние запуска, подготавливает одноименный элемент «И 10 блока элементов «И, обеспечив прохождение через него выбранного двоичного эквивалента S,-j, поступаюи;его от формирователя 6, пол.ностью идентич;ного форми0 рО|Вателю 4. Необходимая задерЖ1ка двоичного эквивалента (10-)э до конца цикла, 1пока не будет известен результат сра.внения, осуществляется элементом 5 задержки. Выбранный зкв.ивалеит S,- удовлетворяет приведбинаму условию, следовательно, операция вычитания |ИЗ его числа Л (а далее - из часТИЧ1НОЙ разности AJ) .возможна. Вычитание осущ,ествляется с помощью одноразрядного двоич-ного вычитателя 13.

Сигналы соответствующего триггера блока 8 поступают также и на двоично-десятичный шифратор 12, осуществляющий преобразование десятичного кода цифры в двоичло-десятичный код тетрады, .снимаемой с выходной щ.И1НЫ -.17.

Указанные нреобразования повторяются в последующих циклах, в результате которых формируются очередные тетрады иреобразуе0 мого Числа. При этом возможны два случая: преобразование заканчивается через k циклов (по числу k десятичных разрядов):

преобразование заканчивается раньше, а Именно в том цикле, как только блок сравне5 ния зафиксирует ра.венство кодов AJ Б;,-.

Введение оз схему преобр;азователя двух формирователей двоичных эквивалентов и блока сравнения выгодно отличает предлагаемый преобразователь двоичных ч.исел в двоич.но-десятиЧНые ОТ-указанного «прототипа, так как уменьщается необходимое количество ц,иклов преобразования (в 10 раз). В результате возрастает быстродействие рассматриваемого устройства. 5

Формула изобретения

Преобразователь двоичных чисел в двоично-десятичные, содержащий блок уир.авления,

0 вход которого подключен к первой входной шине, первый выход соединен С уи.равляющиМИ входами блока триггеров и двоично-десятичного щ.ифратора, а второй выход подключен к Переключателю эививалентов, выход

5 которого соединен с запоминающим устройством эквивалентов десятичных чисел, выход которого соединен с нервым элементом задержки, выходы блока триггеров .подклю:чены к лервЫМ входам блока элементов «И и к входам двоично-десятичного шифратора, выходы которого нодключены к выходным шинам, дваичный выч.итатель, нервый вход которого соединен € выходом блока элемвнт&в «И, .второй вход соедннея с первы1М выходом второго элемента задержки, нервый вход которого лодключен .к второй входной шине, а второй вход соединен с выходом двоичного вычитателя, отличающийся тем, что, с целью увеличения быстродействия, в «его введены блок сравнения и нервый и второй формнрователи двоичных э,квив:алентов, причем вход Первого формирователя двоичных эквивалентов соединен с входом первого элемента задержки, а выходы подключены к первым

входам блока сравлення, второй вход которого соединен с управляюш;им входом блока триггеров, третий вход соединен с вторым выходом второго элемента задержки, а выходы нодключены к информационным входам блока триггеров, вход второго формирователя двоичных эквивалентов соединен с -выходом первого элемента задержки, а выходы подключены к вторым входам блока элементов «И.

Источники информации, принятые во внимание -при экспертизе.

1.Авт. св. № 225551, кл. G Об F 5/02, 29.08.68.

2.Авт. св. ЛЬ 201774, кл. G 06 F 5/02, 018.09.67.

3.Авт. св. № 296102, кл. G 06 F 5/02, 12.11.71.

/4

77

Авторы

Даты

1976-07-30—Публикация

1973-10-01—Подача