Цель Изобретения - повышение точности работы устройства.

Это достигается путем модключення делателя частоты (КО гаторОМу входу грмтг&ра упраплекия и схеме «И.

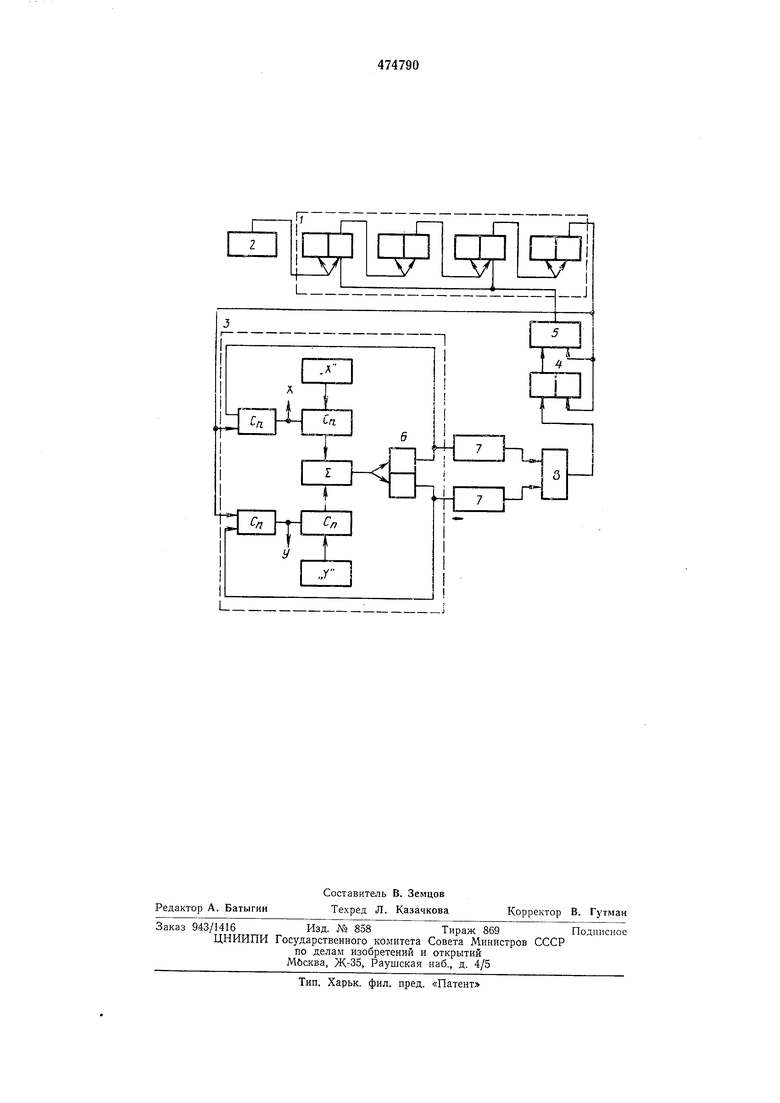

На чертеже .лредсташлена схема предлагаемого устройст ва стаб ил1изации Скорости.

Делитель 7 частоты с переменным коэффициентом деления, .состоящий 1из четьфех т|риггеро:з (iB дянном случае возможно .применение и. большего колИчест1Ба двоичных раЗ|рядов делителя), связан своим счетным входом с блoJcaм 2 задаН1Ия скорости, который представляет собой генаратО|р с двоичным делителем частоты на выхо.де. Каждый из раз1рядоБ делителей бло1ка 2 за:даН ИЯ .скорости объединен на выходе через 1вент1ильяые схемы. Выход делителя / частоты подключен ко .входу Интерлолятора 3, а также ко 1втарому входу триггера 4 управления и схеме .«И 5. Иитерполяфор 3, работающий по спосо.бу оценочиой функции, имеет .на выходе триггер 6 определения знака, подключенный через дифференцирующие блоки 7 1И схемы «ИЛИ 5 к первому входу триггера 4 управления, выход которого через Схему «И 5 :связа« с у1ста;новочны:ми (Входами делителя / частоты lOep.Boro и третьего ра.зрядо(в.

Работа интерполятора 3 построена, как уже указывалось, по способу оцсночиой функщии, в частности по алгоритму Гроссмана.

При .отработке несколгзмих последовательных maroiB ло одной координате интерполятор 3, имеющий в своей о.сеове (Координатные регистры .и сум-матор с последовательным поразрядным (переиосом, ф|о;рми|рует им.пульсы по этой координате с од|ной 1спределен(ной частотой, определяемой частотой На входе интерполятора 3. Делитель / частоты .производит деление частоты следо;ва«ия .И1мпульсо,в, поступающих с блока 2 задания скорости, и усредHeiHMe неравномерн.ости с максимальным коэффищиевтоМ делвн1И:Я Кок 2 16.

При смене координаты, связанной с из.меневием угла наклона обрабатываемой кривой, сигнал с триггера 6 определения знака, изменяется и .появляется на выходе одного из дифференцирующих блоков 7 и далее - на выходе схемы «ИЛИ 8. Этот сигнал переключает триггер 4 у1правлен Ия и запоминается IB 1нем. С этого момента сигнал с триггера 4 yiПpaJBл©ния .присутствует 1на одном из входов схемы «И 5. Однако появление сигнала на триггере 6 определения з.на1ка задерживается относительно /входного сигнала на иитерполятор 5 за счет того, что в неМ применен сумматор с последовательным .поразрядным переносо.м. Это время задержки в интерполяторе 3 на время переноса чисел от младшего раЗ|ряда к старшему каждый раз 5 может быть разным, но оно выбирается таким образом, чтобы его максимальная величина была меньше восьми периодов самой большой частоты следоваяия .импульсов с блока 5 задания скорости.

0 Таким образом, по одному входу схема «И 5 по.дготовлена до Прихода восьмого И1миульса делителя / частоты. С .приходом восьмого импульса «а второй вход схемы «И 5 inpoисходит дополнительного числа «пять, так что :к :пр.иходу девятого импульса в делИтеле / частоты записано число 13 (8-5), следовательно, необходима до.бавка еще трех импульсов. Коэффициент делегаия делителя / частоты уменьшается до Кпк, а появление 1 оследующего .ИМпульса на выходе интерполятора 3 будет происх.одить раньше в

1 f

,45, чем при последовательной обработке нескольких шагов по одной координате. Та.ким образом, ли1кви.дируется ееравномерно.сть подачи, равная ,41, .когтарая указывалась выше, а уареднение входной неравномерност/и происходит с Выходной

0 импульс с делителя / частоты, ло.мимо поступления на интерполятор 3, производит установку трИггера 4 управления в исходное состоя1Н1ие.

Необходимо отметить ряд чисел коэффициентов деления, При .которых возможна работа устройства стабилизащии 16 и //, 32 и 23, 64 И 45 и т. д., пде первый ряд построен по 2. С увеличением числа неравномерность уме.ньшается.

Предмет изобретения

Устройство для стабилизации скорости подачи в станках с /аропраммным управлением,

оодержа.щее линейно-круговой интерполятар, выходы котор.ого через дифферанцирующие бл.оки подк.тючвны ко входу схемы «ИЛИ, выход которой подключен к первому входу триггера управления, выход которого подклю0 чен к первому шходу схемы «И, выход схе.мы «И лодключен ко второму входу делителя частоты, первый /вход которого соединен с выходом блока задания скорости, а выход подключен ко входу линейно-кругового интерио5 лятора, отличающееся тем, что, с целью повышения точности работы устройства, в нем выход делителя частоты подключен ко второ му ВХОДУ тр1иггера управления и схе-мы «И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство контроля для систем программного управления | 1990 |

|

SU1775716A1 |

| Устройство для программного управления | 1984 |

|

SU1218368A1 |

| Круговой интерполятор с оценочной функцией | 1976 |

|

SU638916A1 |

| Система числового программногоупРАВлЕНия "TPACCA-Кп | 1979 |

|

SU813371A1 |

| Устройство для программного управления | 1986 |

|

SU1376065A1 |

| Интерполятор для шагового графопостроителя | 1978 |

|

SU736137A1 |

| Устройство для программного управления | 1986 |

|

SU1317399A1 |

| Линейный интерполятор | 1986 |

|

SU1416940A1 |

| Устройство для двухкоординатного программного управления | 1981 |

|

SU962857A1 |

| ИНТЕРПОЛЯТОР | 1970 |

|

SU272415A1 |

Авторы

Даты

1975-06-25—Публикация

1973-02-09—Подача