средних частот всех указанных устройств, столь велика, что вероятность Р„ (Я, /) наложения п сообщений возрастает до значений, при которых достоверность оценки контролируемого технологического процесса становится ниже допустимой.

Цель изобретения - повышение достоверности собираемой информации.

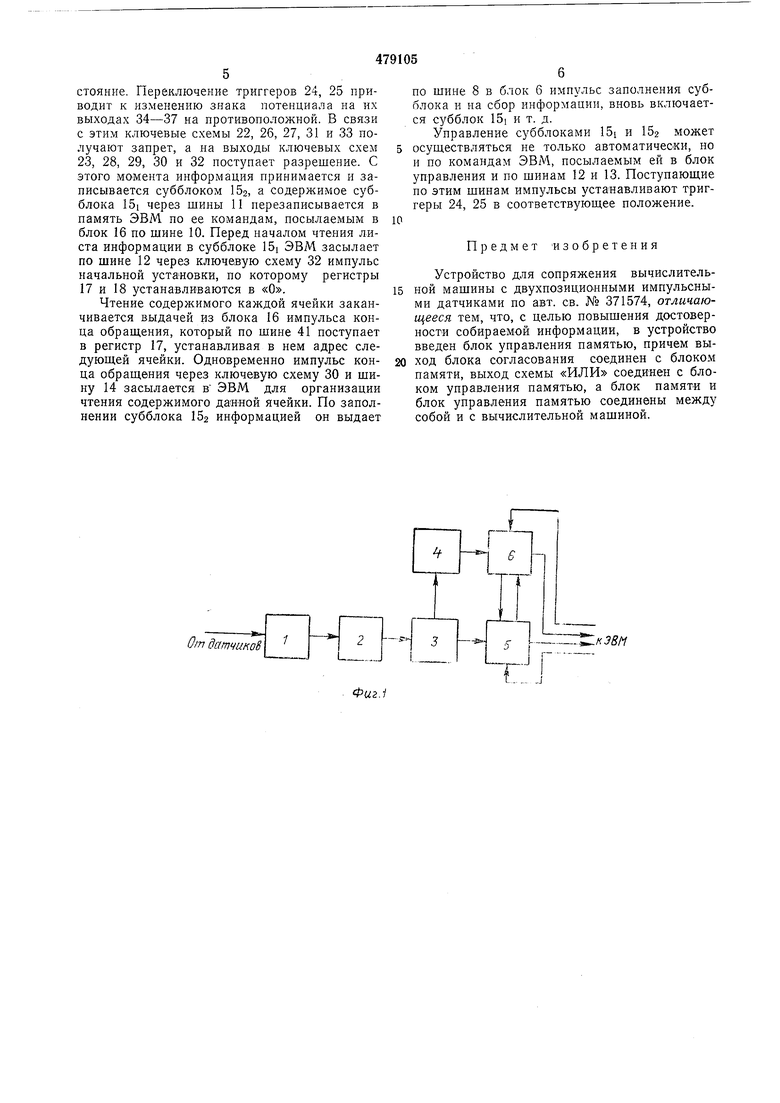

Это достигается тем, что в предлагаемое устройство введен блок управления памятью, причем выход блока согласования соединен с блоком памяти, выход схемы «ИЛИ - с блоком управления памятью, а блок памяти и блок управления памятью связаны между собой и с вычислительной машиной.

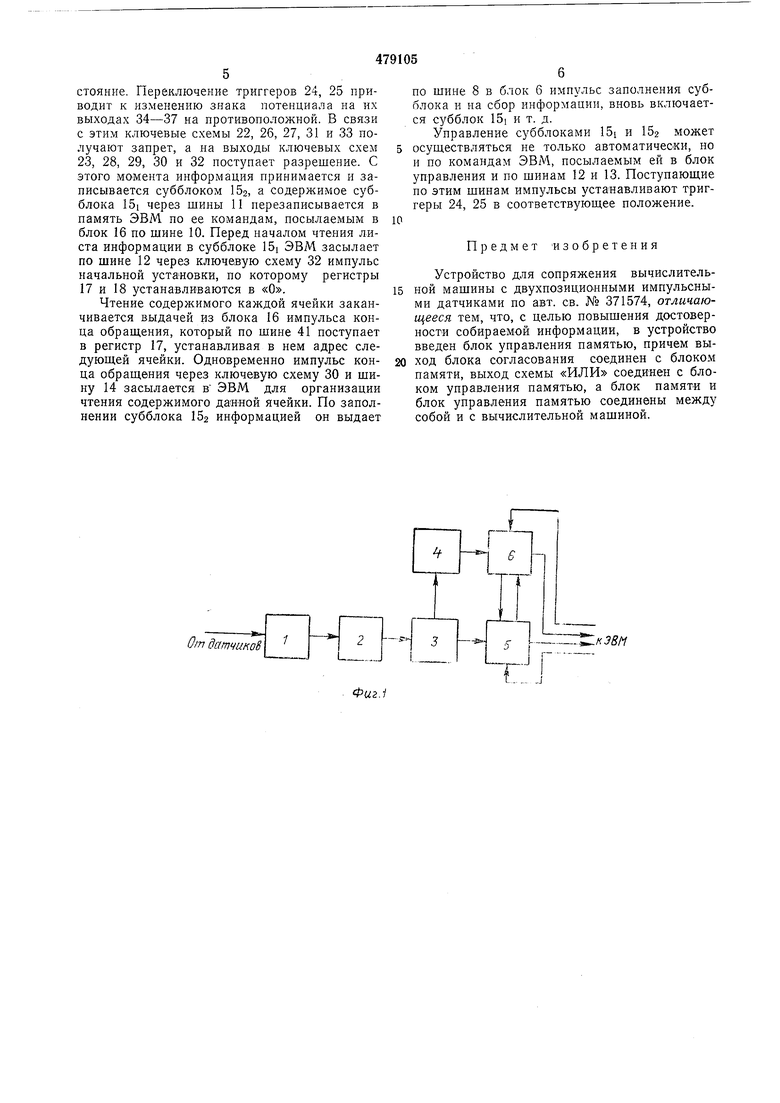

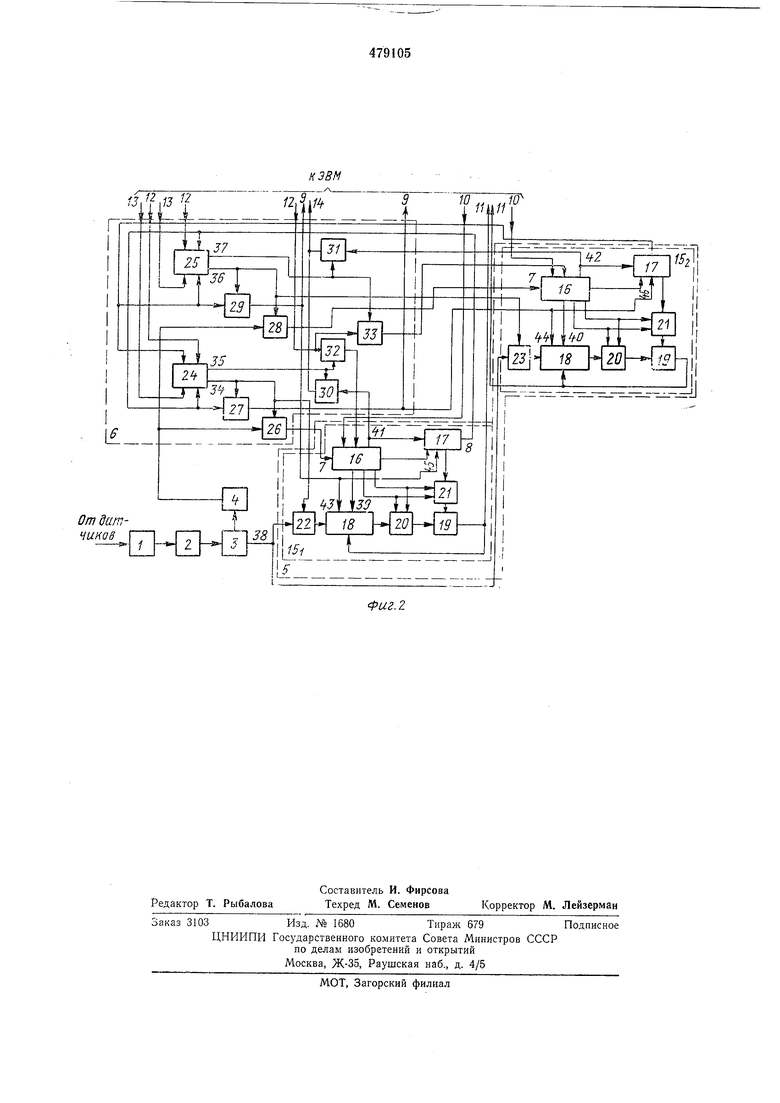

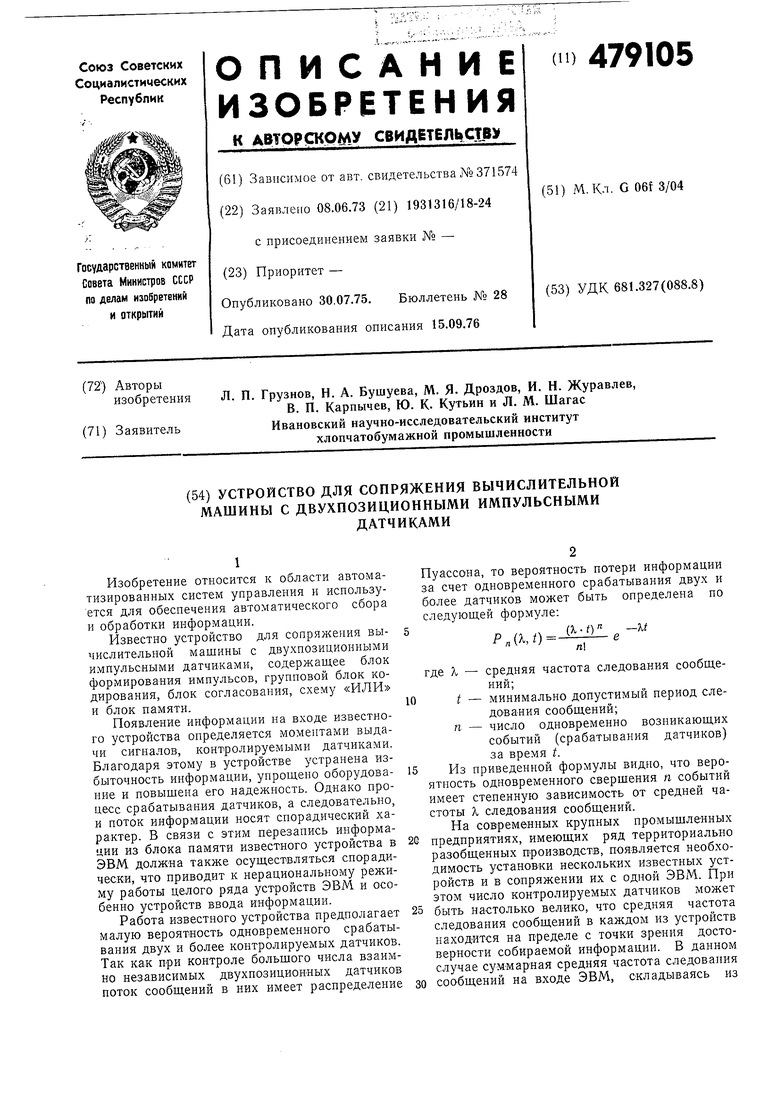

На фиг. 1 показана блок-схема устройства; на фиг. 2 - блок памяти и блок управления памятью.

Устройство содержит блок I формирования импульсов, который формирует импульс достаточно малой длительности в момент срабатывания датчика, групповой блок 2 кодирования, служаш;ий для получения из одиночного импульса кода сообщения и усиления мощности передаваемого сигнала, блок 3 согласования, схему «ИЛИ 4, формирующую импульсы записи информации, блок 5 памяти (накопитель информации, состоящий из субблоков) и блок б управления памятью.

На фиг, 2 приняты следующие обозначения: 7 - шины импульса записи информации, 8, 9 - шилы импульса заполнения субблока памяти, 10 - шины импульсов чтения, II - импульсно-кодовые щины чтения, 12 - шины импульсов начальных установок, 13 - шины импульса конца приема информации, 14 - шина импульса конца обращения, I5i и 15-2 субблоки памяти, 16 - блок местного управления, 17 - регистр адреса, работающий в счетном режиме, 18 - регистр числа, 19 - куб памяти, 20 - управляемый узел, содержащий дешифраторы, формирователи и усилители полуто,ков записи и считывания по разрядным цепям куба памяти, 21 - управляемый узел, но в адресных цепях куба памяти, 22 н 23 - ключевые схемы управления, 24, 25 - триггеры переключения субблоков памяти, 26-33-ключевые схемы управления; 34-37 - потенциальные выходы триггеров, 38-импульсно-кодовые шины информации, 39, 40-шины импульса установки в «О регистра числа, 41, 42-шины импульса конца обращения, 43, 44 - шины импульса начальной установки регистра числа, 45, 46 - шины импульса начальной установки регистра адреса.

Устройство работает следующим образом.

В момент осуществления контролируемого события срабатывает соответствующий датчик, и блок формирования импульсов формирует импульс достаточно малой длительности. Импульс поступает в блок 2, где преобразуется в параллельный код сообщения, состоящий из кода объекта (адреса объекта) и кода признака сообщения (контролируемого параметра). Сигнал, усиленный по мощности, проходит блок 3 и записывается в регистр числа одного из субблоков блока 5. Одновременно сигнал поступает на вход схемы «ИЛИ 4, формирующей из него импульс записи и-нформацин, который направляется блоком 6 в соответствующий субблок памяти и используется в нем для перезаписи содерл имого регистра числа в куб памяти.

По заполнении куба памяти информацией

из блока памяти выдается импульс заполнения соответствующего субблока, который поступает в блок 6. На основании этого импульса блок 6 автоматически отключает заполненный субблок и включает свободный субблок

памяти на сбор информации. Одновременно блок управления памятью выдает в ЭВМ импульс заполнения блока памяти. Получив этот импульс, ЭВМ осуществляет перезапись содержимого заполненного субблока блока памяти в свою память.

Таким образом, блок управления памятью автоматически включает на сбор информации один из свободных субблоков блока памяти, а ЭВМ осуществляет перезапись содержимого

заполнившегося информацией субблока в свою память.

Рассмотрим работу блоков 5 и 6. Исходное состояние схемы задается ЭВМ, которая направляет соответствующие команды по шинам 12 и 13. Примем за исходное такое состояние схемы, при котором на выходе 34 триггера 24 и на выходе 37 триггера 25 имеет место потенциал, дающий разрешение на выходы ключевых схем 22, 26, 27, 31 и 33, а с выходов 35 и 36, указанных триггеров на выходы ключевых схем 23, 28, 29, 30 и 32 подается потенциал запрета. Сообщение с датчиков, преобразованное блоками 1, 2, 3 в параллельный импульс код, проходит шины 38, ключевую схему 22 и записывается в регистр 18. Одновременно свообще-ние преобразуется схемой «ИЛИ 4 в импульс записи информации, который направляется через ключевую схему 26 в блок 16 субблока 15 и превращается в

нем в импульсы перезаписи содержимого регистра 18 в ячейки куба 19 памяти.

В конце числа записи каждого сообщения блок 16 выдает по шине 39 импульс установки в «О регистра 18, а по шине 41 - импульс

конца обращения в регистр 17 адреса, работающий в счетном режиме. Этот импульс используется в нем для установки адреса следующего сообщения путем увеличения содержимого регистра на единицу. По заполнении

последней ячейки куба памяти на выходе регистра 17 появляется импульс заполнения субблока памяти, поступающий по шине 8 в блок управления памятью и производит переключение триггеров 24, 25. Одновременно импульс

через ключ 27 записывается по щине 9 в ЭВМ и служит сигналом о заполнении куба памяти субблока 15i.

Импульс по шинам 44, 46 направляется также в субблок 152 для установки регистров адреса и числа этого субблока в начальное состояние. Переключение триггеров 24, 25 приводит к изменению знака потенциала на их выходах 34-37 на противоположной. В связи с этим ключевые схемы 22, 26, 27, 31 и 33 получают запрет, а на выходы ключевых схем 23, 28, 29, 30 и 32 поступает разрешение. С этого момента информация принимается и записывается субблоком 152, а содержимое субблока 15i через шины 11 перезаписывается в память ЭВМ по ее командам, посылаемым в блок 16 по шине 10. Перед началом чтения листа информации в субблоке 15i ЭВМ засылает по шине 12 через ключевую схему 32 импульс начальной установки, по которому регистры 17 и 18 устанавливаются в «О.

Чтение содержимого каждой ячейки заканчивается выдачей из блока 16 импульса конца обращения, который по шине 41 поступает в регистр 17, устанавливая в нем адрес следующей ячейки. Одновременна импульс конца обращения через ключевую схему 30 и шину 14 засылается в ЭВМ для организации чтения содержимого дайной ячейки. По заполнении субблока ISa информацией он выдает

по шине 8 в блок 6 импульс заполнения субблока и на сбор информации, вновь включается субблок 15i и т. д.

Управление субблоками 15i и 152 может осуществляться не только автоматически, но и по командам ЭВМ, посылаемым ей в блок управления и по шинам 12 и 13. Поступающие по этим шинам импульсы устанавливают триггеры 24, 25 в соответствующее положение.

Предмет изобретения

Устройство для сопряжения вычислительной машины с двухпозиционными импульсными датчиками по авт. св. № 371574, отличающееся тем, что, с целью повышения достоверности собираемой информации, в устройство введен блок управления памятью, причем выход блока согласования соединен с блоком памяти, выход схемы «ИЛИ соединен с блоком управления памятью, а блок памяти и блок управления памятью соединены между собой и с вычислительной машиной.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления оперативным накопителем | 1977 |

|

SU656106A1 |

| Устройство для сопряжения ЭВМ с каналом связи | 1988 |

|

SU1656544A1 |

| Устройство для отладки программно-аппаратных комплексов | 1990 |

|

SU1795464A1 |

| Логический анализатор | 1988 |

|

SU1654822A1 |

| Станция локальной сети | 1987 |

|

SU1478221A1 |

| Устройство для сопряжения процессора с группой устройств памяти | 1986 |

|

SU1348843A1 |

| Устройство для функционального контроля цифровых блоков | 1989 |

|

SU1656538A1 |

| Устройство тестового контроля | 1989 |

|

SU1691842A1 |

| Устройство для сопряжения двух ЭВМ | 1988 |

|

SU1596341A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1988 |

|

SU1536392A1 |

w датчикоК

LкЗВП

Авторы

Даты

1975-07-30—Публикация

1973-06-08—Подача