Ipiirrcpa (|4i,vc;i;i,;ii: rcn:i 1,ч,,м1 о.лжа f;uiX:M),;tia,.i ,i, i;i..|);4i lii.iA

CGC;l,iiiiL-H l.i i;iu)ii c;i . ,L,- :п ;l,;i I

BlopbiM iiXo, .,1:с.1: iiori) J:L: ;: ,: ;:a ; j,:eAiC:i ; «h/;.

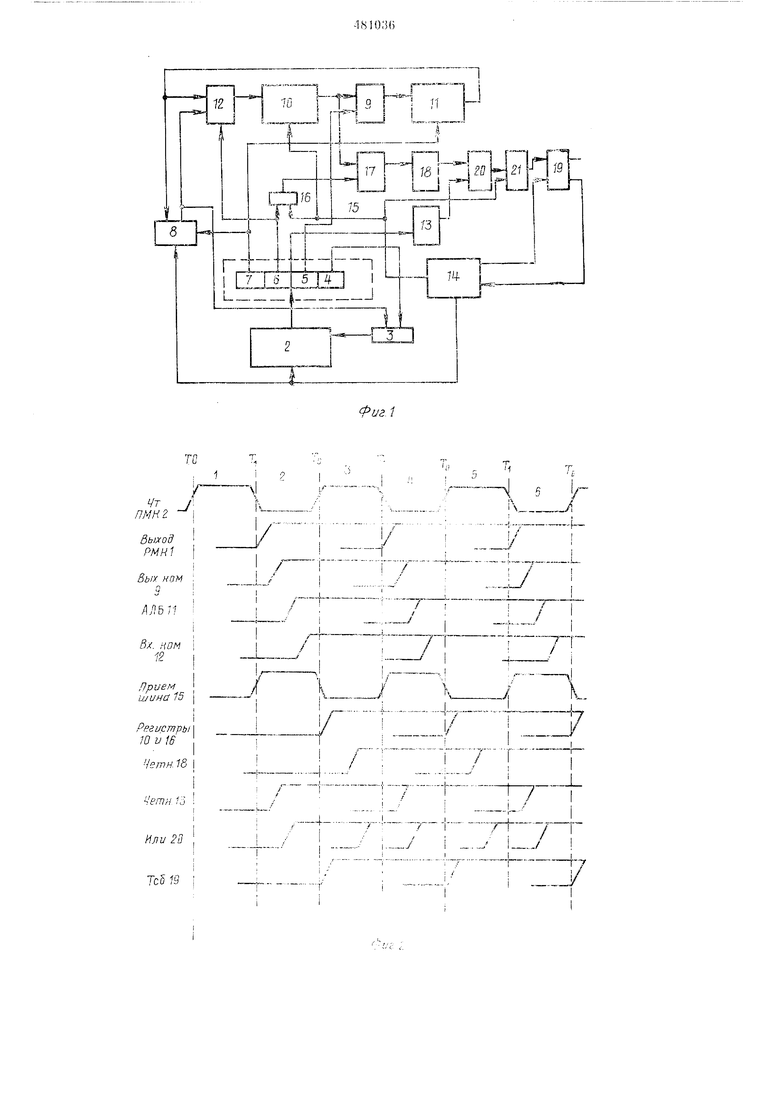

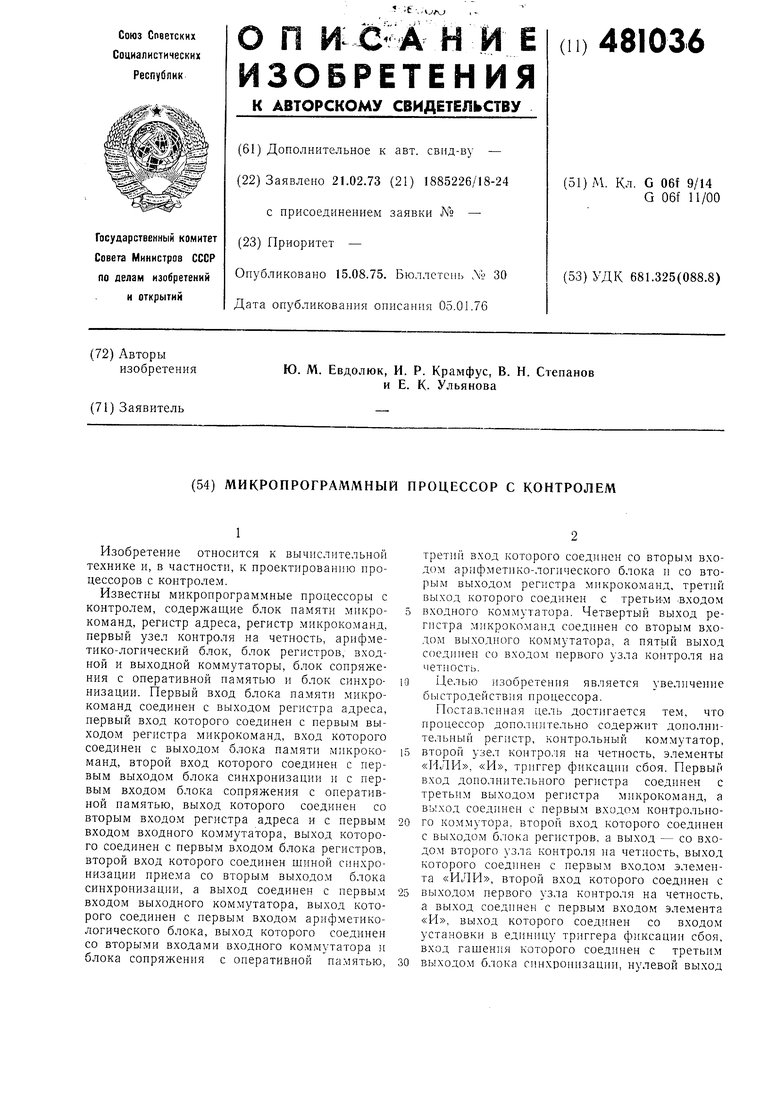

liji фиг. i iipiMK.;,oii;. 6.1;,;-, схема .;

сора.

1рел.1а1асмып iipoue.JCir) /о.чор.ка: |ч;.:1.:) м;1Кр;)К()маид i, блок ;амяп ма.лл,;у()л;а:;д :.. rieriiCTp а;.реча о, a.i)eca)o по.Ч . pi. :-1:ат;)а ; i:iKpo:-;n ; i ад, iia.ic 151)1дача i: ро1а;..т:;а . команд, оле лрасма i) j cri;; jpa :. ;K)ai.ir.-a;;.-;,, иоле хода V и1Хр;)ко: ;а;;ДЛ1 pe;i;ei|)a viaxpvК1)ма11д, блок еаприжения с олерачаа::;; наМЯТ1ЛО 8, )Ь ХодиО 1 ;)м ivгато;) 9. б,д.)К регастров 10. арисЬмепп о-.югичеелШ: о,:,ок ii. входной KOMMviaiOp 12, iicpisijiis уаел 1) ajai jio.i/i на MeTuocib, б/кж сдахр;); aiaiiaa 1-i. aiaиы ciiuxpoaaaaun;) приема lo, до1И,1а1гсл,ПЛ: jieriiCTp 16, Koin po, K:).i M татор i7, ьгаpoii узел контроля s-n ч чпоеч:; Н, -ipanep (;пкеаннн еОсл IH. - леменл «ИЛИ 20 а :.кмент «S-i 21.

Работа процеесо|)а он:)едсляс1Чя с;)д,с,Л1 имым periiiMpa мшчрохомапд ;, в AOTi.ipijiii ;;;, б/фаютси макрокоманд) а.; блока паля га микро сомапд 2. .Лдрее liamapaeMO: .viaxpoкоманды онреде.чиется содор камь;м регаетра адреса 3, которыд устанав.шнастея и:; адресного ноля 4 региетра микрокоманд 1.

11ачал1Л1Ын адрес ма1)онр(.1гра лпл,| иыл(;,1Н-2ННЯ команды устааавльизаеген а per; егле адреса 3 после вкборкл кода колллДЫ а.; оаерагивно намяги с 1омо1дь о б.юха coiii ;-;; eння с ouepaTUBuoii 11амят)К) о. i 11.1авнльпоет1 выборки макрокоманд в peracrj ( 1 коитро,Ч| руетея первым у.лко контр;),;;: аа четность 13.

Через выход1 011 ч i i i i i 113 любого региетрс о i ре i i i ll о i быть нередана на ь о ji | i i i ГО блока 11, в кои рим i i

подается на в.ход L л i i i ii

С выхода ьходно о i i iii

нередаетея в люби p н i P i

ров 10.

ПооТе выдачи о peiaiei pa микоокс лллм, ; определяет помер регистра из б,()ка рсгксгров 10, содержимое которого подк.лоааетея 1Л) входу выходного KOMMyraiOjia 9. Поле л|)ле ма 6 регистра макрокоманд 1 он.) регистра, иа вход которого через 5ход,01| коммутатор 12 пр1Л1амаетс:: аафо|)ма :л:я с выхода ари(1зметико-.тог11ческого блока ; i н.па с выхода б,1ока сопряжения с оа(Г))н i:aу-ятыо 8.

Поле кода микрокомаддь; 7 рс;;.;,-,: ..ixp()комаид 1 оирсделяет тип )аа.а;;, aijiiujaнясмой арифметико-логнчеек1;м 6;iOi OM 11. а блоком сопряжения с онератив1 0н аамят;л; 8. В арифметико-логическом б/юке 1 1 ;и,1а:;,1пяютея онерации сложения, выантання, лагнчеекие преобразования кодов сдзап: а аередачи ииформаиии.

мчаслюз (). аjjejo )аа аотея в

: I. б- юке 1 i а возвраре: :етров Ui.

.аа;аа;л;х аа(|)0рма1 ии в apji(j):л;.1 6,-;(iKc 1 Bceivia доиолия;;1П. i 1Н1рорма1Л5я в оиератив.лч/кс доао. iuciia е помощью

;а.;ря,Тс ДО lie ieTHOH.

,:м. iijia о rev rcTDHH ебое1 со. r:i:ii5 6.-;. ;)craciaio;i 10 iicci

.la ачее -:о1Ч; блока И. преобразования и иод.хл:;лкааи |Нф(.)рмаиаи ; выходам входного г.а,1 i . а 1Ч;ра 2. блок са1нхроннзап,пи 14 выjiaua eai пал iia шине сипхроиизаиии а люлЛ: К), i 1:;е1)бразона11пая ; ирормация а а:;аал.,е1 я в бло1 оегпетров 10, а еодержил:д; ааля и peiaieipa микрокоманд 1 1е;ед,.:е :ся з д ;a;JЛHll; е, регнетр 16. При 1 i 1 лл X зых;.Ду (;,11лк}го комл1утатора 17 аа,л.,.:(1аастея eo.iep KiJMoe того региетра бло.va per,Л .-роз К:, i ivcnopbiii была ир;1пята rui: кон-)оля па четность 18 пронлюсть инфор: 1анли на выходе )л1мутатора 17 и вырабатываин(|)орма1лл; па выходе сигнал, сл:я па исрвый вход .темеита

од элеме1гга «ИЛИ 20 подан а уз.ча 13, который контродиHiaojiMamiii в регпетре микроал е элемента «ИЛИ первый вход Ь1лемеита «И 21, KOTopoixo нодаетея сиихроиизи е И1ННЫ еипхронизации пр.иемента «И 21 воздействует на в единнцу тр 1ггера фиксации le еднниды на выходе триггеЗоя б.юкирует работу б.тока i, н процессор оетанавливаjii диаграмме принято (см, :таноз1ча )егис1ров и триггеров тему фронту сиихроиизи.leiieiByiOHU-ix на их вхо нуиктирными .тиниями процессора, а сплогимым) Ями - моменты измене|-|5егстнуюп1их регистров и

л хроиизаннн 14 вырабатывает сигя очеред1:ой микрокоманды из блоi М11кр()хома11д 2, По окончании пер.; ч;епия на В1з1ходе регистра микроуе 1л аа15лаваются состояния, соотUic ечитан1:сй ,1акрокоманде. в следующем птором такте иромсхол.ит передача информации через выходной коммутатор 9 в арифметико-логический блок 11, ее преобразование в соответствии е тином микрокоманды и подключение через входной коммутатор 12 ко входу блока регистров 10. К концу второго такта уста ;овитея также состояние узла 13. контролнруюи1.его четность информацнн в регистре микрокоманд 1. Во втором такте блок сиихронизаини 14 вьшабатывает сигнал на шиие синхронизации ириема 15, по заднему фронту которого результат выполнения микрокоманды записывается я соответствующий регистр, устанавливается дополнительный регистр 16, а также уетанавливается в единичное состояние триггер фиксации сбоя 19, если узел 13 обнаруж л в регистре микрокоманд 1. В третьем такте возбуждается сигнал чтения следующей микрокоманды нз б.юка памяти микрокомаид 2. Одновременно с следующей микрокоманды в соотве- ствии с содержанием дополнительного регистра 16 к контрольному коммутатору 17 подключится тот регистр, в который был принят результат выполнения текун1,ей микрокоманды, и узел 18 проверит этот результат на четность н вырабатывает соответствуюндий сигнал иа своем выходе, который через элемент «ИЛИ 20 поступает иа вход элемента «И 21. По окончании третьего такта новая микрокоманда принимается в регистр микрокомаид 1. В четвертом такте выполняется новая микрокоманда и по заднему фронту сигнала на шнне синхроннзании приема 15 ее результат принимается в один из регистров блока регистров 10. По заднему фронту сигнала на шине снихронизации приема 15 npi налимП сигнала ебоя на выходе элемента «ИЛИ 20 через элемент «И 21 пронсходит устатшвка в единичное состоянне триггера фиксации сбоя 19, который блокирует работу б тока синхронизации 14, и процессор ири останавливается. Если сбой не зафиксирован, в пятом также происходит вр,уборка очередной микрокоманды, а в HiecTOM также ее выполнение. Кполе того, в шестом такте ппоизводится коитполь выборки этой мцкрокомаид в регистр гикр(1команды 1 и контроль выполнения предьдушей микрокоманды и т. д. Как видно нз временной диаграммы, контроль выполнення текущей микрокомацды совмеи1,еи по времени с чтением и выполнетшелт следуюп1ей микроколтанды. Благодаря этому совмещению выиолиение каждой микрокомаиды осун1ествляется за два такта, и цикл работы процессора также составляет два такта. .Миклоирограммпый Ilioneccop с контролем, содержаиип ; блок иамити мнкрокоманд, регистр адпеса, регистр микрокоманд, первый узел контроля на четность, аригометико-логический блок, блок регистров, входиой п выходцой коммутаторы, блок сопряжения с оперативной памятью ц блок сццхронизании, причем первый вход блока памяти микрокоманд соединец с 15Ь1ходом регистра адреса, первый вход которого сосдццен с цервьпт выходом регистра микрок-эмаид. вход которого соединен с выходом блока памят микрокоманд, второй вход которого соединен с нервым выходом бло1-;а синхронизации и с первым входом блока сопряжеиия с оперативной па тятью. выход которого соедтшеи со вторым входом регистра адреса ц с первым входом входцого коммутатора, выход которого соединен с цервым входом блока регнстров, второй вход которого соедннен шиной сиихронизации приема со втопым выходом блока с п хроннзации, а выход соедииеи с первым входом выходного коммутатора, выход которого соедннен с первым входом арифметико-логического блока, выход которого соединен со вторыми входами входного комлптатора и блока сопряжения с оперативной памятьгО, третий вход которого соединеи со вторым входом арифметико-логического блока и со вторым выходом регистра микрокоманд, тпетий выход которого соедицен е третьим входом входного коммутатора, четвертый выхо.д регистра микрокоманд соедшен со вторым входом выходного коммутатора, а пятый втлход со входом первого узла контроля на четность, отличаюи, и и с я тем, что, с целью новышения быстродействия цпоцессора, он дополнительтю содержит дополнительный регистр, котттрольный коммутатор, второй узет ко 1троля на четность, элементьт «ИЛИ--. «И, тпиггел фиксаииц сбоя, причем епвый вход дополнительного регистра оедииет с третьим выходом регистра гикто1-:омапд, а выход соедииец с первым вхоло контрольного комм татора, второй вход которого соединен с выходом б.тока репстррв. а выход - со входом второго контро;:я на четность, выход которого с(1единсн с пепвхм хододт элемента «ИЛИ, В111ХОД которого соединен со входом становки в единиг1 триггепп d1икcaции сбоя, гашения которого с трсгьим выходом блока cinixjif- M TaiuiH, а 1-1уленой выход триггепа (Ьиксац;1и сбоя соединен со входом б,тока синхроннзяцпи. второй выход которого соединен Н1ИИОЙ сиихпоцизан.ии приедта со вторыми входалг доподцительиого регистра н э.темен-а «И-

I

.4

LI

,

/U I,

Ti

--Y -s- -

Ti

t

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммный процессор | 1972 |

|

SU474008A1 |

| Микропроцессор с контролем | 1981 |

|

SU1016788A1 |

| Микропрограммный процессор с восстановлением при сбоях | 1977 |

|

SU656066A1 |

| Микропрограммный процессор | 1974 |

|

SU535567A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1310818A1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1386998A1 |

| Арифметико-логическое устройство | 1977 |

|

SU693368A1 |

| ОТКАЗОУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1986 |

|

SU1400326A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Мультиплексный канал | 1984 |

|

SU1167613A1 |

Авторы

Даты

1975-08-15—Публикация

1973-02-21—Подача