(St) ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Логическое запоминающее устройство | 1979 |

|

SU790017A1 |

| Устройство для сложения чисел в модулярной системе счисления | 1986 |

|

SU1322278A1 |

| Запоминающее устройство с само-КОНТРОлЕМ | 1979 |

|

SU809398A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Устройство для определения медианы случайного процесса | 1990 |

|

SU1718233A1 |

| Устройство для умножения комплексных чисел | 1986 |

|

SU1388851A1 |

| Анализатор спектров | 1982 |

|

SU1023341A1 |

| Многофункциональное запоминающее устройство | 1972 |

|

SU458037A1 |

| Устройство для деления в системе остаточных классов | 1983 |

|

SU1141400A1 |

| Устройство для формирования спектров с постоянным относительным разрешением по направлениям | 1984 |

|

SU1229775A1 |

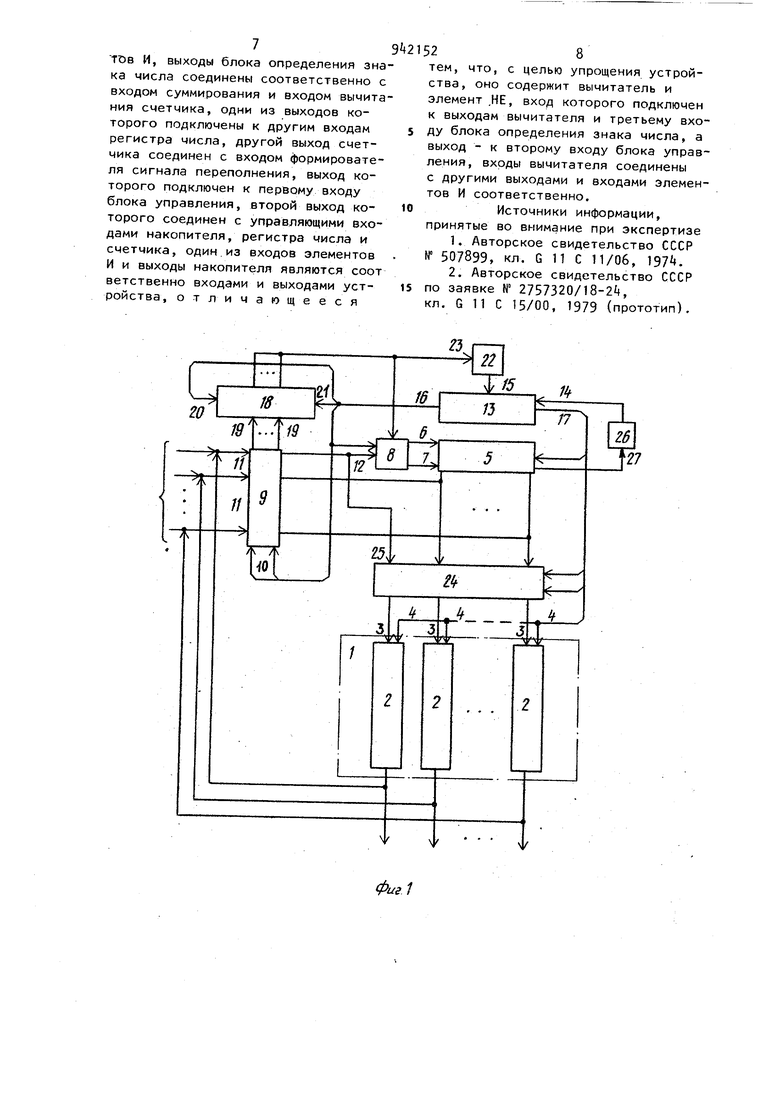

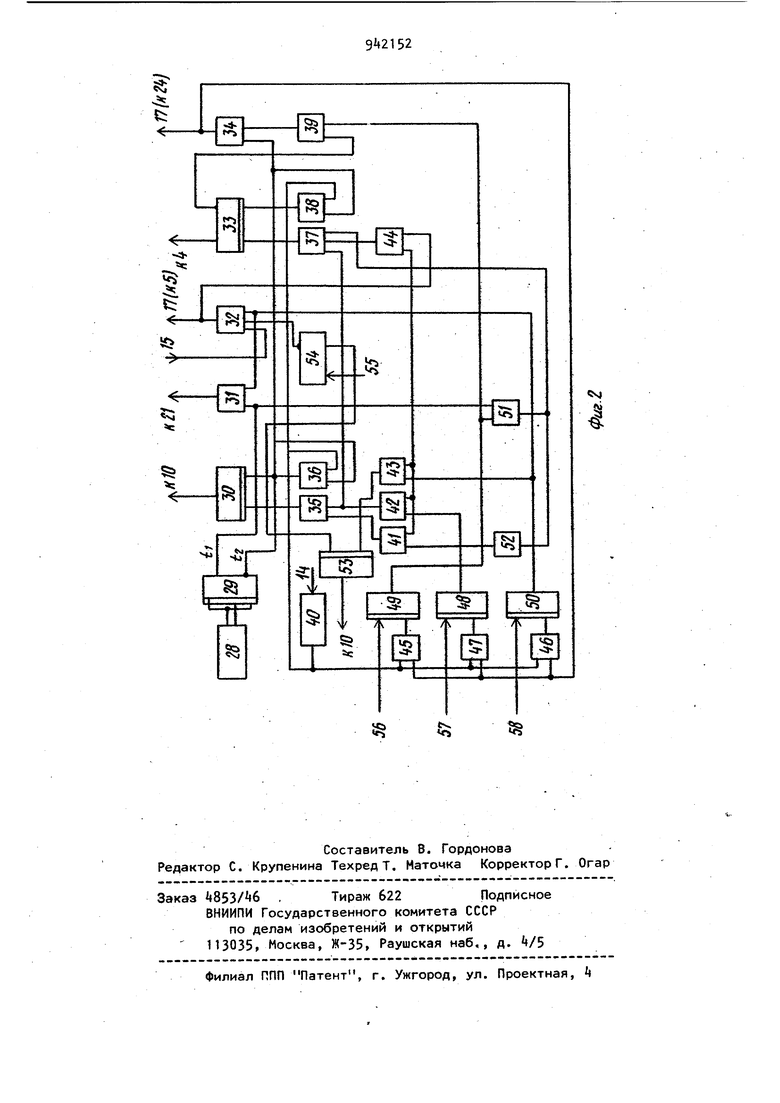

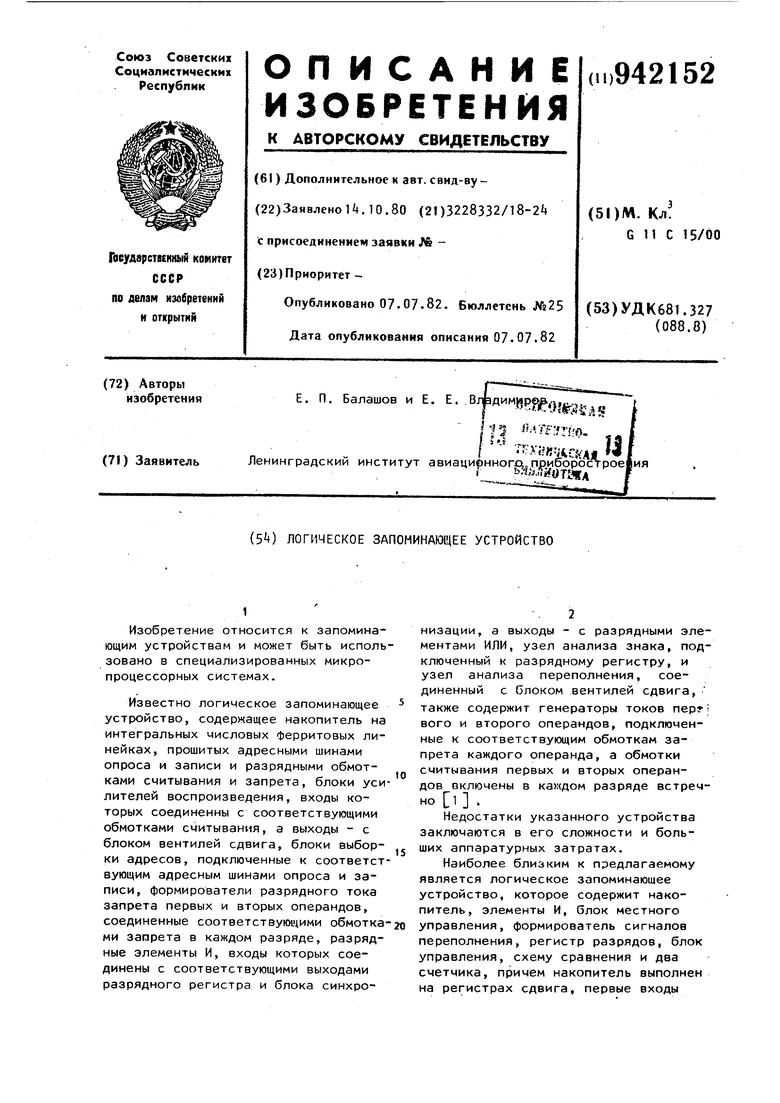

Изобретение относится к запоминающим устройствам и может быть исполь зовано в специализированных микропроцессорных системах. Известно логическое запоминающее устройство, содержащее накопитель на интегральных числовых ферритовых линейках, прошитых адресными шинами опроса и записи и разрядными обмотками считывания и запрета, блоки уси лителей воспроизведения, входы которых соединенны с соответствующими обмотками считывания, а выходы - с блоком вентилей сдвига, блоки выборки адресов, подключенные к соответст вующим адресным шинами опроса и записи, формирователи разрядного тока запрета первых и вторых операндов, соединенные соответствующими обмотка ми запрета в каждом разряде, разрядные элементы И, входы которых соединены с соответствующими выходами разрядного регистра и блока синхронизации, а выходы - с разрядными элементами ИЛИ, узел анализа знака, подключенный к разрядному регистру, и узел анализа переполнения, соединенный с блоком вентилей сдвига, также содержит генераторы токов пер вого и второго операндов, подключенные к соответствующим обмоткам запрета каждого операнда, а обмотки считывания первых и вторых операндов включены в разряде встречно l . Недостатки указанного устройства заключаются в его сложности и больших аппаратурных затратах. Наиболее близким к предлагаемому является логическое запоминающее устройство, которое содержит накопитель, элементы И, блок местного управления, формирователь сигналов переполнения, регистр разрядов, блок управления, схему сравнения и два счетчика, причем накопитель выполнен на регистрах сдвига, первые входы 3 которых подключены к соответствующим выходам регистра разрядов, вторые входы соединены с вторым выходом блока управления, а выходы подключены к выходам накопителя, первые входы элементов И соединены с входными информационными шинами устройства и выходами накопителя, вторые входы - с первым выходом блока управления и первым входом блока . Местного управления, второй и третий входы которого подключены соответственно к первому входу блока управления и к первому выходу элементов И и к одному из входов регистра разрядов, вторые выходы элементов И сое динены с входами первой группы регистра разрядов, вторые выходы элементов И соединены с входами первой группы регистра разрядов, входы второй группы которого подключены к второму выходу блока управления и пе вому входу формирователя сигналов переполнения, выход которого соединен с вторым входом блока управления, первый вход первого счетчика подключен к первому выходу блока управления, второй вход - к третьему входу блока управления и первому вы ходу схемы сравнения, второй выход которой соединен с вторым входом блока местного управления, а первый и второй входы подключены соответственно к третьим выходам элементов И и выходам первого счетчика, выходы блока местного управления соединены с суммирующим и вычитающим входами второго счетчика, другой вход которого подключен к второму ВЫХОДУ блока управления, один из вы ходов второго счетчика соединен с вторым входом формирователя сигнало переполнения, а другие выходы - соответственно с входами первой групп регистра разрядов 2. Недостатком известного устройств является его относительная сложност и большие аппаратурные затраты. Цель изобретения - упрощение уст роиства. Поставленная цель достигается тем что в логическое запоминающее устрой ство, содержащее накопитель на регистрах сдвига, счетчик, блок опр деления знака числа, элементы И, блок управления, формирователь сигнала переполнения и регистр числа, выходы которого подключены соответ24ственно к информационным входам накопителя, выходы которого подключены соответственно к одним из входов элементов И, одни из выходов которых соединены соответственно с входами регистра числа, первый вход блока определения знака числа подключен к одному из входов регистра числа, второй вход - к первому выходу блока управления и другим входам элементов И, выходы блока определения знака числа соединены соответственно с входом суммирования и входом вычитания счетчика, один из выходов которого подключены к другим входам регистра числа, другой выход счетчика соединен с входом формирователя сигнала переполнения, выход которого подключен к первому входу блока управления, второй выход которого соединен с управляющими входами накопителя, регистра числа и счетчика, один из входов элементов И и выходы накопителя являются соответственно входами и выходами устройства, введены вычитатель и элемент НЕ, вход которого подключен к выходам вычитателя и третьему входу блока определения знака числа, а выход - к второму входу блока управления, входы вычитателя соединены с другими выходами и входами элементов И соответственно. На фиг,1 изображена функциональная схема предлагаемого устройства; а на фиг, 2 - то же, наиболее предпочтительный вариант выполнения блока управления. Устройство содержит 1 фиг. 1) накопитель 1 на регистрах 2 сдвига с информационными 3 и управляющими входами, счетчик 5 с входами суммирования б и вычитания 7, блок 8 определения знака числа, элементы И 9 со входами 10 и 11, и одним из выходов 12, блок 13 управления с входами 1 и 15 и выходами 16 и 17, вычитатель 18 с входами 19-2Т, элемент НЕ 22 с входом 23, регистр 24 числа с первым входом 25, формирователь 2б сигнала переполнения с входом 27. Блок управления содержит (фиг.2) генератор 28 сигналов, триггеры 29 и 30, элементы И 31 и 32, триггер 33, элемент И 3, элементы ИЛИ 3539, формирователь 0 сигналов начальной установки, элементы И , элементы ИЛИ , триггеры 48-50, элемент И 51, элемент 52 задержки и триггеры 53 и 54. На фиг.2 обозначены входы 55 Количество обрабатываемой информации, 5б Запись, 57 Считывание и 58 Обработка информации, являющиеся управляющими входами устройства. Устройство работает следующим образом. Предлагаемое устройство работает в режимах хранения информации и об(работки информации. Перед началом работы блок 13 управления устанавливает в исходное состояние регистры 2 накопителя 1, регистр 24, счетчик 5, блок 8 и вычитатель 18 Сфиг.1/. В режиме хране. ния информации устройство работает в двух подрежимах: записи и считыва ния информации. Режимы работы устро ства устанавливаются управляющими сигналами на входах (фиг.2). При записи информация поступает через входы 11 элементов И 9 на вхо ды регистра 2k, С выхода регистра 2 информация поступает через входы 3 накопителя 1 в первые разряды регис ров 2. Затем на входы 4 накопителя 1 поступает от блока 13 сигнал, который сдвигает записанную информацию на один разряд. .При поступлении следующего числа передачи инфо мации в накопитель .и происходит аналогично, после чего производи ся следующий сдвиг и т.д. При считывании информации по си|- налам сдвига из блока 13 код числа с выходов регистров 2 выдается на выходы устройства и поступает по цепям регенерации на входы 11 элементов И Э для перезаписи в регистры 2 накопителя 1. В режиме обработки информации устройство реализует два подрежима: сложение и вычитание входной информации, сложение и вычитание выходной информации. Эти два подрежима отличаются друг от друга тем, что в первом подрежиме информация поступает на входы 11 элементов И 9 через вхо ды устройства, а во втором подрежиме - с выходов регистров 2 накопителя 1. Устройство работает в первом под режиме следующим образом. Пусть информация через входы устройства поступает на вход 11 элементов И 9, на другие входы 10 которых поступает управляющий сигнал с блока 13. Тогда с выходов элементов И 9 ко числа поступает на входы 19 вычитателя 18, а знак - на вход 12 блока В. На вход 21 вычитателя 18 с блока 13 поступают управляющие сигналы, которые уменьшают содержимое вычитателя 18 на единицу. С выходов вычитателя 18 на третий вход блока 8 поступают сигналы, простробированные сигналом с блока 13 (фиг. О, по которым в зависимости от знака кода числа с выходов блока 8 поступают сигналы на вход 6 суммирования или вход 7 вычитания счетчика 5 до тех пор, пока код числа, хранящийся в вычитателе 18 не перепишется со своим знаком в счетчик 5, а содержимое вычитателя 18 не станет равным нулю. Тогда элемент НЕ 22 выдает в блок 13 по входу 15 сигнал, по которому устройство может принять следующее число и провести его обработку. Таким образом, после обработки нескольких чисел результат обработки со счетчика 5 поступает в регистр 2k, с выходов которого через входы 3 запишется в накопитель 1. Затем на входы k накопителя 1 с блока 13 поступает сигнал сдвига. После этого производится обработка следующего массива информации. Технико-экономическое преимущество предлагаемого устройтсва заключается в его упрощении, по сравнению с известным, что дает возможность реализовать его в виде одной большой интегральной схемы БИС) и за счет этого значительно снизить его стоимость. Формула изобретения Логическое запоминающее устройство, содержащее накопитель на регистрах сдвига, счетчик, блок определения знака числа, элементы И, блок управления, формирователь сигнала переполнения и регистр числа, выходы которого подключены соответственно к информационным входам накопителя, выходы которого подключены соответственно к одним из входов элементов И, одни из выходов которых соединены соответственно с входами регистра числа, первый вход блока определения знака числа подключен к одному из входов регистра числа, второй вход - к первому выходу блока управления и другим входам элемен TDB И, выходы блока определения знака числа соединены соответственно с входом суммирования и входом вычитания счетчика, одни из выходов которого подключены к другим входам регистра числа, другой выход счетчика соединен с входом формирователя сигнала переполнения, выход которого подключен к первому входу блока управления, второй выход которого соединен с управляющими входами накопителя, регистра числа и счетчика, один.из входов элементов И и выходы накопителя являются соот ветственно входами и выходами устройства, отличающееся

тем, что, с целью упрощения устройства, оно содержит вычитатель и элемент ,НЕ, вход которого подключен к выходам вычитателя и третьему входу блока определения знака числа, а выход - к второму входу блока управления, входы вычитателя соединены с другими выходами и входами элементов И соответственно.

Источники информации,

принятые во внимание при экспертизе

кл. G 11 С 15/00, 1979 (прототип).

«Nl

Авторы

Даты

1982-07-07—Публикация

1980-10-14—Подача