1

11зобрстс1:ие относится к вычислительной технике, в частности к быстродействующим ПЗУ с большим объемом хранимой информации.

Известно устройство для ностояниого хранения ранее записанной информации, которое состоит из диодного матрично1Ю накопителя и элементов управления, выход одних элементов управления подключены к адресным шинам диодного матричного накопителя, а вход других - к числовым шинам, замкнутым на нагрузочные соиротивлеиня.

Такое устройство имеет малую емкость из-за того, что силовые шины замкнуты на .нагрузочные сопротивления и при увеличе:иии числа числовых шин матричиого накопителя увеличивается нагрузка элемента унравления, -выход которого подключен к адpecur.iM шинам.

Целью изобретения является увеличение информационной емкостн устройства.

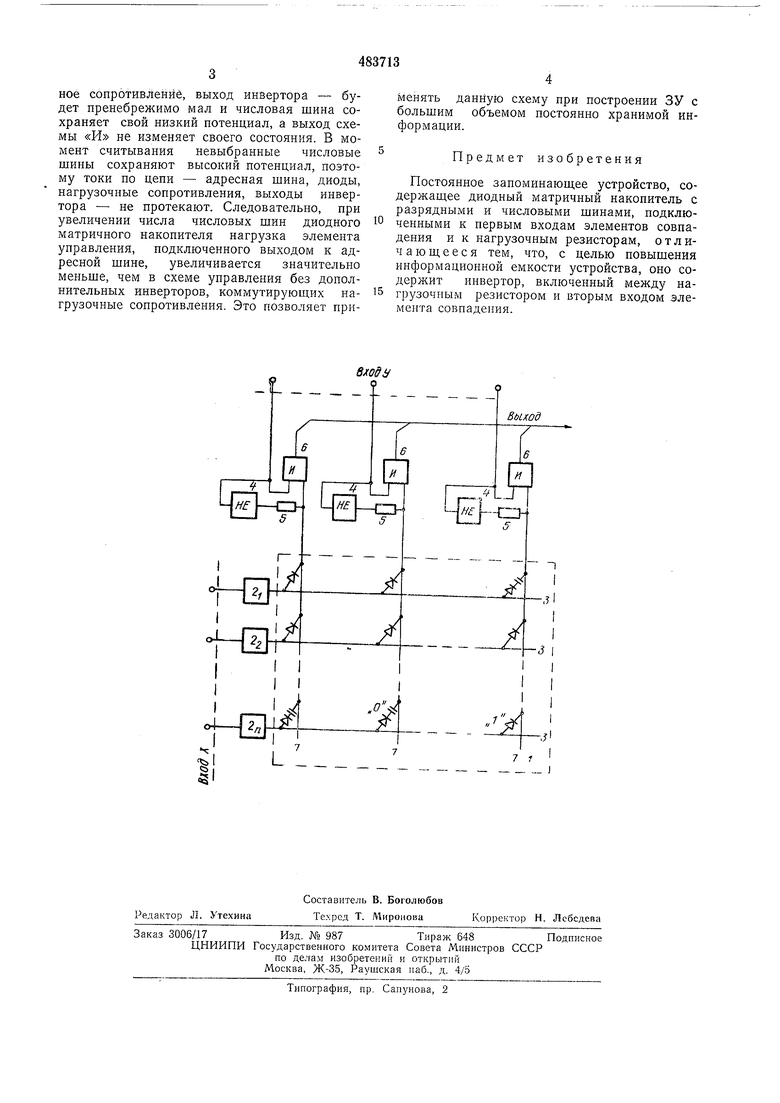

Эта це.аь достигается тем, что в ПЗУ введены ииверторы, включенные между нагрузочными резисторами и вторым входом элемента соБнадения.

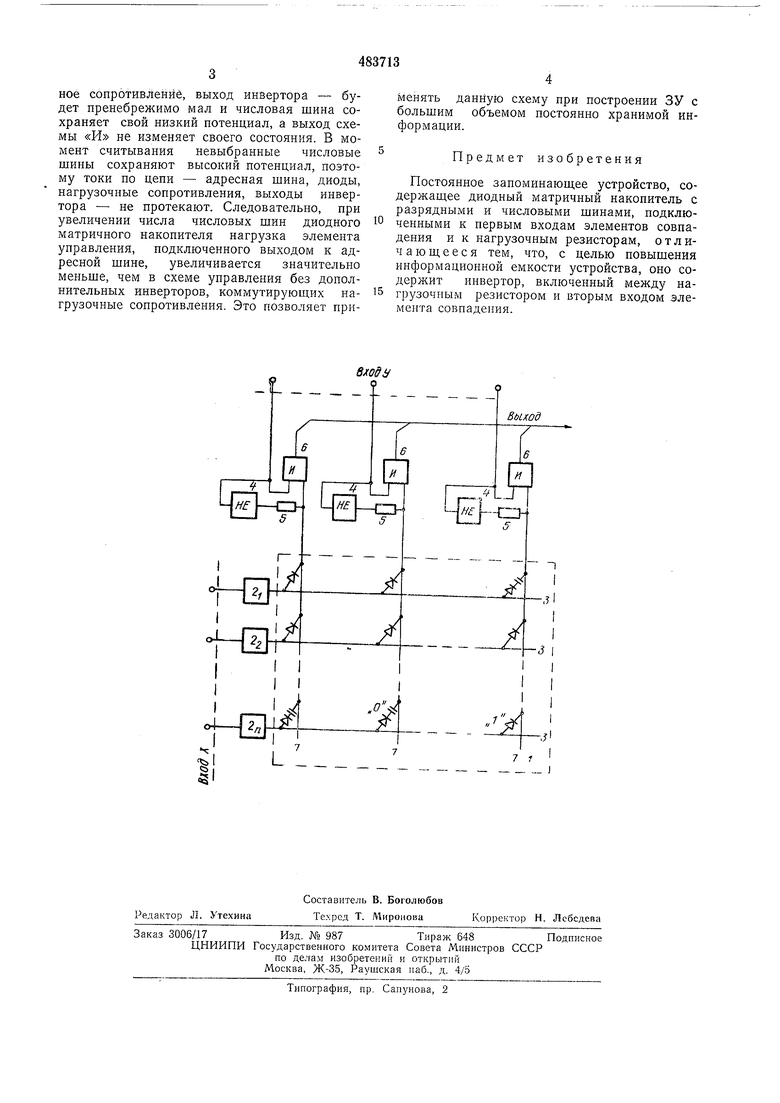

Па чертеже дана схема ПЗУ.

Оно состон1 из матричного накопителя 1, элементов упраолення 2i-2„, выходы которых подключе1 ы к адресным шинам 3, выбирающих одну из шин по входу X, инверторов

2

«ПЕ 4, подключенных выходом к числовым шинам накопителя через нагрузочные сопротивления 5, и схем совпадения «И 6. Один выход схем «И 6 подключен к числовым шинам 7, другой - ко входу инверторов и является входом у.

В статическом состоянии адресные шины диодного матричного накопителя и входы инверторов находятся под нулевым потенциалом, а числовые шины - под высоким потенциалом, соответствующим «1. ПЗУ работает следующим образом. При считывании на выбранную адресную шину с выхода элемента управления 2 подается положительный импульс. Одновременно на вход ннвертора 4 и схемы «И 6 выбираемой числовой шины подается положительный имнульс. В результате на выходе инвертора, а также на числовой шине устанавливается напряжение, соответствующее «О. Если диод в выбранной ячейке есть, то но цепи адресная шина 3, диод, нагрузочное сппротивленне 5, выход инвертора - протекает ток и на нагрузочном сонротивлении выбранной числовой шины появляется напряжение, соответствующее «1, т. е. на обоих входам схемы «П оказываются напряжения, соответствующие «1 и выход схемы «И изменяет свое состояние. Если .диода в выбранной ячейке нет, то ток - цепи - нагрузочное сопротивление, выход инвертора - будет пренебремшмо мал и числовая шина сохраняет свой низкий потенциал, а выход схемы «И не изменяет своего состояния. В момент считывания невыбранные числовые шины сохраняют высокий потенциал, поэтому токи ио цепи - адресная шина, диоды, нагрузочные сопротивления, выходы инвертора - не протекают. Следовательно, при увеличении числа числовых шин диодного матричного накопителя нагрузка элемента управления, подключенного выходом к адресной шине, увеличивается значительно меньше, чем в схеме управления без дополнительных инверторов, коммутирующих нагрузочные сопротивления. Это позволяет применять данную схему при построении ЗУ с большим объемом постоянно хранимой информации.

Предмет изобретения

Постоянное запоминающее устройство, содержащее диодный матричный накопитель с разрядными и числовыми щинами, подключенными к первым входам элементов совпадения и к нагрузочным резисторам, отличающееся тем, что, с целью повышения информационной емкости устройства, оно содержит инвертор, включенный между нагрузочным резистором и вторым входом элемента совпадения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство | 1978 |

|

SU752482A1 |

| Постоянное запоминающее устройство | 1978 |

|

SU767841A2 |

| Постоянное запоминающее устройство | 1982 |

|

SU1112411A1 |

| Постоянное запоминающее устройство | 1982 |

|

SU1101896A1 |

| Постоянное запоминающее устройство | 1977 |

|

SU739653A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU799006A1 |

| Запоминающее устройство | 1976 |

|

SU690564A1 |

| Постоянное запоминающее устройство | 1975 |

|

SU556498A1 |

| Постоянное запоминающее устройство | 1985 |

|

SU1305775A1 |

| Запоминающее устройство | 1974 |

|

SU491153A1 |

Авторы

Даты

1975-09-05—Публикация

1973-02-05—Подача