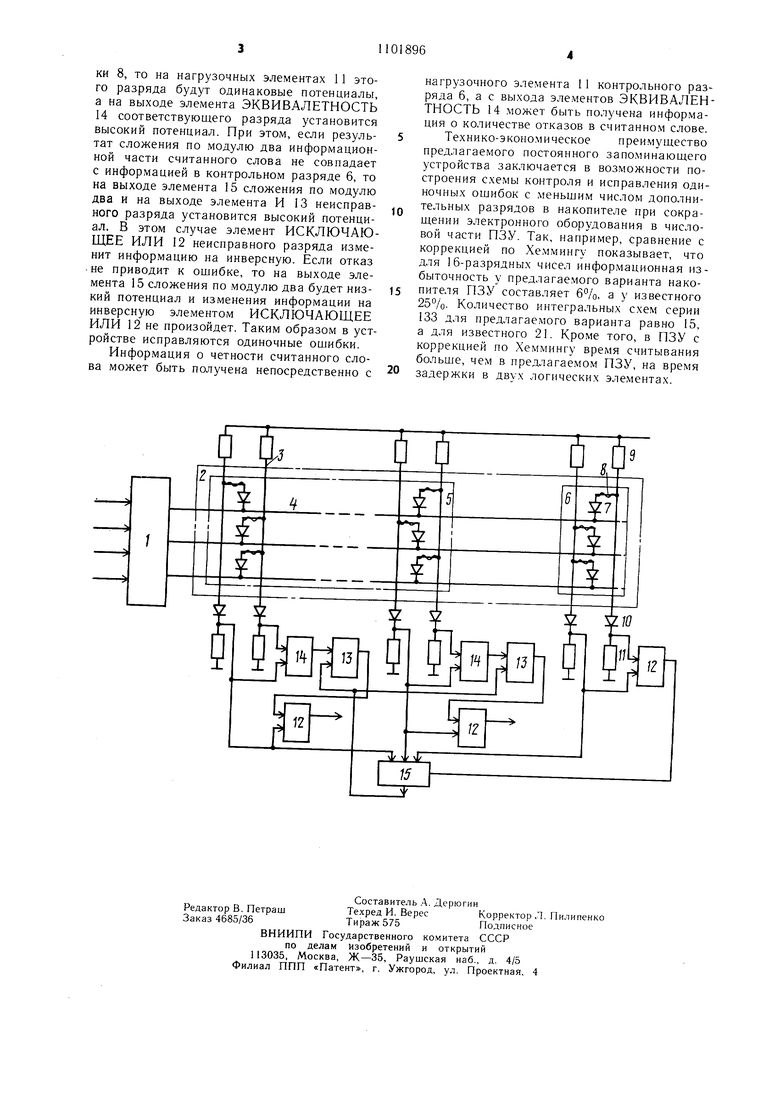

Изобретение относится к вычислите.чьной технике и может использовано при построении постоянных запоминающих устройств. Извесппя ностоянные зано.1инаюн1ие уст1)ойства (ПЗУ) матричного типа с контролем и исправленнем ип(|)ормации при считывании I 1 j i 2 I . 11едос1атком таких ПЗУ является то, что п-разрядный накопите,1ь содержит k контрольных разрядов, нричем k всегда больп1е ,1. Это приводит к увеличению оборудования нако11ите;1я и чис.ш элементов электронного обрамления усилител-ей считывания, элементов контроля и т. д. Кро.ме того, снижается быстродействие ПЗУ за счет увеличепия времени прохождения сигнала, полученного на В1л1ходе накопителя, через элементы схем неправ.1епия оигибок. Паибо;1ее б, по технической супд юстн и достигаемому эффекту к предлагаемому являетея устройство, содержа .ee диодный матричный нако11итель е нарафазн.ыми выходами инфор.маипонных разрядов и разряда коитро.ля четпостн, дешифратор млбора строки, которого соединены с входа.ми диодного матричного накопителя, а ВХОДВ1 являются входами уст)ойства, э;1емеит сложения по модулю два и ограничите;1ьп1 1е элемепты, через которые каждый выход диодного матричпого накопителя еоедипен с шиной питания 3. Педостатком известпого устройства яв.1яе ч:я то, что одиночпые О1ипбкп в не.м не иеп)а11.ляются. Для их |-1Снранле1 ия в пакопиle.ie необходимо предусмотреть К дополпите.:|Ы11 г разрядов, нричем К.1. ИсправлеiHie О1пибок с при.меиеппем ксхюв Хем.мипга в этом е.лучае приводит к уве.шчению обору;1овап)1Я ь;акопите.:|я и чие;1а элемептов чис.овой части э,лектрон11(хго об)амления ПЗУ. За счет введения допо.тнительных усилите.|ей сч.чтывания, э;1ементов кон.гроля и иенравлеппя считаьчгой информации уменьшается эффективность применения коррекции. Пе.ль изобретения - - noBbinjeiine надеж1Юст1-1 устройства путем псиравления одиноч| ЫХ ОП1ИбоК. Поетав.ленная цель достигается те.м, что в ностоянно.м запо.мипаюи1,е.м устройстве, содержащем диодный матричный наконнтель с нарафазньгмп выходами информационных разрядов п разряда контроля четности, дешифратор выбора строки, выходы коTopoio соединены с входами диодно1о матрич ного накопителя, а входы являются входами устройства, э.пемент сложения но .моду.по два и огра1 ичительные э-лементы, через которые каждый выход диодного .матричного накопителя еоедииен е шиной иитапия, в каждь й разряд ьакопителя введены два ограничительных элемента на диоднах, два нагрузочных э.лемеита и эле.мент ИСКЛЮЧАЮЩЕЕ ИЛИ и в каждый информациогшый разряд - элемент ЭКВИВАЛЕНТНОСТЬ и элемент И, приче.м в каждом разряде парафазные выходы накопителя соединены е анода.ми диодов, катоды которых через нагрузочные элементы соединены с шиной нулевого потенциала, в каждом инфор.мационном разряде входы элемента ЭКВИВАоТЕНТНОСТЬ соединепы с катода.мн диодов, а его выход - с первы.м входом эле.мента И, второй вход которого соединен с выходо.м элемента сложения по модулю два, а выход - с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с вторым входом элемента ЭКВИВАЛЕНТНОСТЬ и с входо.м элемента сложения по .модулю два, а его выход является выходо.м устройства, входы эле.мента ИСКЛЮЧАЮЩЕЕ ИЛИ разряда контроля четности соединены с катодами диодов, соответствующих данному разряду, его второй вход соединен с входо.м эле.мента сложения по .модулю два, а выход -- с управляющим входом эле.мента сложения по модулю два. На чертеже изображена схема предложенного устройства. Постоянное запоминающее устройство содержит дещифратор 1 выбора строки, диодный матричный накопитель 2, состоящий из столбцов 3, строк 4, информационных разрядов 5, контрольного разряда б, информационных диодов 7 и плавких цере.мычек 8, ограничительные элементы 9, ограничительные эле.менты на диодах iO, нагруочные элементы 11, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 12, эле.менты И 13, элементы ЭКВИВАЛЕНТНОСТЬ 14 и элемент 15 сложения по модулю два. Устройство работает следующим образом. Запись инфор.мации в диодный матричный накопитель осуществляется до установки в постоянное запоминающее устройство пережиганием плавких перемычек. Считывание информации происходит следующим образом. Дешифратор 1 выбора строки в соответствии с заданным адресом формирует низкий потенциал на выбранной строке 4. При этом на нагрузочных элементах 1 1 в каждо.м разряде устанавливаются низкие и высокие потенциалы в соответствии с записанной в накопитель 2 инфор.мацией, а па выходах элементов ЭКВИВАЛЕНТНОСТЬ 14 и И 13 устанавливается низкий потенциал. Считанная из накопителя информация может быть записана в регистр числа ПЗУ (не показан) с выхода элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 12 но окончании переходных процессов в элементах 15 сложения но модулю два, ЭКВИВАЛЕНТНОСТЬ 14, И 13 и ИСКЛЮЧАЮЩЕЕ ИЛИ 12. Если в каком-нибудь разряде имеется отказ, например короткое замыкание столбцов 3, обрыв диода 7 или плавкой пере.мычки 8, то на нагрузочных элементах 11 этого разряда будут одинаковые потенциалы, а на выходе элемента ЭКВИВАЛЕТНОСТЬ 14 соответствующего разряда установится высокий потенциал. При этом, если результат сложения по модулю два информационной части считанного слова не совпадает с информацией в контрольном разряде 6, то на выходе элемента 15 сложения по модулю два и на выходе элемента И 13 неисправного разряда установится высокий потенциал. В этом случае элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 12 неисправного разряда изменит информацию на инверсную. Если отказ не приводит к ошибке, то на выходе элемента 15 сложения по модулю два будет низкий потенциал и изменения информации на инверсную элементом ИСКЛЮЧАЮЩЕЕ ИЛИ 12 не произойдет. Таким образом в устройстве исправляются одиночные ошибки.

Информация о четности считанного слова может быть получена непосредственно с

нагрузочного элемента 11 контрольного разряда 6, а с выхода элементов ЭКВИВАЛЕНТНОСТЬ 14 может быть получена информация о количестве отказов в считанно.м слове. Технико-экономическое преимущество предлагаемого постоянного запоминающего устройства заключается в возможности построения схемы контроля и исправления одиночных ошибок с меньшим числом дополнительных разрядов в накопителе при сокращении электронного оборудования в числовой части ПЗУ. Так, например, сравнение с коррекцией по Хеммингу показывает, что для 16-разрядных чисел информационная избыточность у предлагаемого варианта накопителя ПЗУ составляет 6%, а у известного 25%- Количество интегральных схем серии 133 для предлагаемого варианта равно 15, а для известного 21. Кроме того, в ПЗУ с коррекцией по .Хеммингу время считывания больше, чем в предлагаемом ПЗУ, на время

0 задержки в двух логических элементах.

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство | 1978 |

|

SU752482A1 |

| Постоянное запоминающее устройство | 1973 |

|

SU483713A1 |

| Постоянное запоминающее устройство | 1985 |

|

SU1305775A1 |

| Постоянное запоминающее устройство | 1982 |

|

SU1112411A1 |

| Запоминающее устройство | 1986 |

|

SU1361630A1 |

| УНИВЕРСАЛЬНАЯ ЦИФРОВАЯ УПРАВЛЯЮЩАЯ МАШИНА | 1965 |

|

SU170218A1 |

| Запоминающий модуль для постоянной памяти | 1981 |

|

SU991510A1 |

| Постоянное запоминающее устройство | 1978 |

|

SU767841A2 |

| Постоянное запоминающее устройство | 1977 |

|

SU739653A1 |

| Устройство декодирования для системы передачи цифровых сигналов | 1985 |

|

SU1305884A1 |

ПОСТОЯННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее диодный матричный накопитель с нарафазными выходами информационных разрядов и разряда контроля четности, дещифратор выбора строки, выходы которого соединены с входами диодного матричного накопителя, а входы являются входами устройства, элемент сложения по модулю два и ограничительные элементы, через которые каждый выход диодного матричного накопителя соединен с щиной питания, отличающееся тем, что, с целью повыщения надежности устройства путем исправления одиночных ощибок, в каждый разряд накопителя введены два ограничительных элемента на диодах, два нагрузочных элемента и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и в каждый информационный разряд - элемент ЭКВИВАЛЕНТНОСТЬ и элемент И, причем в каждом разряде парафазные выходы накопителя соединены с анодами диодов, катоды которых через нагрузочные элементы соединены с шиной нулевого потенциала, в каждом информационном разряде входы элемента ЭКВИВАЛЕНТНОСТЬ соединены с катодами диодов, а его выход - с первым входом элемента И, второй вход которого соединен с выходом элемента сложения по модулю два, а выход - с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с вторым входом элемента ЭКВИВАЛЕНТ- «g НОСТЬ и с входом элемента сложения по модулю два, а его выход является выходом устройства, входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ разряда контроля четности соединены с катодами диодов, соответствующих данному разряду, его второй вход соединен с входом элемента сложения по модулю два, а выход - с управляющим входом элемента сложения по модулю два.

О

О

о

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| 0 |

|

SU341062A1 | |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| А | |||

| Постоянные запоминающие устройства цифровых машии | |||

| Л., «Энергия, 1969, с | |||

| Устройство для усиления микрофонного тока с применением самоиндукции | 1920 |

|

SU42A1 |

| Прибор для получения стереоскопических впечатлений от двух изображений различного масштаба | 1917 |

|

SU26A1 |

Авторы

Даты

1984-07-07—Публикация

1982-07-05—Подача