1

Изобретение относится к вычислительной технике, в частности к микроэлектронным запоминающим устройствам иможет быть использовано в устройствах обработки цифровой информации в качестве постоянной памяти подпрограмм, табличных данных, генераторов символов, функций и др.

Известно постоянное запоминающее устройство (ПЗУ), содержащее матричный накопитель с разрядными и числовыми шинами, подключенными к первым входам элементов Ник нагрузочным р зисторам, инвертор, включенный между нагрузочным резистором и вторым входом элемента И 111.

Недостатки ПЗУ следующие: большое количество схем управления - по входам X и по входам У, что увеличивает потребляемую мощность и уменьшает быстродействие считывания информации;

большое количество резисторов, инверторов и элементов И, что увеличивает потребляемую мощность, уменьшает быстродействие считывания информации ;

невозможность изготовления на одном кристалле накопителя, резисторов инверторови элементов совпадения.

что увеличивает количество паяных соединений, увеличивает паразитные емкости - уменьшается быстродействие, снижается надежность функционирования

устройства, усложняется технология ее изготовления.

Наиболее близким по технической сущности -является ПЗУ, содержащее адресный дешифратор, выходы которого

соединены с соответствующими входными шинами накопителя, состоящего из W секций, выходные шины накопителя и шифратор, и шины управления по числу секций и вентили по числу выходных шин накйпителя, при этом все первые входы всех вентилей соединены с соответствующими выходными шинами накопителя, а вторые входы вентилей каждой секции объединены и подключены к соответствующей шине управления, выходы одноименных вентилей всех секций объединены между собой и подключены JC соответствующему входу шиф ратора 2 .

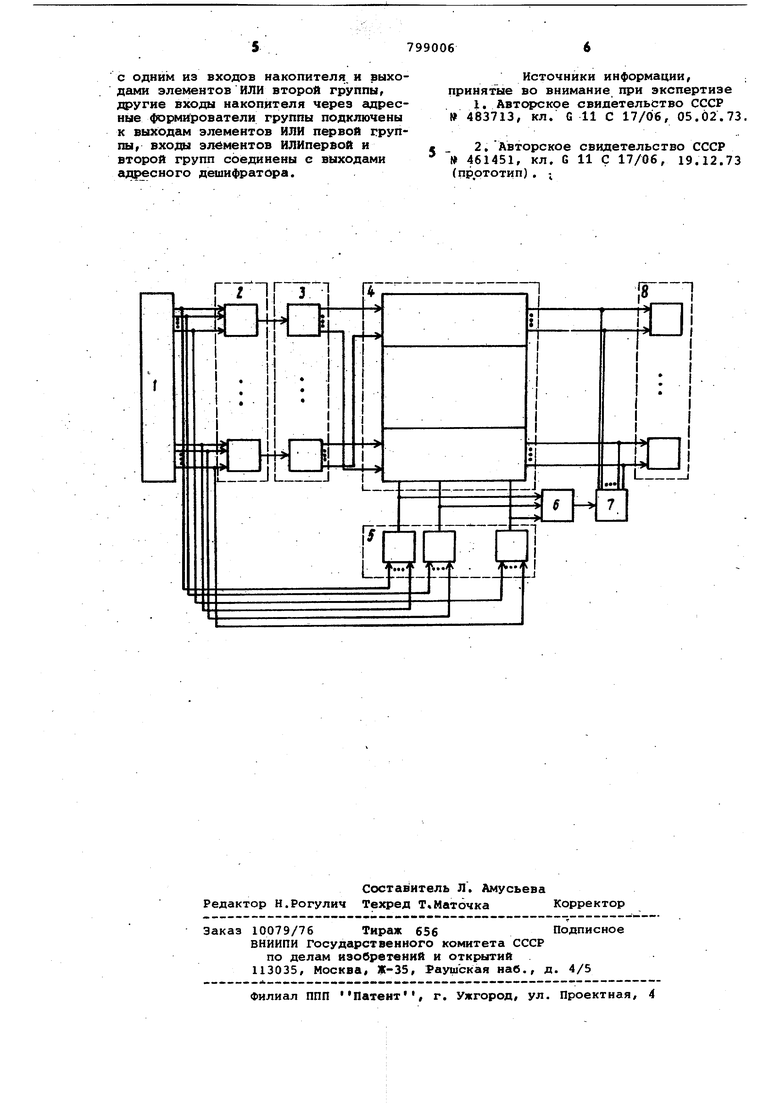

Однако в известном устройстве использование большого количества вентилей увеличивает паразитные емкости, уменьшает быстродействие устройства, увеличивает потребляемую мощность, снижает надежность функционирования устройства. Невозможность изготовления всех узлов ПЗУ на одном кристалле ограничивает информационную емкость. Кроме того, однокоординатная выбор ка является ограничивающим фактором увеличения информационной емкости, в результате для построения ПЗУ с бол шой информационной ейкостью необходи мо использовать большое количество кристаллов, а это уменьшает быстродействие устройства и снижает надеж- ность функционирования устройства. Цель изобретения - повышение быст родействия устройства. Поставленная цель достигается тем что в постоянное запоминающее устрой ство, содержащее адресный дешифратор и накопитель, введены группы элементов ИЛИ, группа адресных формировате лей, группа формирователей считывани элемент ИЛИ и адресный формирователь выходы которого соединены с выходами накопителя и входами соответствующих формирователей считывания группы, вход адресного формирователя через элемент ИЛИ соединен с одним из входов накопителя и выходами элементов ИЛИ второй группы, другие входы нако пителя через адресные формирователи группы подключены к выходам элементо ИЛИ первой группы, входы элементов ИЛИ первой и второй групп соединены с выходами адресного дешифратора. На чертеже представлена структурная схема предлагаемого ПЗУ; ПЗУ содержит адресный дешифратор 1, соответствующие выходы которого подключены к одноименным входам соот ветствующих элементов ИЛИ первой гру пы -2, выходы элементов ИЛИ первой группы подключены ко входам соответ ствующих адресных формирователей пер вой группы 3, выходы адресных формирователей первой группы подключены К соответствующим первьм входам нако пителя 4, причем одноименные входы элементов ИЛИ первой группы 2 подключены к одноименным входам соответстйующих элементов ИЛИ второй группы 5, выходы элементов ИЛИ второй группы подключены к соответствую щим вторым входам накопителя 4, а также к соответствующим входам элемента ИЛИ б, выход которого подключе к входу адресного формирователя 7, при этом выходы накопителя 4 подключены к.одноименным входам соответствующих формирователей 8 считывания, а также к соответствующим выходам гщресного формирователя 7 . ПЗУ работает следующим образом. На одном (необходимом) выходе адресного дешифратора 1 вырабатывается низкий уровень напряжения {J , а на остальных выходах вырабатывают ся высокие уровни напряжения UB ПР этом сигнал через выбранный адресный формирователь первой группы 3 поступает на соответствующие первые входы накопителя 4, а также через выбранный элемент ИЛИ второй группы 5 поступает на соответствующий второй вход накопителя 4 на соответствующий вход элемента ИЛИ б, с выхода которого сигнал поступает на соответствующий вход адресного формирователя 7,.на выходах последнегоустанавливаются высокие уровни напряжения. При этом выбираются необходимые запоминающие элементы (по одному в каждой секции) и ,из накопителя 4 в .результате . считывается Jii-разрядное двоичное слово с помощью формирователей 8 считывания. После этого на выходах адресного формирователя второй группы 7 вырабатываются низкие уровни напряжения и происходит быстрый перезаряд . паразитных емкостей. По сравнению с известным предлагаемое ПЗУ имеет следующие преимущества:., . . введение элемента ИЛИ 6 и адресного формирователя 7 существенно повышает быстродействие устройства (происходит быстрая разрядка паразитных емкостей); отсутствие большого количества вентилей, в результате уменьшаются паразитные емкости (повышается быстродействие устройства); уменьшается задержка считывания информации (повышается быстродействие устройства), повышается надежность функционирования устройства; упрощение технологии изготовления устройства; введение адрес,ных формирователей первой группы и элементов ИЛИ первой и второй групп позволяют построить ПЗУ с большой информационной емкостью (считывание информации осуществляется двухкоординатной выборкой), уменьшаются паразитные емкости (повышается быстродействие устройства), уменьшается количество паяных соединений (повышается быстродействие и надежность функционирования устройства). Формула изобретения Постоянное запоминающее устройство, содержащее адресный дешифратор и накопитель, отличающе тся тем, что, с целью повышения быстродействия, в него . введены группы элементов ИЛИ, группа адресных формирователей, группа формирователей считывания, элемент ИЛИ и адресный формирователь, выходы которого соединены с выходами накопителя и входами соответствующих формирователей считывания группы, вход адресного формирователя через элемент ИЛИ соединен

с одним из входов накопителя, и выходами элементов ИЛИ второй группы, другие входы накопителя через адресные формирователи группы подключены к выходам элементов ИЛИ первой группы, входы элементов ИЛИпервой и второй групп соединены с выходами гщресного дешифратора.

Источники информации, ; принятые во внимание при экспертизе

1.Авторское свил етельство СССР

483713, кл. G 11 С 17/06, 05.02.73.

2,Авторское свидетельство СССР

461451, кл. G 11 С 17/06, 19.12.73 (прототип). ;

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устрой-CTBO | 1979 |

|

SU809381A1 |

| Постоянное запоминающее устройство | 1978 |

|

SU752482A1 |

| Постоянное запоминающее устройство | 1978 |

|

SU767841A2 |

| Постоянное запоминающее устройство | 1982 |

|

SU1096693A1 |

| Постоянное запоминающее устройство | 1978 |

|

SU805413A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU841047A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Постоянное запоминающее устройство | 1982 |

|

SU1112411A1 |

| Запоминающее устройство | 1979 |

|

SU809367A1 |

| Запоминающее устройство | 1976 |

|

SU690564A1 |

Авторы

Даты

1981-01-23—Публикация

1979-01-10—Подача