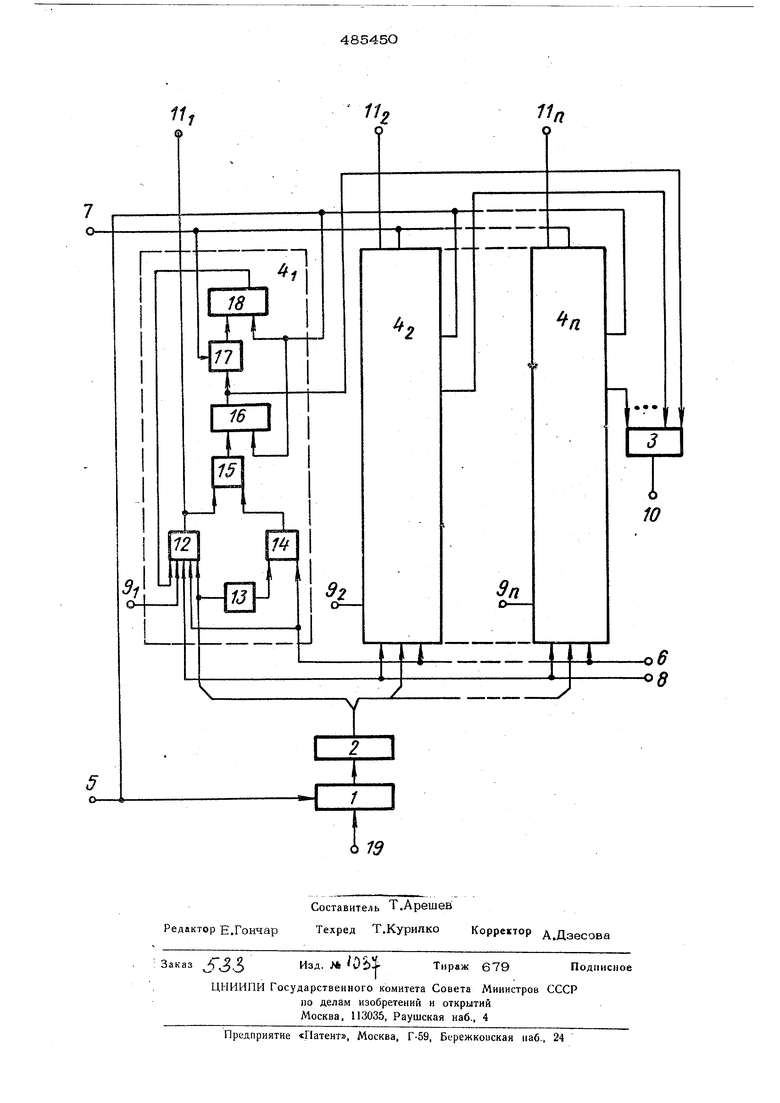

дом элемента- И, выход которого соединен с выходом признака окончания передачи устройства. Кроме того, каждый логиче ский блок направления передачи содержит два триггера, три элемента И, элемент ИЛИ и элемент НЕ, причем первый |вход первого элемента И соединен с пер вым входом логического блока и с входом элемента НЕ, выход которого соединен с первым входом второго элемента И, второй вход которого соединен со вторым входом первого элемента И и с четвер- , тым входом логического блока, а выход с первым входом элемента ИЛИ. Выход последнего соединен с нулевым входом первого триггера, единичный вход которого соединен с единичным входом второго триггера и с пятым входом логического блока, выход первого триггера соеданен со вторым выходом логического блока и с первым входом третьего элемента И, второй вход которого соединен с шестым входом логического блока, а выход - с нулевым входом второго триггера, единич йый выход которого соединен с третьим входом первого элемента И, четвертый вход которого соединен со вторым входом логического блока направления передачи, пятый вход первого элемента И соединен с третьим входом логического блока, а выход первого элемента И соединен, со вторым входом элемента ИЛИ и с первым выходом логического блока. На чертеже приведена схема устройства. Устройство содержит регистр 1 кода операции, дешифратор 2, элемент .И 3, логические блоки направления передачи 4 , 4 , ... 4 л, , первый вход 5 синхрюнизащш, второй вход 6 синхронизации, третий вход 7 синхронизации, вход 8 приз нака готовности к передаче, входы 9. .LI признаков готовности к приему, выход 10 признака окончания передачи, выходы 11.., Ир управления приемом, элемент И 12, элемент НЕ 13, элемент И 14, элемент ИЛИ 15, первый триггер 16, элемент И 17, второй триггер 18, лиформационный вход 19. Устройство работает следующим образом. В результате подачи на первый вход синхронизации 5 импульсного сигнала осуществ;шется занесение с им гармационного входа 19 устройства кода операции, определяющего направления передачи информации, в регистр 1 и установка в ч единичное состояние триггеров 16 и 18 всех логических блоков напраБ 1ения передачи. На входах дешифратора 2 формируются сигналы , фиксирующие направления передачи информации, причем на ,-ом выходе сигнал возбуждается в том случае, если должен быть сформирован импульсный сигнал на выходе 11, ; управления приемом информации устройства. Коиичество сигналов I, возбуждаемых одновременно на выходах дешифратора 2, соответствует общему количеству сигналов управления приемной информации устройства, вырабатьшаемых при реализации принятого в регистр 1 кода операции (количеству принимаемых АЛБ, в которые следует переслать информацию с выхода рассматриваемого передающего АЛБ). Синхроимпульсы, последовательно поступающие на второй и третий входы синхронизации (6 и 7, соответственно), вызывают последовательный переход в нулевое состояние триггеров 16 и 18 тех логических блоков направления передачи, которым соответствуют си1 налы О на выходах дешифратора 2. Формирование импульсного сигнала управления приемом информации на выходе элемента И12 к-го логического блока направления передачи, которому соответствует сигнал l на соответствующем выходе дешифратора 2, происходит только при единичных значениях признака готовности к передаче устройства (вход 8) и соответствующего признака готовности к приему устройства (вход 9), поступающего из соответствующего принимающего АЛБ. Признак, формируемый на входе 8 устройства, фиксирует заверщение вьшолнения микроопераций, обеснечивающих преобразование информации в передающем АЛБ. В результате выработки сигнала на выоде элемента И 12 к-го логического лока направления передачи (при этом фо{ ируется также сигнал на выходе 11 правления приемом информации устройства) риггеры 16 и 18 этого блока последоваельно переходят в нулевое состояние, что сключает повторную выработку управляюего сигнала. После того как будут сфо)ированы все сигналы управления приемом нформации устройства, определяемые кодом перации в регистре 1, триггеры 16 всех огических блоков направления передачи аходятся в нулевом состоянии. Это влочет а собой выработку сигнала 1 на выходе лемента И 3.

Предмет изобретения

1, Устройство для управления передачей информации в ЦВМ, содержащее регистр ко« да операции и дешифратор, причем,, первый б вход регистра кода операции соединен с информационным входом устройства, второй вход регистра кода операции соединен с первым входом синхронизации устройства, выход регистра кода операции соединен со 10 входом дешифратора, о тли чающеес я тем, что, с целью повышения быстродействия устройства, оно дополнительно содержит элемент И и логические блоки направления передачи, первый вход каждого 1& из которых соединен с соответствующим выходом дешифратора, второй вход соединен со входом признака готовности к передаче устройства, третий вход соединен с соответствующим входом признака готовно- 20 сти к приему устройства, четвертый вход соединен со вторым входом синхронизации устройства, пятый вход соединен с первым входом синхронизации устройства, шестой вход соединен с третьим входом синхрони- 25 зации устройства, первый выход каждого логического блока соединен с соответствук щим выходом управления приемом информации устройства, а второй его выход соедп-i йен с соответствующим входом элемента 30 И, выход которого соединен с выходом признака окончания передачи устройства.

. 2 Устройство пов, 1,отлича юЩ в ,тем, что, каждь1й логический блок направления передачи содержит два триггера, три элемента И, элемент ИЛИ и элемент НЕ, причем первый вход первого элемента И соединен с первым входом логического блока и с входом элемента НЕ выход которого соединен с первым входом второго элемента И, второй вход которого соединен со вторым входом первого элемента И и с четвертым входом логического блока, а выход - с первым входом элемента ИЛИ, выход которого соединен с нулевым входом первого тригirepa, единичный вход которого соединен с единичным входом второго триггера и с пятым входом логического блока, выход первого триггера соединен со вторым выходом логического блока и с первым входом третьего элемента И, второй вход которого соединен с шестым входом логического блока а выход - с нулевым входом второго триггера, единичный выход которого соединен с третьим входом первого элемента И, четвертый вход которого соединен со вторым входом логического блока направления передачи, пятый вход первого элемента И соединен с третьим входом логического блока, а выход первого элемента И соединен со вторым вхо | дом элемента ИЛИ и с первым выходом логического блока,

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор программируемого контроллера | 1985 |

|

SU1406595A1 |

| Ячейка однородной вычислительной среды | 1986 |

|

SU1443000A1 |

| ДИСКРЕТНАЯ МИКРОКОНТРОЛЛЕРНАЯ СЕТЬ | 1997 |

|

RU2110827C1 |

| Адаптивное устройство для сопряжения ЭВМ с каналами связи | 1987 |

|

SU1532938A1 |

| Процессор матричной вычислительной системы | 1987 |

|

SU1603395A1 |

| Устройство для контроля цифровых узлов | 1986 |

|

SU1357959A1 |

| Модульное устройство программного управления и контроля | 1990 |

|

SU1803905A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Трехканальная резервированная микропроцессорная система | 1985 |

|

SU1378287A1 |

| Дельта-кодек | 1987 |

|

SU1427572A1 |

Авторы

Даты

1975-09-25—Публикация

1973-04-03—Подача