I

Изобретение относится к области автоматики и вычислительной техники и предназначено для преобразования двоичных чисел в двоично-десятичные.

Известно устройство для прео бразования двоичного кода в двоично-десятичный, работающее по принцилу сдвига и коррекции и содержащее сдвиговый регистр, разделенный на тетраду. Выходы разрядов каждой тетрады соединены с входами соответствующего блока (дещифратора) коррекции, выходы которого подключены к входам соответствующих разрядов той же тетрады. Число блоков коррекции равно, таким образом, числу тетрад в сдвиговом регистре.

Предложенное устройство отличается тем, что выход старшего разряда каждой тетрады сдвигового регистра, кроме первой тетрады, соединен с входом соответствующего элемента «И блока коммутации, входы всех тетрад сдвигового регистра, кроме первой и второй тетрад, - с соответствующими управляющими входами устройства.

Это позволяет упростить устройство за счет исключения блоков коррекции для всех тетрад, кроме одной. Исключенное из известного устройства оборудование гораздо сложнее, чем дополнительное оборудование (блок коммутации и источник управляющих сигналов) в предложенном устройстве.

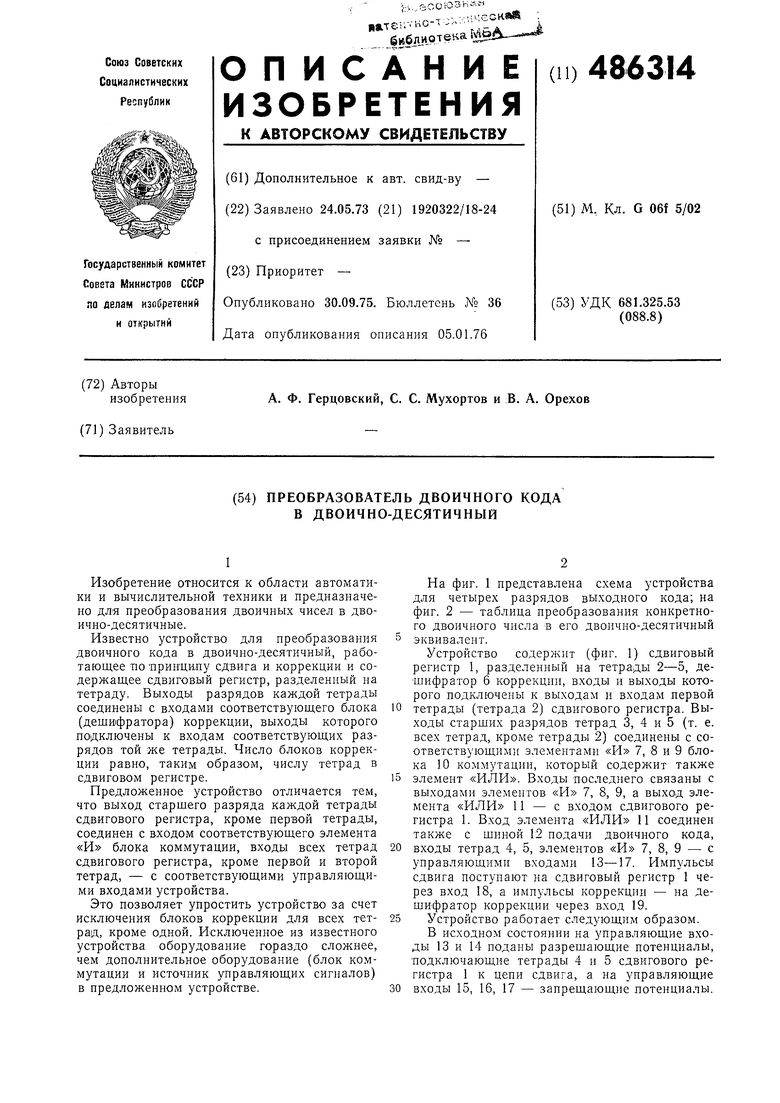

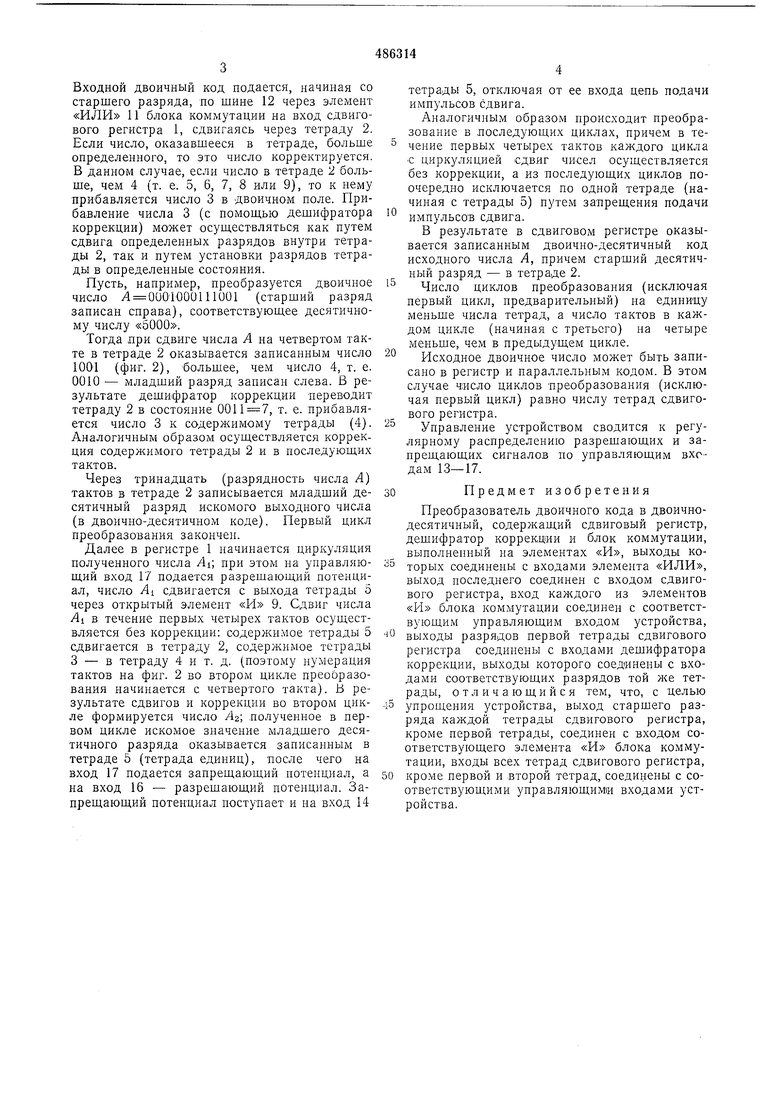

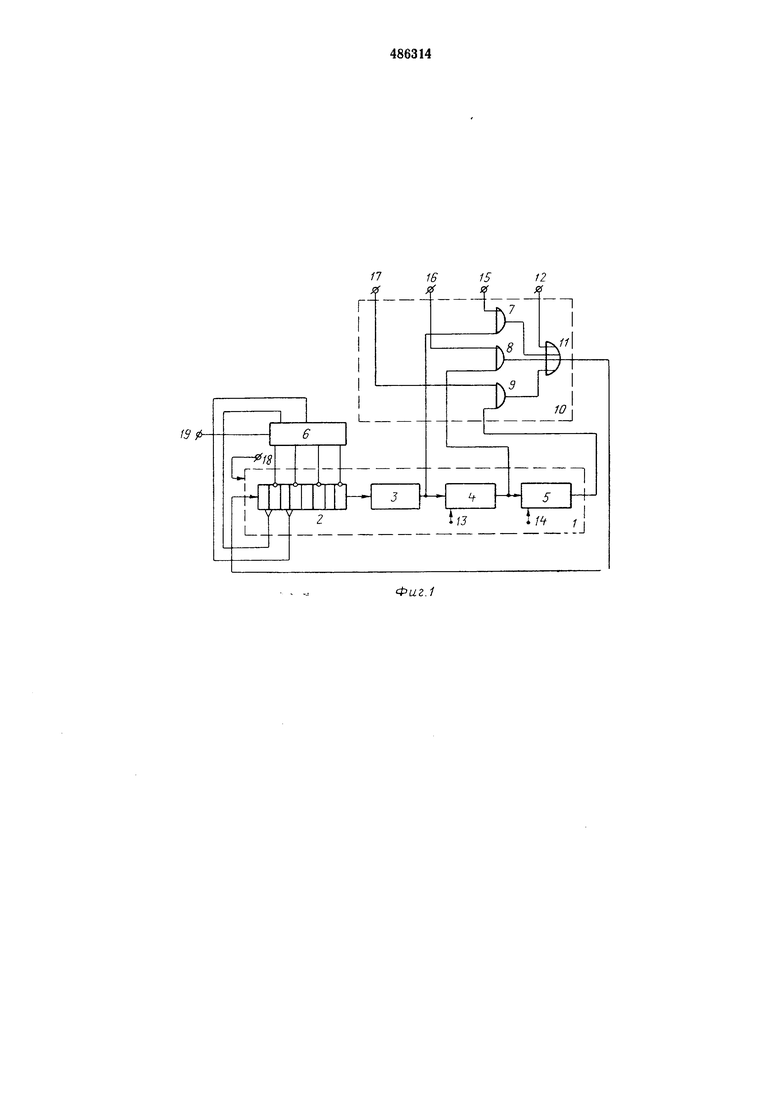

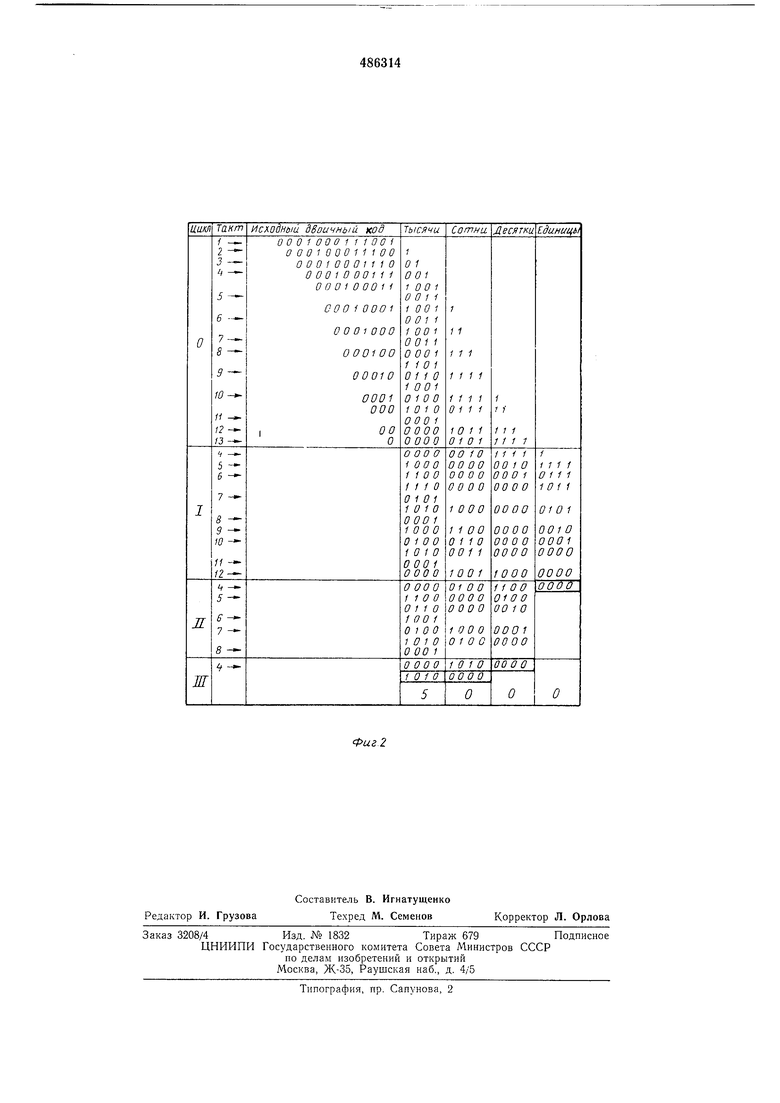

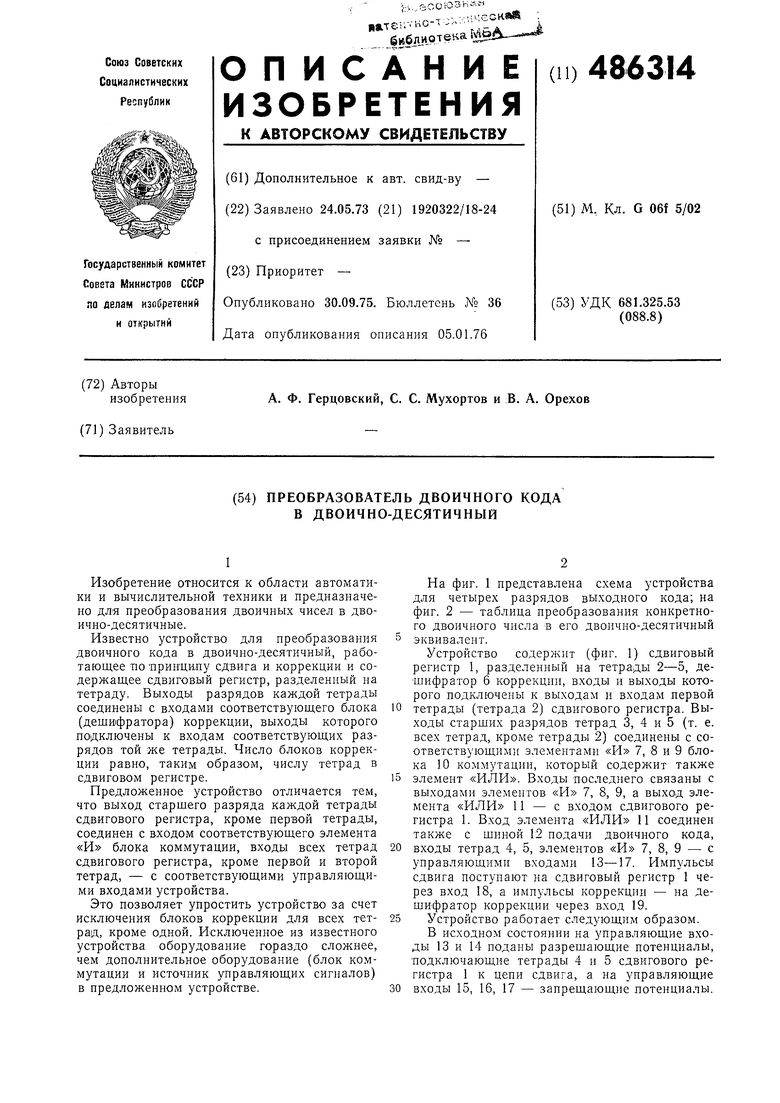

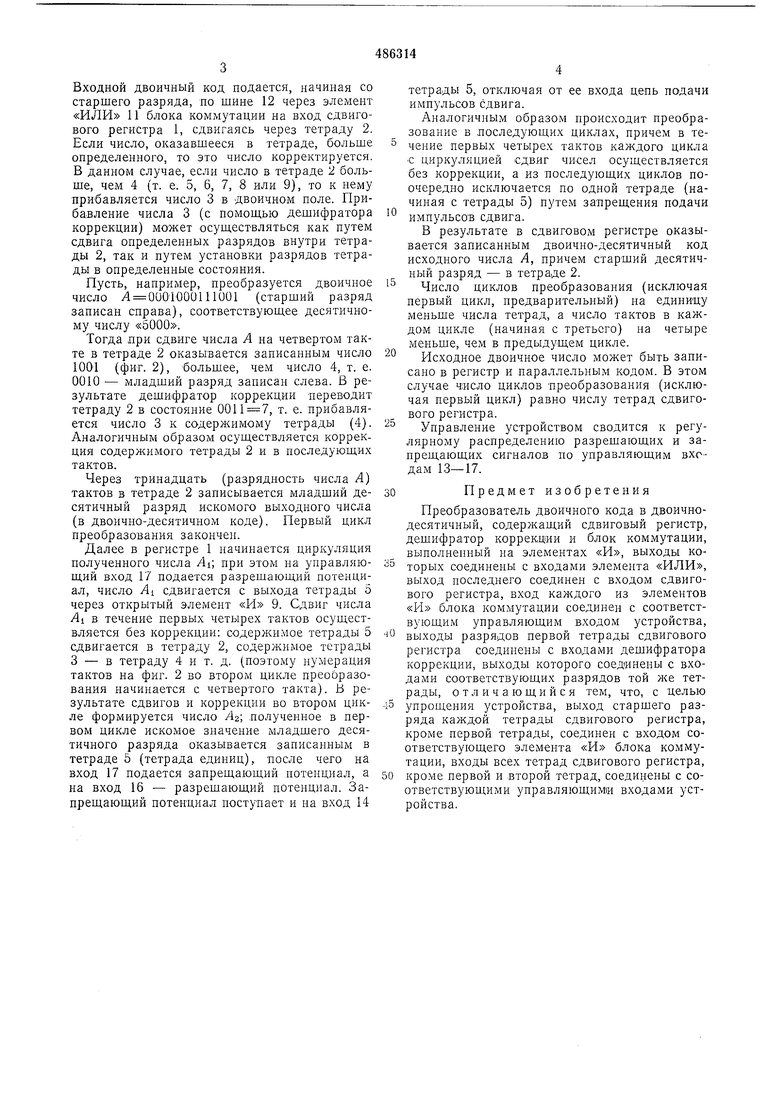

На фиг. 1 представлена схема устройства для четырех разрядов выходного кода; на фиг. 2 - таблица преобразования конкретного двоичного числа в его двоично-десятичный эквивалент.

Устройство содержит (фиг. 1) сдвиговый регистр 1, разделенный на тетрады 2-5, дешифратор 6 коррекцни, входы и выходы которого подключены к выходам и входам первой

тетрады (тетрада 2) сдвигового регистра. Выходы старших разрядов тетрад 3, 4 и 5 (т. е. всех тетрад, кроме тетрады 2) соединены с соответствующими элементами «И 7, 8 и 9 блока 10 коммутации, который содерл ит также

элемент «ИЛИ. Входы последнего связаны с выходами элементов «И 7, 8, 9, а выход элемента «ИЛИ 11 - с входом сдвигового регистра 1. Вход элемента «ИЛИ 11 соединен также с шиной 12 подачи двоичного кода,

входы тетрад 4, 5, элементов «И 7, 8, 9 - с управляющими входами 13-17. Импульсы сдвига поступают на сдвиговый регистр 1 через вход 18, а импульсы коррекции - на Дешифратор коррекции через вход 19.

Устройство работает следующим образом.

В исходном состоянии на управляющие входы 13 и 14 поданы разрешающие потенциалы, подключающие тетрады 4 и 5 сдвигового регистра 1 к цепи сдвига, а на управляющие

входы 15, 16, 17 - запрещающие потенциалы.

Входной двоичный код подается, начиная со старшего разряда, по шнне 12 через элемент «ИЛИ 11 блока коммутации на вход сдвигового регистра 1, сдвигаясь через тетраду 2. Если число, оказавшееся в тетраде, больше определенного, то это число корректируется. В данном случае, если число в тетраде 2 больше, чем 4 (т. е. 5, 6, 7, 8 или 9), то к нему прибавляется число 3 в двоичном поле. Прибавление числа 3 (с помош,ью дешифратора коррекции) может осуш,ествляться как путем сдвига определенных разрядов внутри тетрады 2, так и путем установки разрядов тетрады в определенные состояния.

Пусть, например, преобразуется двоичное число Л 0001000111001 (старший разряд записан справа), соответствуюш ее десятичному числу «5000.

Тогда при сдвиге числа Л на четвертом такте в тетраде 2 оказывается записанным число 1001 (фиг. 2), большее, чем число 4, т. е. 0010 - младший разряд занисан слева. В результате дешифратор коррекции переводит тетраду 2 в состояние , т. е. прибавляется число 3 к содержимому тетрады (4). Аналогичным образом осуш.ествляется коррекция содерл имого тетрады 2 и в иоследуюших тактов.

Через тринадцать (разрядность числа Л) тактов в тетраде 2 записывается младший десятичный разряд искомого выходного числа (в двоично-десятичном коде). Первый цикл преобразования закончен.

Далее в регистре 1 начинается циркуляция полученного числа AI; при этом на управляюш,ий вход 17 подается разрешаюш,ий потенциал, число Ai сдвигается с выхода тетрады 5 через открытый элемент «И 9. Сдвиг числа AI в течение первых четырех тактов осуществляется без коррекции: содержимое тетрады 5 сдвигается в тетраду 2, содержимое тетрады 3 - в тетраду 4 н т. д. (поэтому нумерация тактов на фиг. 2 во втором цикле преобразования начинается с четвертого такта). В результате сдвигов н коррекции во втором цикле формируется число Az, .полученное в первом цикле искомое зиачение младшего десятичного разряда оказывается записанным в тетраде 5 (тетрада единиц), после чего на вход 17 подается запреш,а1ош,ий потенциал, а на вход 16 - разрешаюндий потенциал. Запреш.ающий потенциал поступает и па вход 14

тетрады 5, отключая от ее входа цепь подачи импульсов сдвига.

Аналогичным образом происходит преобразование в последуюш,их циклах, причем в течение первых четырех тактов каждого цикла € циркуляцией сдвиг чисел осуш,ествляется без коррекции, а нз последуюш,их циклов поочередно исключается по одной тетраде (начиная с тетрады 5) путем запреш,ения подачи импульсоБ сдвига.

В результате в сдвиговом регистре оказывается записанным двоично-десятичный код исходного числа Л, причем старший десятичный разряд - в тетраде 2.

Число циклов преобразования (исключая первый цикл, нредварительный) на единицу меньше числа тетрад, а число тактов в каждом цикле (начиная с третьего) на четыре меньше, чем в предыдущем цикле.

Исходное двоичное число может быть записано в регистр и параллельным кодом. В этом случае число циклов преобразования (исключая первый цикл) равно числу тетрад сдвигового регистра.

Управление устройством сводится к регулярному распределению разрешающих и запрещающих сигналов но управляющим входам 13-17.

0Предмет изобретения

Преобразователь двоичного кода в двоичнодесятичный, содержащий сдвиговый регистр, дешифратор коррекции и блок коммутации, выполненный на элементах «И, выходы ко° торых соединены с входами элемента «ИЛИ, выход последнего соединен с входом сдвигового регистра, вход каждого из элементов «И блока коммутации соединен с соответствующим управляющим входом устройства,

выходы разрядов первой тетрады сдвигового регистра соединены с входами дешифратора коррекции, выходы которого соединены с входами соответствующих разрядов той же тетрады, отличающийся тем, что, с целью

5 упрощеиия устройства, выход старщего разряда каждой тетрады сдвигового регистра, кроме первой тетрады, соединен с входом соответствующего элемента «И блока коммутации, входы всех тетрад сдвигового регистра,

0 кроме первой и второй тетрад, соединены с соответствующими управляющими входами устройства.

W 9

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1978 |

|

SU767749A1 |

| Преобразователь двоичного кодаВ дВОичНО-дЕСяТичНый | 1978 |

|

SU809150A1 |

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код | 1980 |

|

SU943703A1 |

| Преобразователь кодов | 1974 |

|

SU561957A2 |

| Преобразователь двоично-десятичной дроби в двоичную дробь | 1979 |

|

SU860053A1 |

| Преобразователь двоичного кода вдВОичНО-дЕСяТичНый и дВОичНО-дЕСяТичНОгОВ дВОичНый | 1979 |

|

SU849197A1 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1980 |

|

SU943702A2 |

| Преобразователь двоично-десятичных чисел в двоичные | 1982 |

|

SU1048469A1 |

| Преобразователь двоичного кода в двоично-десятичный и обратно | 1975 |

|

SU708344A1 |

| Преобразователь правильной двоично-десятичной дроби в двоичную дробь и целых двоичных чисел в двоично-десятичные | 1978 |

|

SU741260A1 |

Авторы

Даты

1975-09-30—Публикация

1973-05-24—Подача