(54) ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА В ДВОИЧНО-ДЕСЯТИЧНЫЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь правильной двоичной дроби в двоично-десятичную дробь и целых двоично-десятичных чисел в двоичные | 1978 |

|

SU734669A1 |

| Преобразователь двоичного кода вдВОичНО-дЕСяТичНый | 1979 |

|

SU842784A1 |

| Преобразователь правильной двоично-десятичной дроби в двоичную дробь и целых двоичных чисел в двоично-десятичные | 1978 |

|

SU741260A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1974 |

|

SU494744A1 |

| ПРОЦЕССОР ДЛЯ ЦИФРОВОЙ СИСТЕМЫ ОБРАБОТКИ ДАННЫХ | 1971 |

|

SU305477A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1973 |

|

SU486314A1 |

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код | 1980 |

|

SU943703A1 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА В ДВОИЧНО-ДЕСЯТИЧНЫЙ | 1972 |

|

SU434404A1 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1978 |

|

SU767749A1 |

| Устройство для вычитания двоично-десятичных кодов | 1982 |

|

SU1043640A1 |

I

Изобретение относится к автоматике и цифровой вычислительной технике и может быть использовано при построении двоично-десятичных преобразователей.

Известен преобразователь двоичного кода в двоично-десятичный, содержащий сдвиговый регистр, состоящий из последовательно соединенных тетрад, блоков коррекции, блоки коммутации и синхронизации 1.

Недостаток известного преобразователя состоит в относительно низком быстродействии, связанном с необходимостью двух тактов на один шаг преобразования, а также в сложности преобразователя, связанной с наличием блоков анализа содержимого тетрады.

Наиболее близким к предлагаемому по технической сущности является преобразователь двоичного кода в двоично-десятичный, содержащий сдвиговый регистр, выполненный в виде п последовательно соединенных тетрад,, где п-число разрядов двоично-десятичного кода, п блоков коррекции, выходы трех младщих разрядов каждого из которых соединены с информационными входами трех старших разрядов соответствующих

тетрад, выход старшего разряда i-ro (i 1 - (п-1) блока коррекции соединен со входом младшего разряда (1-ь1)-ой тетрады, входы каждого блока коррекции соединены с разрядными выходами соответствующей тетрады 2.

Недостаток данного преобразователя состоит в относительно большой сложности, связанной с трудностью применения блоков повышенной степени интеграции.

Цель изобретения - упрощение преобразователя.

Поставленная цель достигается тем, что в преобразователь двоичного кода в двоично-десятичный, содержащий сдвиговый регистр, выполненный в виде п последовательно соединенных тетрад, где п-число разрядов двоично-десятичного кода, п блоков коррекции, выходы трех младщих разрядов каждого из которых соединены с информационными входами трех старщих разрядов соответствующих тетрад, выход старщего

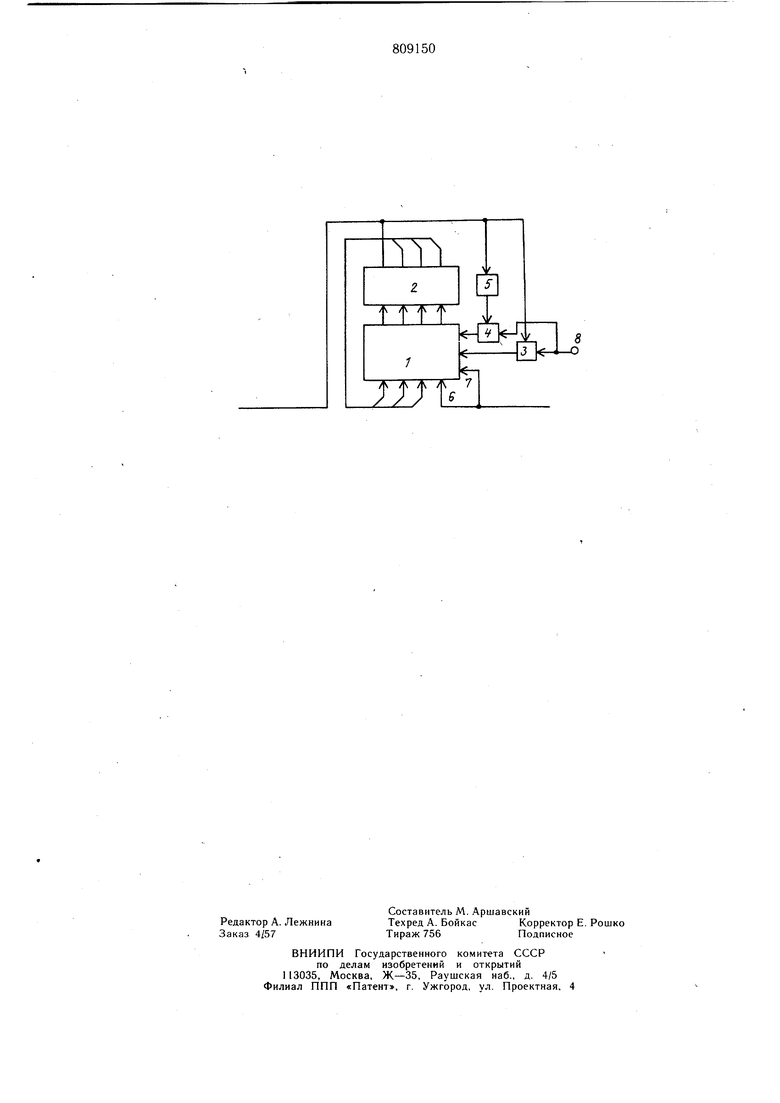

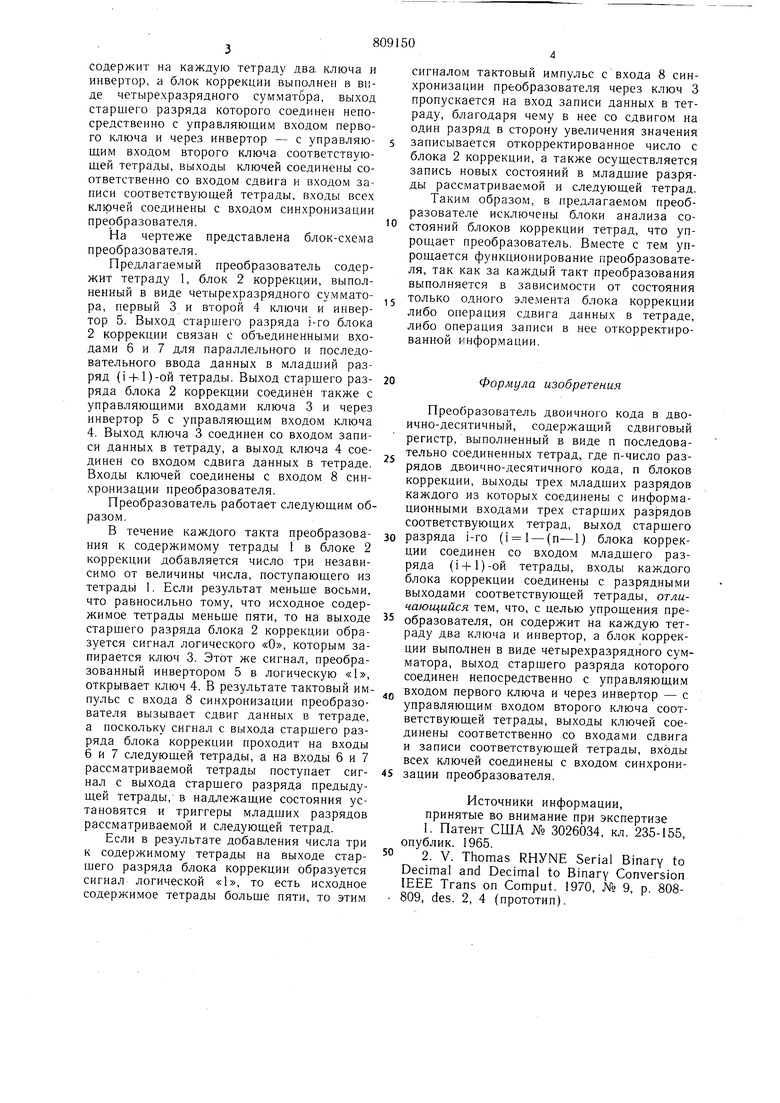

разряда -го (i i - (п-1) блока коррекции соединен со входом младщего разряда (1 + 1)-ой тетрады, входы каждого блока коррекции соединены с разрядными выходами соответствующей тетрады, дополнительно содержит на каждую тетраду два. ключа и инвертор, а блок коррекции выполнен в виде четырехразрядного сумматбра, выход старшего разряда которого соединен непосредственно с управляющим входом первого ключа и через инвертор - с управляющим входом второго ключа соответствующей тетрады, выходы ключей соединены соответственно со входом сдвига и входом записи соответствующей тетрады, входы всех ключей соединены с входом синхронизации преобразователя. На чертеже представлена блок-схема преобразователя. Предлагаемый преобразователь содержит тетраду 1, блок 2 коррекции, выполненный в виде четырехразрядного сумматора, первый 3 и второй 4 ключи и инвертор 5. Выход старшего разряда i-ro блока 2 коррекции связан с объединенными входами 6 и 7 для параллельного и последовательного ввода данных в младщий разряд (i-f. 1)-ой тетрады. Выход старшего разряда блока 2 коррекции соединен также с управляющими входами ключа 3 и через инвертор 5 с управляющим входом ключа 4. Выход ключа 3 соединен со входом записи данных в тетраду, а выход ключа 4 соединен со входом сдвига данных в тетраде. Входы ключей соединены с входом 8 синхронизации преобразователя. Преобразователь работает следующим образомВ течение каждого такта преобразоваНИЯ к содержимому тетрады 1 в блоке 2 коррекции добавляется число три независимо от величины числа, поступающего из тетрадь 1. Если результат меньше восьми, что равносильно тому, что исходное содержимое тетрады меньше пяти, то на выходе старшего разряда блока 2 коррекции образуется сигнал логического «О, которым запирается ключ 3. Этот же сигнал, преобразованный инвертором 5 в логическую «1, открывает ключ 4. В результате тактовый им пульс с входа 8 синхронизации преобразователя вызывает сдвиг данных в тетраде, а поскольку сигнал с выхода старшего разряда блока коррекции проходит на входы 6 и 7 следующей тетрады, а на входы 6 и 7 рассматриваемой тетрады поступает сигнал с выхода старшего разряда предыдушей тетрады, в надлежащие состояния установятся и триггеры младших разрядов рассматриваемой и следующей тетрад. Если в результате добавления числа три к содержимому тетрады на выходе старщего разряда блока коррекции образуется сигнал логической «1, то есть исходное содержимое тетрады больше пяти, то этим сигналом тактовый импульс с входа 8 синхронизации преобразователя через ключ 3 пропускается на вход записи данных в тетраду, благодаря чему в нее со сдвигом на один разряд в сторону увеличения значения записывается откорректированное число с блока 2 коррекции, а также осуществляется запись новых состояний в младшие разряды рассматриваемой и следующей тетрад. Таким образом, в предлагаемом преобразователе исключены блоки анализа состояний блоков коррекции тетрад, что упрощает преобразователь. Вместе с тем упрощается функционирование преобразователя, так как за каждый такт преобразования выполняется в зависимости от состояния только одного эле.мента блока коррекции либо операция сдвига данных в тетраде, либо операция записи в нее откорректированной информации. Формула изобретения Преобразователь двоичного кода в двоично-десятичный, содержащий сдвиговый регистр, выполненный в виде п последовательно соединенных тетрад, где п-число разрядов дЕ.оично-десятичного кода, п блоков коррекции, выходы трех младших разрядов каждого из которых соединены с информационными входами трех старших разрядов соответствующих тетрад, выход старщего разряда i-ro (i l - (п-1) блока коррекции соединен со входом младшего разряда (1+1)-ой тетрады, входы каждого блока коррекции соединены с разрядными выходами соответствующей тетрады, отличающийся тем, что, с целью упрощения преобразователя, он содержит на каждую тетраду два ключа и инвертор, а блок коррекции выполнен в виде четырехразрядного сумматора, выход старшего разряда которого соединен непосредственно с управляющим входом первого ключа и через инвертор - с управляющим входом второго ключа соответствующей тетрады, выходы ключей соединены соответственно со входами сдвига и записи соответствующей тетрады, входы всех ключей соединены с входом синхронизации преобразователя. Источники информации, принятые во внимание при экспертизе I. Патент США № 3026034, кл. 235-155, опублик. 1965. 2. V. Thomas RHVNE Serial Binary to Decimal and Decimal to Binary Conversion IEEE Trans on Comput. 1970, № 9, p. 808809, des. 2, 4 (прототип).

vn

A

k-N.

5 -О

77;

Авторы

Даты

1981-02-28—Публикация

1978-07-31—Подача