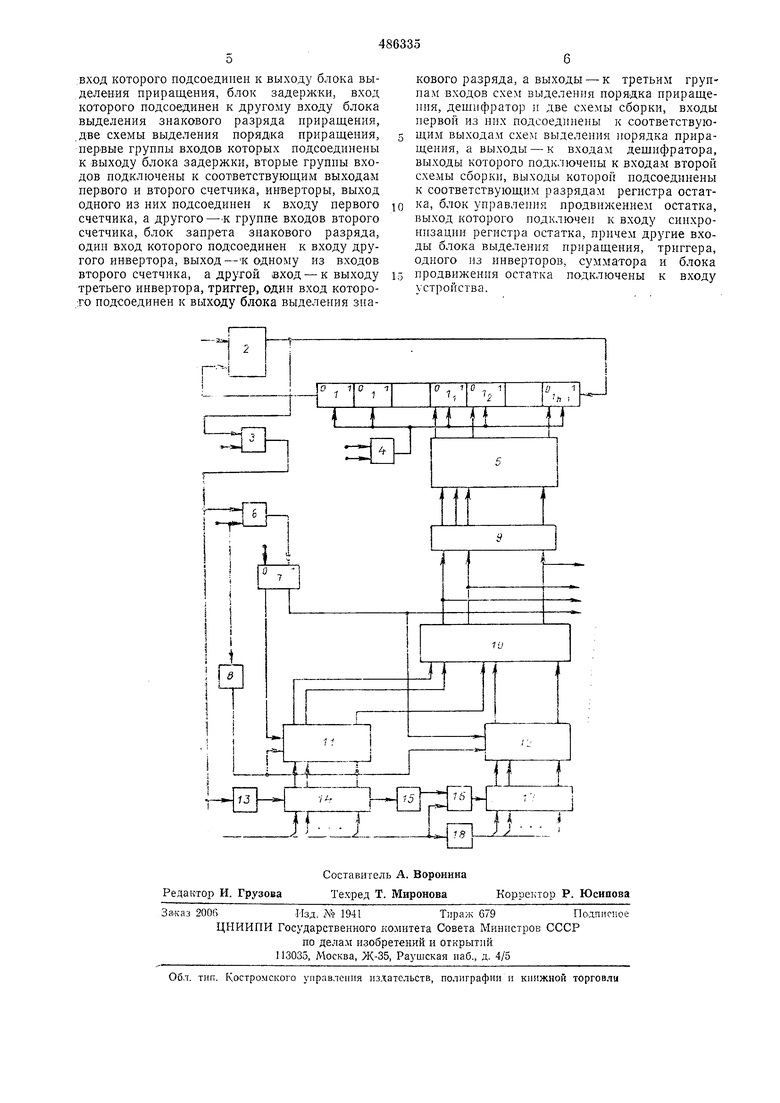

ны к соответствующим выходам схем выде; ения порядка приращения, а выходы - к входам дещпфратора, выходы которого соединены с входами Второй схемы сборки. Выходы второй схемы сборки гюдсоедииены к соответствующнм разрядам регистра остатка. Выход блока уиравлеиня иродвижеинем остатка подключен к входу сннхронизацин регистра остатка, а другие в.ходы блока выделения приращеиия, триггера, одного из инверторов, сумматора II блока продвижения остатка - к входу устройства. При этом прнращеиия, которые меньше кванта (веса младшего разряда иодылтегральной функции) накапливаются в остатке.

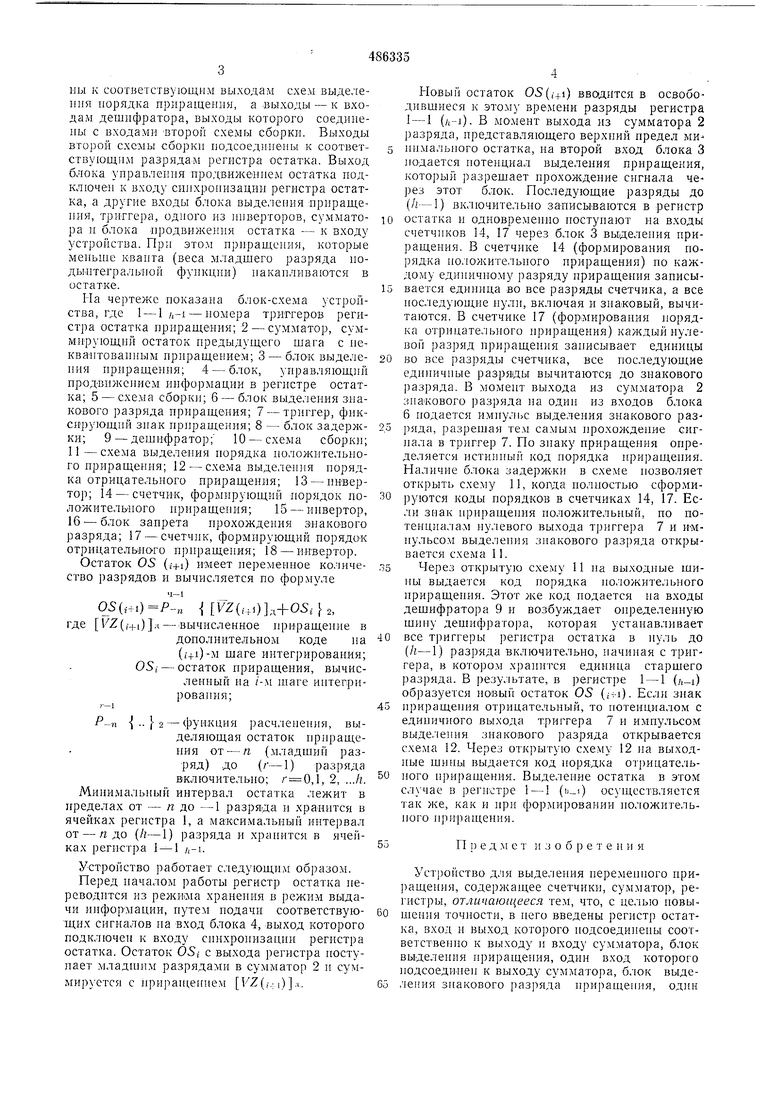

На чертеже показаиа блок-схема устройства, где 1 - 1 /г-1 - номера триггеров регистра остатка приращения; 2 - сумматор, суммирующий остаток предыдущего шага с некваитованным ирнращение.м; 3 - бло-к выделеиия ириращення; 4 - блок, уиравляющий продвижением информации в регистре остатка; 5 - схе.ма сборки; 6 - блок выделения зиакового разряда приращения; 7 - триггер, фиксирующий знак прирао ения; 8 - блок задержки; 9 - дешифратор; 10 - схема сборки; 11-схема выделеиия порядка ноложнтельного приращения; 12 - схе.ма выделення иорядка отрицательного приращения; 13 - инвертор; 14 - счетчнк, формирующий порядок положителыюго приращения; 15 - инвертор, 16 - блок запрета прохождения знакового разряда; 17 - счетчик, формирующий порядок отрицательного приращения; 18 - инвертор.

Остаток OS (i+i) имеет переменное количество разрядов и вычисляется по формуле

05(,.-i) Я-, l/Z(,.,i)д+05, 2, где К2(,-+|)д- вычисленное приращеиие в

дополнительном коде на (i+i)-M шаге интегрирования; OSi - остаток приращения, вычисленный иа /-М шаге иптегрировапия;

7--1

) 2 - функция расчленения, выделяющая остаток прнращеппя от - п (.младший разряд) до (г-1) разряда включительно; ,1, 2, .../;. Минимальный интервал остатка лежит в пределах от - я до -1 разряда и хранится в ячейках регистра 1, а макси.мальный интервал от - л до (/г-1) разряда и храннтся в ячейках регистра /;-i.

Устройство 1аботает следующи.м образом.

Перед началом работы регистр остатка нереводится из режиаит хранеиня в режим выдачи информации, иутем нодачи соответствующи.х сигналов на вход блока 4, выход которого подключен к входу синхронизации регистра остатка. Остаток 05; с выхода регистра г оступает младн1им разрядамн в сумматор 2 и суммируется с нриран1,еннем VZd,.

Новый остаток OS((ii) вводится в освободившиеся к этому времени разряды регистра 1 - 1 (л-i). В мо.мент вы.хода из сумматора 2 разряда, представляющего верхний предел минимального остатка, на второй вход блока 3 подается потенциал выделения приращения, который разрешает прохождение сигнала через этот блок. Последующие разряды до (Л-1) включительно записываются в регистр остатка и одновременно поступают на входы счетчиков 14, 17 через блок 3 выделения приращения. В счетчике 14 (формироваиия порядка ноложительиого ириращения) по каждому единичному разряду ириращения записывается единица во все разряды счетчика, а все носледующне нули, включая и знаковый, вычитаются. В счетчике 17 (формирования порядка отрицательиого нриращения) каждый нулевой разряд нриращения занисывает единицы во все раз)яды счетчика, все последующие едн1П1чные разряды вычитаются до знакового разряда. В момент выхода из су.м.лштора 2 знакового разряда на один из входов блока 6 нодается имнульс выделения знакового раз)яда, разрешая тела самым прохождение сигнала в триггер 7. По знаку приращения определяется истинный код порядка нриращепия. Наличие блока задерж-ки в схеме позволяет открыть схему 11, когда полностью сформируются коды порядков в счетчиках 14, 17. Если знак нрнращеиня положительный, по потенциалам нулевого выхода триггера 7 и имнульсом выделения знакового разряда открывается схе.ма 11.

Через открытую схему 11 на выходные шины выдается код порядка положительного приращення. Этот же код нодается на входы дешифратора 9 и возбуждает оиределенную шипу деншфратора, которая устанавливает все триггеры регистра остатка в нуль до (h-1) разряда включительно, начииая с триггера, в котором хранится единица старшего разряда. В результате, в регистре 1 - 1 () образуется новый остаток 05 (i+i). Если знак нриращепия отрицательный, то потенциалом с единичного выхода триггера 7 п импульсом выделения знакового разряда открывается схема 12. Через открытую схему 12 на выходные шины выдается код порядка отрицательного нриращения. Выделение остатка в этом случае в 1 - 1 {) осуществляется так же, как и ири формировании иоложительпого прпращения.

П р е д м е т и з о б р е т е и и я

Устройство для выделения неремеппого нриращения, содержащее счетчики, сум.матор, регистры, отличаю11{ееся тем, что, с целью новышения точности, в него введены регистр остатка, вход и вы.ход которого иодсоединены соответственно к выходу 1 входу сумматора, блок выделения нриращения, один вход которого подсоединен к выходу сумматора, блок выделения знакового )яда приращения, один

| название | год | авторы | номер документа |

|---|---|---|---|

| ЭКСТРАПОЛЯТОР с ОКРУГЛЕНИЕМ ПРИРАЩЕНИЙдля | 1970 |

|

SU279192A1 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1971 |

|

SU291216A1 |

| Интегратор потоков многоразрядных приращений | 1975 |

|

SU548869A1 |

| УСТРОЙСТВО для СЖАТИЯ ВХОДНОЙ ИНФОРМАЦИИ | 1972 |

|

SU324638A1 |

| ИНТЕГРИРУЮЩЕЕ УСТРОЙСТВО | 1971 |

|

SU294156A1 |

| Цифровой интегратор | 1975 |

|

SU661572A1 |

| Интегрирующее устройство | 1990 |

|

SU1727122A1 |

| Цифровой интегратор | 1975 |

|

SU650084A1 |

| Устройство для выделения приращения | 1973 |

|

SU474024A1 |

| Устройство для решения систем линейных дифференциальных уравнений | 1985 |

|

SU1252792A1 |

Авторы

Даты

1975-09-30—Публикация

1973-04-27—Подача