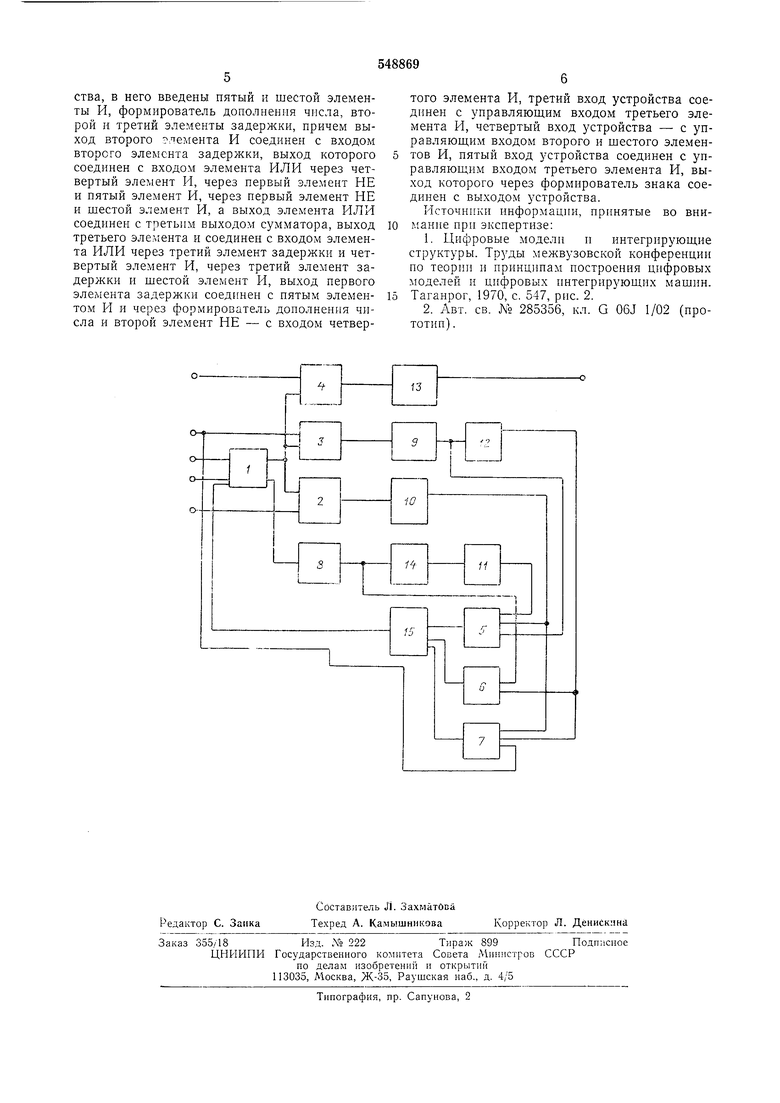

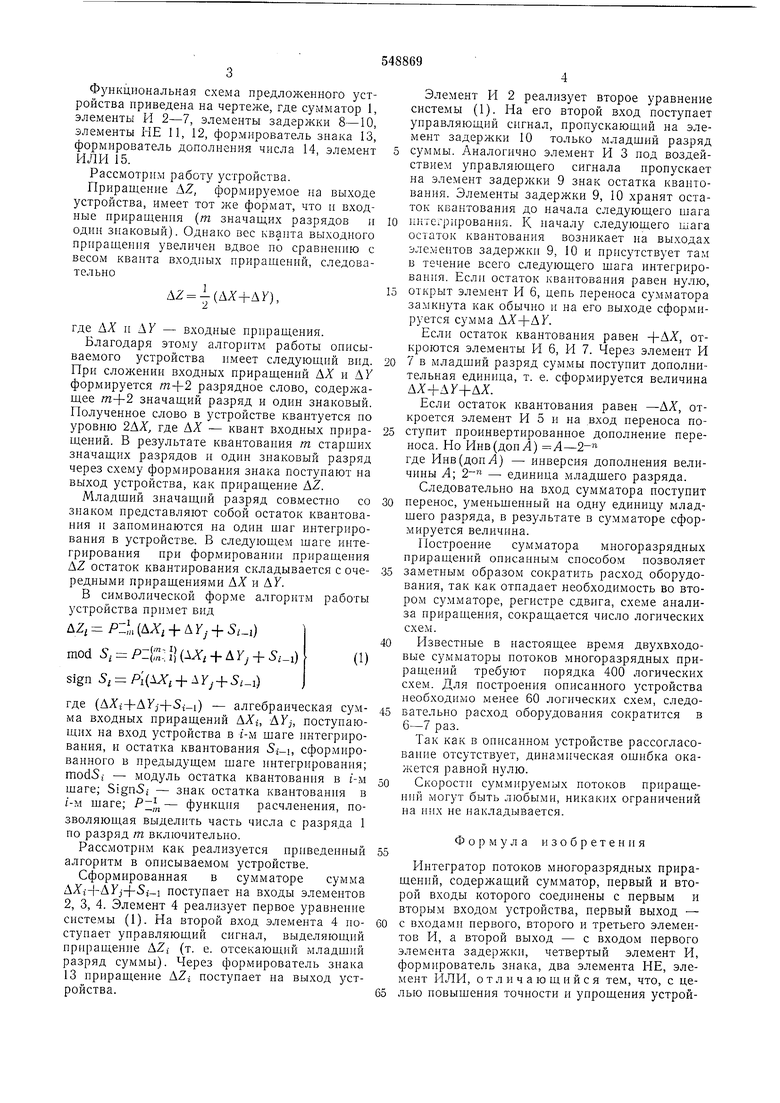

Ф)нкциональная схема предложенного устройства приведена на чертеже, где сумматор 1, элементы И 2-7, элементы задержки 8-10, элементы НЕ 11, 12, формирователь знака 13, формирователь дополнения числа 14, элемент ИЛР1 15. Рассмотрим работу устройства. Приращение AZ, формируемое на выходе устройства, имеет тот же формат, что и входные нриращения (т значащих разрядов и один знаковый). Однако вес кванта выходного приращення увеличен вдвое но сравнению с весом кванта входных ирирашений, следовательноД2 -(), где Д и ДУ - входные нриращения. Благодаря этому алгоритм работы описываемого устройства имеет следующий вид. При сложении входных нриращений Д и ДУ формируется т+2 разрядное слово, содержащее т-|-2 значащий разряд и один знаковый. Полученное слово в устройстве квантуется по уровню 2ДА, где ДА - квант входных приращений. В результате квантования т старших значащих разрядов и один знаковый разряд через схему формирования знака постунают на выход устройства, как приращение Д2. Младший значащий разряд совместно со знаком нредставляют собой остаток квантования и запоминаются на один шаг интегрирования в устройстве. В следующем шаге интегрирования нри формировании приращения ДЛ остаток квантирования складывается с очередными прнращениями ДХ и ДК В символической форме алгоритм работы устройства примет вид ( + Si,i mod 5, PZ{;I: Jl (Л + A Г; + 5,) sign Si P(Xi + + ) где (ДАг+ДУз+ г-) - алгебраическая сумма входных нриращений ДА;, ДУ, поступающих на вход устройства в f-м шаге ннтегрирования, и остатка квантования , сформированного в предыдущем шаге интегрирования; mod5i - модуль остатка квантования в i-м шаге; SignS; - знак остатка кваитовання в г-м шаге; - функцня расчленення, позволяюшая выделить часть числа с разряда 1 по разряд т включительно. Рассмотрим как реализуется приведенный алгоритм в описываемом устройстве. Сформированная в сумматоре сумма Д гЧ-ДУ + г- поступает на входы элементов 2, 3, 4. Элемент 4 реализует первое уравнение системы (1). На второй вход элемента 4 поступает управляющий сигнал, выделяющий нриращеиие Д21 (т. е. отсекающий младший разряд суммы). Через формирователь знака 13 приращение Д7г поступает на выход устройства. Элемент Н 2 реализует второе уравнение системы (1). На его второй вход поступает управляющнй сигнал, пропускающий на элемент задержки 10 только младший разряд суммы. Аналогично элемент И 3 под воздействием управляющего сигнала иропускает на элемент задержки 9 знак остатка квантования. Элементы задержки 9, 10 хранят остаток квантования до начала следующего шага интегрирования. К началу следующего шага остаток квантования возникает на выходах элементов задержкн 9, 10 и присутствует там в течение всего следзющего шага интегрирования. Если остаток квантования равен нулю, открыт элемент П 6, цепь переноса сумматора замкнута как обычно и на его выходе сформируется сумма . Если остаток квантования равен , откроются элементы И 6, И 7. Через элемент И 7 в младший разряд суммы постуиит дополнительная единнца, т. е. сформируется величина д +ду+д;. Если остаток квантования равен , откроется элемент И 5 и на вход переноса поступит проинвертированное донолнение переноса. Но Инв{донЛ) Л-2- где Инв(допЛ) - инверсия дополнения величины А; 2 - единица младшего разряда. Следовательно на вход сумматора поступит перенос, уменьшенный на одну единицу младшего разряда, в результате в сумматоре сформируется величина. Построение сумматора многоразрядных приращений описанным способом позволяет заметным образом сократить расход оборудования, так как отпадает необходимость во втором сумматоре, регистре сдвига, схеме анализа приращения, сокращается число логических схем. Известные в настоящее время двухвходовые сумматоры нотоков многоразрядных приращеиий требуют порядка 400 логических схем. Для построения описанного устройства необходимо менее 60 логических схем, следовательно расход оборудования сократится в 6-7 раз. Так как в оиисанном устройстве рассогласование отсутствует, динамическая ошибка окажется равной нулю. Скорости суммируемых потоков приращений могут быть любыми, никаких ограничений на них не накладывается. Формула изобретения Интегратор потоков многоразрядных приращений, содержащий сумматор, первый и второй входы которого соединены с первым и вторым входом устройства, первый выход - с входами первого, второго и третьего элементов И, а второй выход - с входом нервого элемента задержкн, четвертый элемент И, формирователь зиака, два элемента НЕ, элемент ИЛИ, отличающийся тем, что, с целью повышения точности и упрощения устройства, в него введены пятый и шестой элементы И, формирователь дополнения числа, второй и третий элементы задержки, причем выход второго элемента И соединен с входом второго элемента задержки, выход которого соединен с входом элемента ИЛИ через четвертый элемент И, через первый элемент НЕ и пятый элемент И, через первый элемент ИЕ и шестой элемент И, а выход элемента ИЛИ соединен с третьим выходом сумматора, выход третьего элемента и соединен с входом элемента ИЛИ через третий элемент задержки и четвертый элемент И, через третий элемент задержки н шестой элемент И, выход первого элемента задержки соединен с пятым элементом И и через формирователь дополнения числа и второй элемент НЕ - с входом четвертого элемента И, третий вход устройства соединен с управляющим входом третьего элемента И, четвертый вход устройства - с управляюш;им входом второго и шестого элементов И, пятый вход устройства соединен с управляющим входом третьего элемента И, выход которого через формирователь знака соединен с выходом устройства.

Источники информации, принятые во внимание прн экспертизе:

1.Цифровые модели п интегрирующие структуры. Труды межвузовской конференции по теории н принщшам построения цифровых моделей н цифровых ннтегрирз-ющих машин.

Таганрог, 1970, с. 547, рис. 2.

2.Авт. св. № 285356, кл. G 06J 1/02 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для выделения переменного приращения | 1973 |

|

SU486335A1 |

| Интегроарифметическое устройство | 1987 |

|

SU1515162A2 |

| Интегрирующее устройство | 1990 |

|

SU1727122A1 |

| Интегрирующее устройство интегрирующей машины последовательного типа | 1974 |

|

SU526927A1 |

| Устройство для решения систем линейных дифференциальных уравнений | 1985 |

|

SU1252792A1 |

| Цифровой интегратор | 1975 |

|

SU650084A1 |

| Устройство для решения систем линейных дифференциальных уравнений | 1988 |

|

SU1525714A2 |

| Модуль интегрирующей вычислительной структуры | 1984 |

|

SU1257641A1 |

| Интегро-арифметическое устройство | 1977 |

|

SU746602A1 |

| Детерминированно-вероятностныйиНТЕгРАТОР | 1979 |

|

SU840859A1 |

f3

Авторы

Даты

1977-02-28—Публикация

1975-01-03—Подача