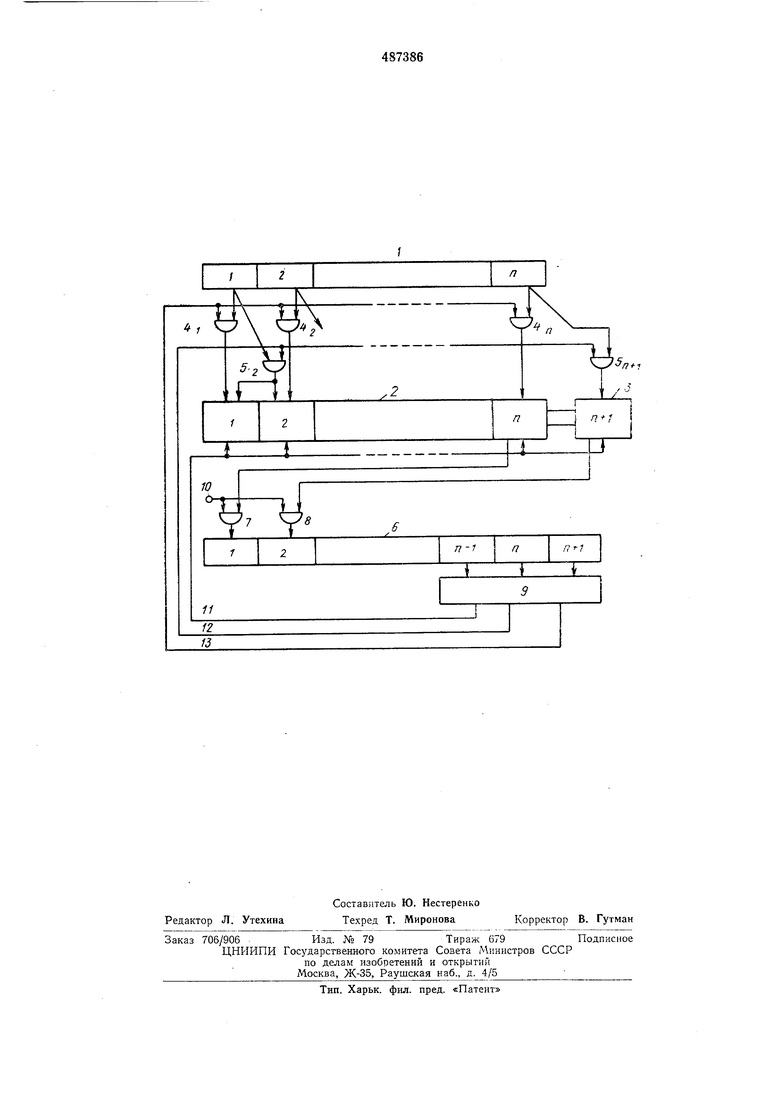

торе Р производится анализ (п-1), п, (п+{)го разрядов регистра множителя 6 для определения действий )Иад содержимым регистра множимого / и сумматаром 2, 3.

,При состоянии 011 или 100 (п-1), п, (п + 1)-то разрядов регистра 6 содержимое регистра / передается в cyMiMaTOp 2 без сдвига через первую группу схем «И . ПрИ оостояняи 001 или 010, ,или 101 или ПО (), п, (п + 1)-го разрядов регистра 6 содержимое регистра / передается в сумматор |2 и 3 со сдвигом вправо на один разряд через iBTOpyio группу схем «И Jg-5 + 1При состоянии 001 .или 010, или 011 (п-/), п, (n+)--:Q разрядов регистра 6 содержимое регистра 1 складывается с содержимым сумматора 2 :и , а при состоянии 100 «ли 101, или 110 выше указанных трех разрядов регистра 6 ;из содержимого сумматора 2 и 5 вычитается содержимое регистра /. После получения в сумм,аторе 2, 3 (я+1)-разрядного результата в регистре 6 в сумматоре 2, 3 производится сдвиг содерЖИМОГО -ка два разряда вправо. В освобождающиеся первый и второй разряды регистра 6 через схемы «И 7 и 5 1ПО сигналу шины 10 записывается п и (п + 1)-й разряды произведения, после чего (производится сдвиг содержимого сумматора 2, 3 на два разряда вправо.

В последующих циклах освобождающиеся разряды регистра 6 заполняются двумя разрядами младщей части частного произведен 1Я, образующимися в п и (л+1)-ом разрядах сумматора 2, 3. После выполнения га/2 циклов С« - число разрядов множителя) старщая часть (Произведения (1-:-/г разряды) находится в сумматоре 2, а младшая часть (п + -ь 2 га) - в регистре 6.

Формула изобретения

Устройство для умножения чисел в дополнительном .коде, содержащее fra + ,1)-разрядный регистр множителя, выходы (п-1)-го, п-го ;и (га-ь 1)-го разрядов которого соединены со в.ходамй дешифратора, первый выход которого соединен с первыми входами первой группы схем «И, вторые входы которых соединены соответственно с ;выходами га-разрядного регистра множимого, а выходы - с

соответствующими первыми входами «-разрядного сумматора, второй выход - с первыми входами второй группы схе.м «И, вторые входы которых соединены соответственно с выходами «-разрядного регистра множимого,

кроме га-го разряда, а выходы - с соответствующими вторыми входами га-разрядного сумматора, третьи входы которого подключены к третьему выходу дешифратора, отличающееся тем, что, с целью увеличения точности,

.оно содержит (п+)-к разряд сумматора, первый вход которого соединен с выходом соответствующей схемы «И из второй группы схем, первый вход -которой подключен ко второму выходу дешифратора, второй вход - к

выходу га-го разряда регистра множимого, второй вход п + 1-го сумматора - к третьему выходу дешифратора, а выходы (rt-h)-ro и га-го разрядов сумматора подключены соответственно к первым входам третьей группы

Схем «И, вторые входы которых связаны с шиной управления устройства, а ;зыходы подключены соответственно «о входам второго и первого разрядов регистра множителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения @ -разрядных чисел | 1986 |

|

SU1374217A1 |

| Устройство для умножения | 1983 |

|

SU1130859A1 |

| Устройство для умножения | 1981 |

|

SU1012245A1 |

| Устройство для умножения комплексных чисел | 1986 |

|

SU1388851A1 |

| Устройство для умножения двоичных чисел | 1989 |

|

SU1784973A1 |

| Устройство для умножения по модулю М=2 @ -1 | 1986 |

|

SU1383339A1 |

| Устройство для умножения | 1982 |

|

SU1136151A1 |

| Устройство для умножения десятичных чисел | 1984 |

|

SU1198514A1 |

| Устройство для умножения @ -разрядных чисел | 1981 |

|

SU1003077A1 |

| Устройство для умножения в избыточной четверичной системе счисления | 1983 |

|

SU1160399A1 |

Авторы

Даты

1975-10-05—Публикация

1973-10-05—Подача