:ыход триггера соединен со входом шестого элемента «И первой логической схемы, нулевой - со входами седьмого ,и восьмого элементов «PI первой логической схемы. В первой логической-схеме первыйИ второй управляющие входы модуля |Ооед1И1 ены со входами второго элемента «ИЛИ, выход которого соединен со входом пятого элемента «И. Второй вход последнего соединен через второй элемент «НЕ с выходОМ первого элемента «ИЛИ, соеднненного также со входо-м второго выходного элемента «ИЛИ, выход которого соед иен через третий элемент «ИЕ со зторым ВХОДОМ четзертого элемента «И. Третий логический вход модуля соединен со входом восьмого элемента «И первой логической Схемы ,и входом четвертого элемента «И второй логической схемы, выход которого СОединен со входом ее элемента «ИЛИ, к выходу которого под( второй выход модуля. Выход первого элемепта «НЕ соединен со 1зходами шестого и седьмого элементов «PI первой логической схемы. Четвертый логический вход модуля соединен со входами седьмого элемента «И первой логической схемы, четвертого элемеита «И второй логической схемы и четвертого элемента «ИЕ, выход которого соед.ииен со входами восьмого элемента «И первой логической схемы. Пятый управляющий вход модуля соединен со входом шестого элемента «И и входом пятого элемента «ИЕ, выход которого соединен со входом nepiBoro элемента «И первой логической схемы. Шестой уиравляюш.ий вход модуля соедииеи со входами второго, третьего и четвертого элементов «И второй логической схемы.

Это позволяет упростить схему модуля, л та-кже повысить его быстродействие за счсгг того, что сигнал нереноса в следу1ош,ий разряд образуется одповремешю с операцией сложения.

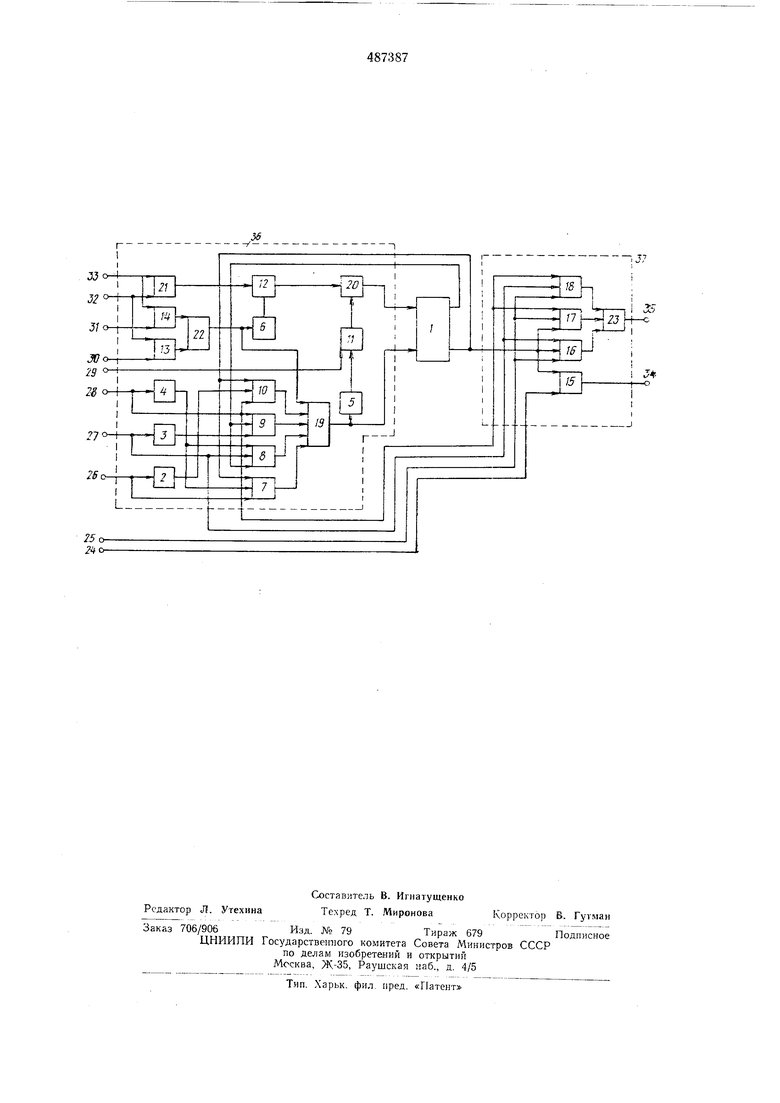

Схема модуля изображена на чертеже.

.Аодуль содержит тр.иггер /. элем(;;;ты «ИЕ 2-6, эломеиты «И 7-18. элементы «ИЛИ 19-23. входы 24-33 и выходы 34-35.

Элементы 2-6, 7-14, 19-22 объединены Б .пепвую логическую схему 36, а э.чемекты /5-18. 23 - во вторую логическую схему 37.

Входы 27. 28, 30 и 31 Я вляются логическими, а входы 25, 26, 24, 29, 32 ,и 33 - управЛЯЮЩ.ИМ1И.

На входы ,модуля подаются следующие сиг -:алы:

а,- - г-й разряд оператора (в.ход 28), Q/--1 - содержимое соседнего младшего разряда (вход 31,

Q/4-1 - содержимое соседнего старшего разряда (вход 30).

На входы 26, 27 подаются сигналы переноса ИЗ младшего разряда и другие переменные и константы в зависимости от реализуемой функции.

Соответствующая подача управляющих оягналов обеспечивает выполнение модулем

операций логического сложения, сдвига вправо и влево, логического умножения, ариф.метического сложения и сложения по модулю два, прямым и обратным кодами и

выдачи содержимого триггера / на выход, 34. ч одуль работает следующи.м образом. Ири подаче на вход 28 сигнала О;, иа вход 27 1копстаит «О и на вход 26 сигнала а;

на выходе элемента ;ИЛИ 19 реализуется функция

/ a,Q/ / afyi V u,Q, --си / Q,-,

которая устанавливает на триггере / результат, равный логической су.мме велич ;н а, и Q;. При этом сигналы на входах 29, 32 и 33 равны «О.

Ири подаче сигна,1а Qj-i на вход 31 и константы «1 на управляющий вход 33 величина Q;., проходит через элементы 14, 22 и 19 на зход становки триггера / в «1. Ири Qi О на выходе элемента «ИЕ 6 присутствует единичный сигнал, который разрешает прохождение -констапты «1 со входа 33 через элемент «И 12 на вход установки в «О триггера /. 3)то соответствует поступлению содержимого соседнего младшего (i-)-го разряда арифметической схемы в /-и разряд, т. е. сдвпгу вправо.

Ири выполнении этой операции сигналы на входах 2.6, 27 и 28 равны «. на входах 29,

32- «О.

Сдвиг влево происходит аналогично при подаче константы «1 на управляющий вход 32. Величина Q/+ проходит через элементы /Л, 22 к 19 на вход установки в «1 триггера /. При Q,-.j. сигнал на входе 32 через элементы 21, 12 и 20 поступает iia зход установки триггепа / з «О. При этом па ЗХОДР.Х 26, 27 и 28 сиг. ра1знь «1, а ::а входах 29,

33- «О.

Для ор-анизации операции логического М1:ожс-;пгя на входы 27, 28 подается сигнат С;, на входы 26, 32 и 33 - копста.нта «О, а на з.чод 29 - константа «1. При этом на выходе элемента «ИЛИ 19 реал.изуется зелпMfiiia а,: Q--. При а,- Q; 1 триггер / устаназлпзается в единичное состояние, прн и,- Q; 0 сигнал ка выходе элемента «НЕ 5 через 5.дементы //, 20 устанавливают триггер в нулевое состоян.ие.

Для организации операций арифметического сложения на вход 28 поступает сигнал а,-, на вход 27 - сигнал , на вход 26 - сигнал , на входы 32, 33 - константа «О, на входы 25, 29 - ашнстанта «1. При этом на выходе элемента «ИЛИ 19 реализуется

ФУРГКЦИЯ

/ a/Q.Z,, / ,Z,i /a;Q, / G/Q;Z/,,

которая представляет собой сумму по модулю

дзаотпеременных с,, Q,-, Z;(. Y.f f 1 триг65 rep 1 устанавливается в «1, а при f 0 тригrep / через элементы 5, II, 20 устаназлпзается в «О. Одновременно с реализацией фуккцин / на выходе элемента 19 сигнал перекоса формируется на выходе 34 модуля нри помощи элементов 16, 17, 18 я 23. Таким образом, в модуле реализуется параллельный перенос, что позволяет повысить быстродействие модуля.

Для сложения по мoдyv ю два на входы 26,

28подается Сигнал а;, на вход 27 - сигнал О; на в.ход 52, 33 - константа «О, а на вход

29- константа «1. Пр:И этом на выходе элемента 19 реализуется функция /

/ a,-Q,,-,

.которая представляет собой су.м,.му по модулю два от переменных С; и Q,-. При триггер устанавливается в единичное состояние, а при / 0 единичный сигнал па выходе эле.мента 5 через элементы 11, 20 устанавливает триггер в нулевое Состояние.

Для |приема информации прямым кодом на вход 28 (Подается сигнал С;, на входы 26, 27, 32 п 33 - константа «О, а на вход 29 - константа «1.

Переменная а,- пвступает на выход элемента 19. При Cj 1 триггер / устанавливается в единичное состояние, а при а,- О триггер через элементы 5, 11, 20 - в нулевое.

.Аналогично происходит Прием информации обратным кодом. При этом на вход 28 подается сигнал а,-, на входы 26, 27, 29 - константа «I, а на входы 32 и 33 - константа «О.

Для выдачи содержимого триггера 1 на выход 34 .модуля на входы 24, 26, 27 и 28 подается «онстанта «I, а aia входы 29, 32, и 33- константа «О. При этом содержимое тр.иггера / через элеме 1Т «И 15 поступает на выход 34 модуля. Операция 1выдачи может быть выполнена одновременно с любой рассмотренной выше операцией.

СодержЕмое триггера может быть стерто различными способами, в частности ир« выполнении операции приема прямым кодом при нулевом сигнале на входе 28.

П р е лТ м е т изобретения

Управляемый арифметический модуль, содержащий первую логическую схему, выполненную на элементах «И, «ПЛИ, «ПЕ, вторую логическую схему, выполненную на элементах «И и элементе «ПЛИ, логические и управляющие входы, триггер, входы которого соединены с выходами выходных элементо:: «ПЛИ первой логической схемы, а единичный выход - со входами первого, второго и третьего элементов «И второй логической схемы -и входом первого элемента «П первой логической схемы, входы которого элемента «И первой логической схемы соединены с первьгм управляющим и первым логическим

входами модуля, входы третьего элемента «И первой логической схемы соединены со вто pbiw управляющим и вторым логическим входами :модуля, третий управляющий вход соединен с входами четвертого элемента «П первой логической схемы, четвертый управляющий вход -.модуля соединен -со входом первого элемента «П второй логической схемы, выход которого соединен с лсрвы.м выходом модуля, третий логический вход соединен со входами первого элемента «НЕ, нервого элемента «П первой логической схемы и третьего элемента «П второй логической схемы, четвертый логический вход модуля соединен со входом второго элемента «П второй логической схемы, выходы второго и третьего элементов «П первой логической схемы соединены со входами ее первого элемента «ПЛП, вы.ходы второго и третьего элементов «П второй логической схемы соединены со входами ее элемента «ПЛП, выходы четвертого н пятого элементов «П первой логической схемы соедине1;ы со входами ее первого выходного элеглента «ПЛП, .выходы первого, щестого, седьмого и восьмого элементов «П первой логической схемы соединены со входами ее второго выходного элемента «ПЛП, отличающийся тем. что, с целью упрощения устройства и повышения его быстродействия, единичный вы.од триггера соединен со входом шестого элемента «П первой логической схемы, нулевой - со входами седьмого н восьNroro элементов «П первой логической схемы: 13 первой логической схеме первый (И второй управляющие входы модуля соединены со входами второго элемента «ПЛП, выход которого соединен со входом пятого элемента второй вход последнего соединен через второй элемент «ПЕ с выходом первого элемента «ПЛП, соединенного также со входом второго .выходного э.чсмента «Р1ЛП, выход «оторого Соединен через третий элеме т «ПЕ со вторым входом четвертого элемента третий логический вход модуля соединен со входом восьмого элемента «П первой логической схемы и ВХОДОМ четвертого элемента «П .второй логической схемы, выход которого соединен со входом ее элемента «ПЛП, к выходу которого подключен второй выход модуля; выход первого элел:ента «ПЕ соединен со входами шестого и седьмого элe eнтoв «П первой логической схемы; четвертый логи еский вход модуля соединен со входами седьмого элемента «П первой логической схемы,

5 четвертого элемента «П ВТОРОЙ логической схемы и четвертого элемента «НЕ, вы.ход которого соединен со входами восьмого элемента «П первой логической схемы; пятый упг.1зля:ощий в.ход модуля соединен со входом щестого элеме;-1та i входом пятого элемента «НЕ, выход .которого соединен со входом первого элемента «ГЬ первой логической схемы; шестой управляющий вход модуля соединен со входами второго, третьего и четвертого элементов «И второй логической схемы.

5

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1277105A1 |

| Центральный процессор | 1979 |

|

SU960830A1 |

| Устройство для формирования маршрута сообщения в однородной вычислительной системе | 1988 |

|

SU1501080A1 |

| Устройство контроля и управления реконфигурацией резервированной системы | 1989 |

|

SU1691990A1 |

| Устройство для управления | 1986 |

|

SU1418650A1 |

| Устройство для деления чисел без восстановления остатка | 1989 |

|

SU1605228A1 |

| Микропрограммное устройство для приоритетного обслуживания группы абонентов | 1984 |

|

SU1302277A1 |

| КОМБИНАЦИОННО-НАКАПЛИВАЮЩИЙ СУММАТОР | 2005 |

|

RU2292073C1 |

| Управляемый арифметический модуль | 1982 |

|

SU1062688A1 |

| Устройство для моделирования конечных автоматов | 1980 |

|

SU955080A1 |

Авторы

Даты

1975-10-05—Публикация

1973-10-23—Подача