Известны матричные устройства для сложения десятичных чисел, представленных в фазо-импульсном коде, содержащие матрицу сложения, схему запоминания переносов и схему образования полной суммы.

Предлагаемое устройство аналогичного назначения отличается тем, что оно содержит блок схем «ИЛИ, преобразователи фазоимиульсного представления чисел в пространственно-импульсное представление чисел и преобразователь пространственно-импульсного представления чисел в фазо-импульсное представление чисел, выходы которых подсоединены через матрицу сложения ко входам блока схем «ИЛИ и ко входам схемы запоминания переносов, выходы блока схем «ИЛИ подключены через схему образования полной суммы ко входам преобразователя нространственно-импульсного представления чисел в фазо-импульсное представление чисел.

Это позволяет упростить выполнение операции сложения чисел.

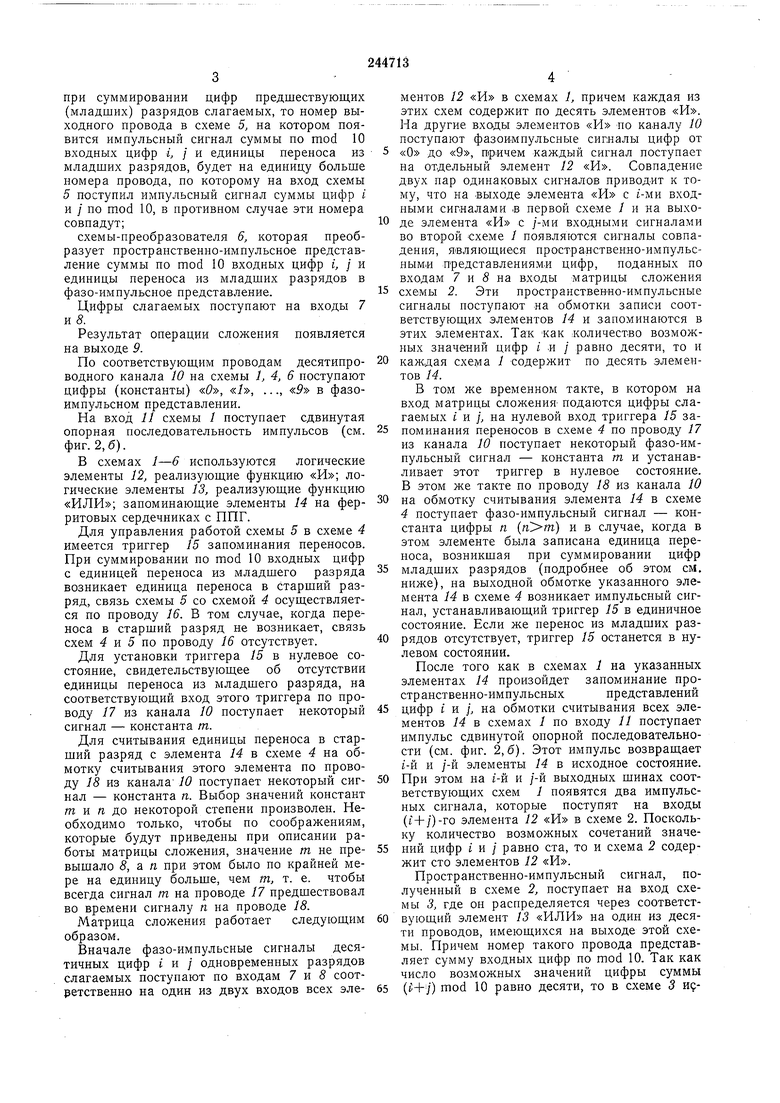

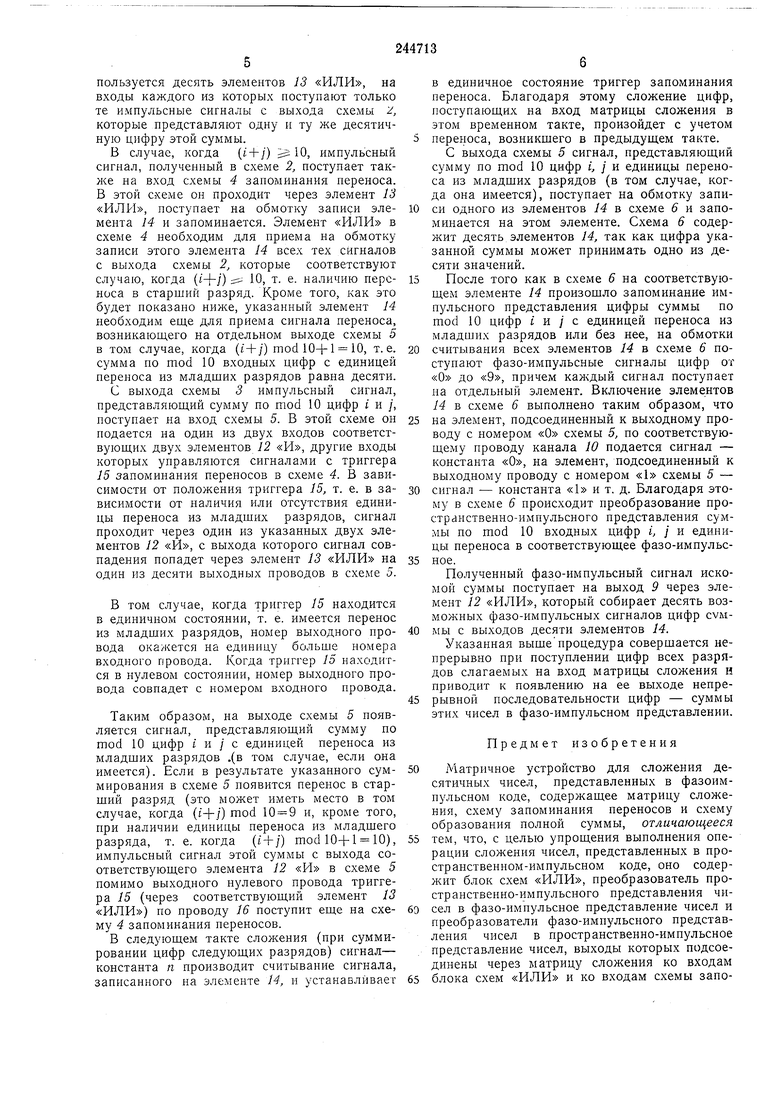

На фиг. 1 изображена блок-схема предлагаемого матричного устройства сложения.

Оно состоит:

из двух одинаковых схем-преобразователей 1, каждая из которых преобразует фазо-импульсное представление десятичной цифры (слагаемого), подаваемой на вход схемы, в

импульсный сигнал на одном из десяти проводов «О, «1, ..., «9, имеющихся на выходе этой схемы;

матрицы сложения - схемы 2, работа которой заключается в том, что каждой паре импульсных сигналов, поступающих с выходов схем / на вход схемы 2, соответствует импульсный сигнал на одном из ста проводов на выходе этой схемы; этот сигнал представляет собой сумму входных цифр;

блок-схемы «ИЛИ 3, работа которой состоит в том, что каждому импульсному сигналу, поступающему с выхода схемы 2 на вход схемы 3, соответствует импульсный сигнал на одном из десяти проводов «6, «7,..., «9, имеющихся -на выходе этой схемы; этот сигнал представляет сумму по mod 10 входных цифр;

схемы 4 запоминания переносов;

схемы 5 образования полной суммы, работа которой состоит в том, что каждому импульсному сигналу, поступающему по одному из десяти проводов с выхода схемы 3 на вход схемы 5, соответствует импульсный сигнал на одном из десяти проводов на выходе схемы 5. Номер провода, на котором появляется этот сигнал, зависит от положения схемы 4 запоминания переносов. Если схема 4 находится в положении, свидетельствующем

при суммировании цифр предшествующих (младших) разрядов слагаемых, то номер выходного провода в схеме 5, на котором появится импульсный сигнал суммы по mod 10 входных цифр i, I и единицы переноса из младших разрядов, будет на единицу больше номера провода, по которому на вход схемы 5 поступил импульсный сигнал суммы цифр / и / по mod 10, в противном случае эти номера совпадут;

схемы-преобразователя 6, которая преобразует пространственно-импульсное представление суммы по mod 10 входных цифр 1, j и единицы переноса из младших разрядов в фазо-импульсное представление.

Цифры слагаемых поступают на входы 7 и 5.

Результат операции сложения появляется на выходе 9.

По соответствуюш,им проводам десятипроводного канала 10 на схемы 1, 4, 6 поступают цифры (константы) «О, «1, ..., «9 в фазоимпульсном представлении.

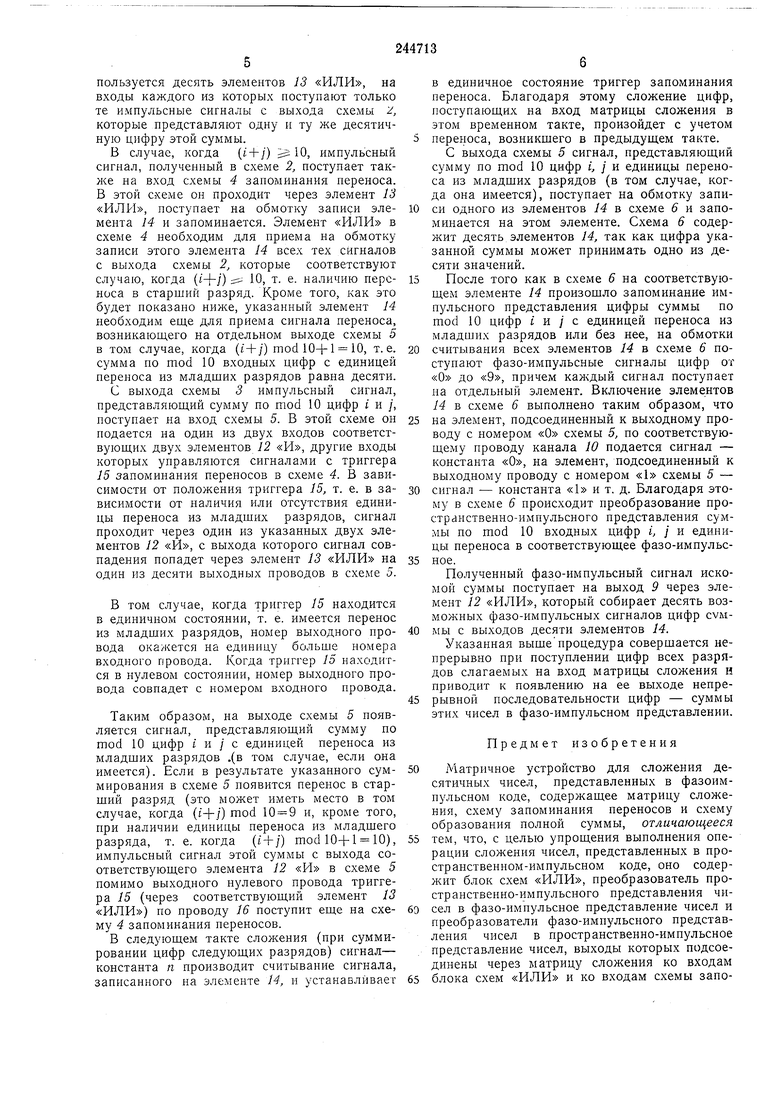

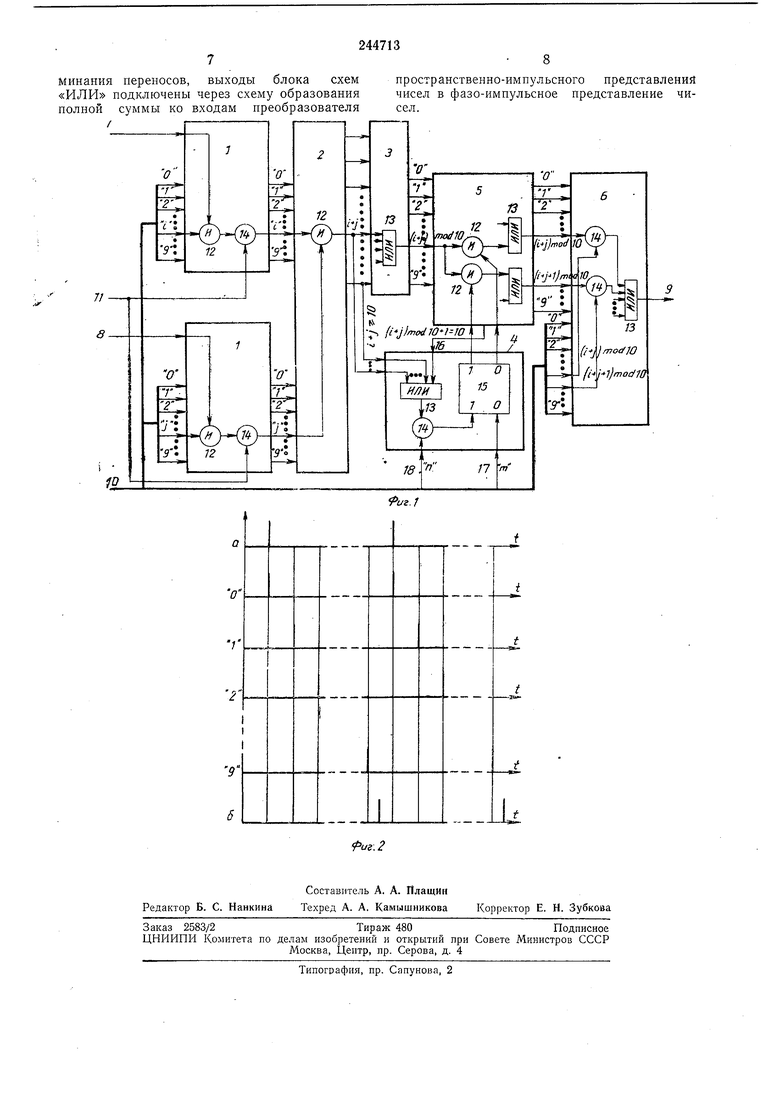

На вход 11 схемы / поступает сдвинутая опорная последовательность импульсов (см. фиг. 2,6).

В схемах /-6 используются логические элементы 12, реализуюш,ие функцию логические элементы 13, реализуюш,ие функцию запоминающие элементы 14 на ферритовых сердечниках с ППГ.

Для управления работой схемы 5 в схеме 4 имеется триггер 15 запоминания переносов. При суммировании по mod 10 входных цифр с единицей переноса из младшего разряда возникает единица переноса в старший разряд, связь схемы 5 со схемой 4 осуществляется по проводу 16. В том случае, когда переноса в старший разряд не возникает, связь схем 4 и 5 по проводу 16 отсутствует.

Для установки триггера 15 в нулевое состояние, свидетельствующее об отсутствии единицы переноса из младшего разряда, на соответствующий вход этого триггера по проводу 17 из канала 10 поступает некоторый сигнал - константа т.

Для считывания единицы переноса в старший разряд с элемента 14 в схеме 4 на обмотку считывания этого элемента по проводу 18 из канала 10 поступает некоторый сигнал - константа п. Выбор значений констант /п и ft до некоторой степени произволен. Необходимо только, чтобы по соображениям, которые будут приведены при описании работы матрицы сложения, значение т не превышало 8, а п при этом было по крайней мере на единицу больще, чем т, т. е. чтобы всегда сигнал т на проводе 17 предществовал во времени сигналу п на проводе 18.

Матрица сложения работает следующим образом.

ментов 12 «И в схемах 1, причем каждая из этих схем содержит по десять элементов «И. На другие входы элементов «И по каналу 10 поступают фазоимпульсные сигналы цифр от «о до «9, причем каждый сигнал поступает на отдельный элемент 12 «И. Совпадение двух пар одинаковых сигналов приводит к тому, что на выходе элемента «И с i-ми входными сигналами .в первой схеме / и на выходе элемента «И с /-ми входными сигналами во второй схеме / появляются сигналы совпадения, Я1вляющиеся пространственно-импульсными представлениям.и цифр, поданных по входам 7 и 8 на входы матрицы сложения

схемы 2. Эти пространственно-импульсные сигналы поступают на обмотки записи соответствующих элементов 14 и запоминаются в этих элементах. Так как количество возможных значений цифр / ,и / равно десяти, то и

каждая схема 1 содержит по десять элементов 14.

В том же временном такте, в котором на вход матрицы сложения- подаются цифры слагаемых i и /, на нулевой вход триггера 15 запоминания переносов в схеме 4 по проводу 17 из канала 10 поступает некоторый фазо-импульсный сигнал - константа т и устанавливает этот триггер в нулевое состояние. В этом же такте по проводу 18 из канала 10

на обмотку считывания элемента 14 в схеме 4 поступает фазо-импульсный сигнал - константа цифры п () и в случае, когда в этом элементе была записана единица переноса, возникшая при суммировании цифр

младших разрядов (подробнее об этом см. ниже), на выходной обмотке указанного элемента 14 в схеме 4 возникает импульсный сигнал, устанавливающий триггер 15 в единичное состояние. Если же перенос из младших разрядов отсутствует, триггер 15 останется в нулевом состоянии.

После того как в схемах 1 на указанных элементах 14 произойдет запоминание пространственно-импульсныхпредставлений

цифр t и I, на обмотки считывания всех элементов 14 в схемах 1 по входу 11 поступает импульс сдвинутой опорной последовательности (см. фиг. 2,6). Этот импульс возвращает j-й и /-Й элементы 14 в исходное состояние.

При этом на i-й и /-и выходных щинах соответствующих схем 1 появятся два импульсных сигнала, которые поступят на входы (i + /)-ro элемента 12 «И в схеме 2. Поскольку количество возможных сочетаний значеНИИ цифр t и / равно ста, то и схема 2 содержит сто элементов 12 «И.

Пространственно-импульсный сигнал, полученный в схеме 2, поступает на вход схемы 3, где он распределяется через соответствующий элемент 13 «ИЛИ на один из десяти проводов, имеющихся на выходе этой схемы. Причем номер такого провода представляет сумму входных цифр по mod 10. Так как число возможных значений цифры суммы

пользуется десять элементов 13 «ИЛИ, на входы каждого из которых поступают только те импульсные сигналы с выхода схемы , которые представляют одну и ту же десятичную цифру этой суммы.

В случае, когда (i + /), импульсный сигнал, полученный в схеме 2, поступает также на вход схемы 4 запоминания нереноса. В этой схеме он проходит через элемент 13 «ИЛИ, поступает на обмотку записн элемента 14 и запоминается. Элемент «ИЛИ в схеме 4 необходим для приема на обмотку записи этого элемента 14 всех тех сигналов с выхода схемы 2, которые соответствуют случаю, когда (i+/) : 10, т. е. наличию персноса в старший разряд. Кроме того, как это будет показано ниже, указанный элемент 14 необходим еще для приема сигнала переноса, возникающего на отдельном выходе схемы 5 в том случае, когда (i+j) mod 10+1 10, т.е. сумма но mod 10 входных цифр с единицей нереноса из младших разрядов равна десяти.

С выхода схемы 3 импульсный сигнал, представляющий сумму по mod 10 цифр i и /, поступает на вход схемы 5. В этой схеме он подается на один из двух входов соответствующих двух элементов 12 «И, другие входы которых управляются сигналами с триггера 15 запоминания переносов в схеме 4. В зависимости от положения триггера 15, т. е. в зависимости от наличия или отсутствия единицы переноса из младших разрядов, сигнал проходит через один из указанных двух элементов 12 «И, с выхода которого сигнал совпадения попадет через элемент 13 «ИЛИ на один из десяти выходных проводов в схеме 5.

В том случае, когда триггер 15 находится в единичном состоянии, т. е. имеется перенос из младших разрядов, номер выходного провода окажется на единицу больше номера входного провода. Когда триггер 15 находится в нулевом состоянии, номер выходного провода совпадет с номером входного провода.

Таким образом, на выходе схемы 5 появляется сигнал, представляющий сумму но mod 10 цифр i и / с единицей переноса из младших разрядов .(в том случае, если она имеется). Если в результате указанного суммирования в схеме 5 появится перенос в старший разряд (это может иметь место в том случае, когда (i+/) mod 10 9 и, кроме того, при наличии единицы переноса из младщего разряда, т. е. когда (i + /) mod 10+1 10), импульсный сигнал этой суммы с выхода соответствующего элемента 12 «И в схеме 5 помимо выходного нулевого провода триггера 5 (через соответствующий элемент 13 «ИЛИ) по проводу 16 поступит еще на схему 4 запоминания нереносов.

В следующем такте сложения (при суммировании цифр следующих разрядов) сигнал- константа п производит считывание сигнала, записанного на элементе 14, н устанавливает

в единичное состояние триггер запоминания переноса. Благодаря этому сложение цифр, поступающих на вход матрицы сложения в этом временном такте, произойдет с учетом переноса, возникшего в предыдущем такте.

С выхода схемы 5 сигнал, представляющий сумму по mod 10 цифр i, j и единицы переноса из младших разрядов (в том случае, когда она имеется), поступает на обмотку записи одного из элементов 14 в схеме 6 и запоминается на этом элементе. Схема 6 содерл ит десять элементов 14, так как цифра указанной суммы может принимать одно из десяти значений.

После того как в схеме 6 на соответствующем элементе 14 произощло запоминание имнульсиого представления цифры суммы по mod 10 цифр t и / с единицей переноса из младших разрядов или без нее, на обмотки

считывания всех элементов 14 в схеме 6 поступают фазо-импульсные сигналы цифр от «О до «9, причем каждый сигнал поступает на отдельный элемент. Включение элементов 14 в схеме 6 выполнено таким образом, что

на элемент, подсоединенный к выходному проводу с номером «О схемы 5, по соответствующему проводу канала 10 подается сигнал - константа «О, на элемент, подсоединенный к выходному проводу с номером «1 схемы 5 -

сигнал - константа «1 и т. д. Благодаря этому в схеме 6 происходит преобразование пространственно-импульсного представления суммы по mod 10 входных цифр i, j и единицы переноса в соответствующее фазо-импульсное.

Полученный фазо-импульсный сигнал искомой суммы поступает на выход 9 через элемент 12 «ИЛИ, который собирает десять возможных фазо-импульсных сигналов цифр CVMмы с выходов десяти элементов 14.

Указанная выщенроцедура совершается непрерывно при поступлении цифр всех разрядов слагаемых на вход матрицы сложения н приводит к появлению на ее выходе непрерывпой последовательности цифр - суммы этих чисел в фазо-импульсном представлении.

Предмет изобретения

Матричное устройство для сложения десятичных чисел, представленных в фазоимпульсном коде, содержащее матрицу сложения, схему запоминания переносов и схему образования полной суммы, отличающееся

тем, что, с целью упрощения выполнения операции сложения чисел, представленных в пространственном-импульсном коде, оно содержит блок схем «ИЛИ, преобразователь пространственно-импульсного представления чисел в фазо-импульсное представление чисел и преобразователи фазо-импульсного представления чисел в пространственно-импульсное представление чисел, выходы которых подсоединены через матрицу сложения ко входам минания переносов, выходы блока схем «ИЛИ подключены через схему образования полной суммы ко входам преобразователя пространственно-нмпульсного представления чисел в фазо-импульсное представление чисел.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ДЕСЯТИЧНЫХ ЧИСЕЛ, ВЫРАЖЕННЫХ В ФАЗО-ИМПУЛЬСНОМ КОДЕ | 1967 |

|

SU223463A1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2395833C2 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2009 |

|

RU2410745C1 |

| УСТРОЙСТВО для СЛОЖЕНИЯ-ВЫЧИТАНИЯ ДЕСЯТИЧНЫХ ЧИСЕЛ | 1972 |

|

SU332459A1 |

| Устройство для умножения | 1980 |

|

SU960805A1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2386998C1 |

| Устройство для деления п-разрядных десятичных чисел | 1976 |

|

SU742933A1 |

| Арифметическое устройство с плавающей точкой | 1985 |

|

SU1259248A1 |

| Устройство для деления десятичных чисел | 1976 |

|

SU744562A1 |

| УСТРОЙСТВО для СЛОЖЕНИЯ и ВЫЧИТАНИЯ | 1971 |

|

SU306462A1 |

Даты

1969-01-01—Публикация