1

Изобретение относится к вычислительной технике и, в частности, к организации структур селекторных каналов ввода-вывода.

Известны селекторные каналы, содержащие блок управления канала, соединенный с соответствующими входами и выходами селекторного канала, регистр признаков операции, регистр адреса данных, регистр счета байтов, регистр состояния и блок управления интерфейсом, соединенные с блоком управления канала и с адресными и информационными шинами селекторного канала.

Недостатком известных селекторных каналов является сравнительно невысокое быстродействие.

Целью настоящего изобретения является повыщение быстродействия селекторного канала.

Поставленная цель достигается тем, что в селекторный канал введены регистр адреса последующего управляющего слова канала, блок формирования адреса управляющего слова канала и блок сравнения, первый и второй входы которого подключены соответственно к выходам регистра адреса данных и регистра адреса последующего управляющего слова канала, выход блока сравнения соединен с нервыми входами блока управления канала и блока формирования адреса управляющего слова канала, второй вход которого,

первый вход регистра адреса последующего управляющего слова канала и третий вход блока сравнения подключены к первому выходу блока управления канала, выход б.юка формирования адреса управляющего слова канала и второй вход регистра адреса последующего управляющего слова канала соединены с адресными информационными щинами канала соответственно.

Это позволяет увеличить скорость передачи данных при использовании режима зацепления по данным.

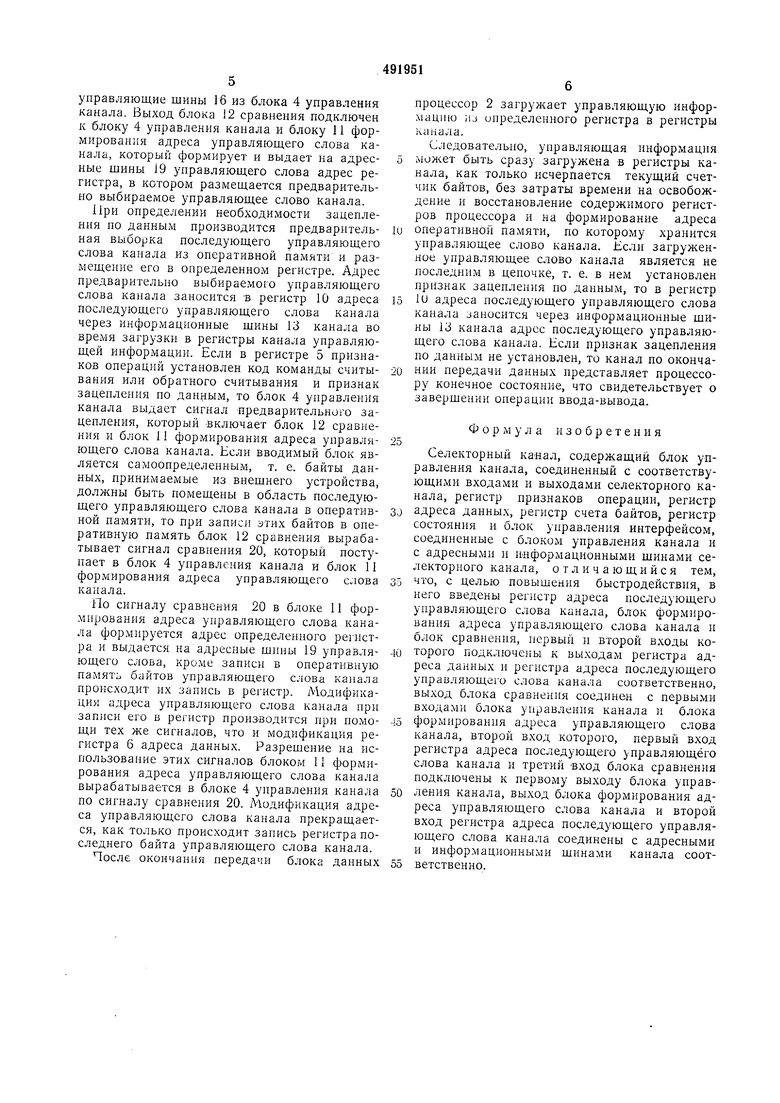

Структурная схема селекторного канала представлена на чертеже, где обозначено:

селекторный канал 1, процессор 2, внещнее устройство 3, блок 4 управления канала, регистр 5 признаков операций, регистр 6 адреса данных, регистр 7 счета байтов, регистр 8 состояния, блок 9 управления интерфейсом, регистр 10 адреса последующего управляющего слова канала, блок 11 формирования адреса управляющего слова канала, блок 12 сравнения, информационные шины 13 канала, выходные управляющие шины 14 канала, входные управляющие щины 15 канала, управляющие щины 16, адресные щины 17 оперативной памяти, щины интерфейса 18, адресные щины 19 управляющего слова, сигнал сравнения 20.

Селекторный канал 1 предназначен для подключения к процессору 2 высокоскоростных внешних устройств 3 и управления передачей данных между ними и процессором 2.

Селекторный канал работает следующим образом.

Операция передачи данных между процессором 2 и внешним устройством 3 выполняется под управлением управляюшего слова канала, расположенного в регистрах канала. Управляющие слова канала первоначально хранятся в оперативной памяти процессора 2 и содержат всю необходимую управляющую информацию для передачи блока данных, а именно: код выполняемой команды, начальный адрес блока в оперативной памяти, количество байтов данных, которые необходимо передать, и специальные признаки. Управляющие слова канала выбираются из оперативной памяти и загружаются в регистры канала через информационные шины 13 канала по специальной команде, при помощи которой процессор 2 запускает операцию ввода-вывода в селекторном канале 1, или по ходу выполнения операции ввода-вывода, когда заканчивается передача блока данных, указанного в ранее загруженном (текущем) управляющем слове канала, и в нем задан специальный.признак зацепления по данным.

Получив управляющую информацию, селекторный канал 1 продолжает выполнение операции передачи данных без вмешательства процессора 2, используя управляющую информацию в регистрах канала. В зависимости от кода операции, состояния регистра 7 счета байтов и блока 9 управления интерфейсом в блоке 4 управления канала формируются запросы на передачу данных, которые через выходные управляющие шины 14 капала поступают в процессор 2.

По каждому запросу на передачу данных работа процессора по выполнению текущей микропрограммы приостанавливается на цикл обмена данными между оперативной памятью и селекторным каналом 1. Процессор 2 вырабатывает специальную серию синхроимпульсов, которые через входные управляющие шины 15 канала поступают в блок 4 управления канала для формирования управляющих сигналов. В цикле передачи данных блок 4 управления канала формирует сигналы для управления нриемом и передачей данных, а также сигналы для модификации счетчика байтов и адреса данных, которые через управляющие шины 16 поступают в блок 9 управления интерфейсом, регистр 6 адреса данных и регистр 7 счета байтов. При этом адрес оперативной памяти, куда должны считываться или откуда должны записываться данные, иередается из регистра 6 адреса данных через адресные шины 17 оперативной памяти в процессор 2. Обмен данными между селекторным каналом 1 и внешним устройством 3 производится через шины интерфейса 18 и не зависит от режима работы процессора 2. Процесс передачи заканчивается, когда счетчик байтов текущего управляющего слова канала становится равным нулю.

По окончании передачи блока данных в

блоке 4 управления канала возбуждается запрос на обработку оконечного состояния или, как было отмечено выше, при наличии признака зацепления по данным - запрос на загрузку последующего управляющего слова

канала. В этом случае нроцессор 2 прерывает текущую обработку информации, формирует в своих регистрах, предварительно освободив их от текущей информации, адрес онеративной памяти, по которому содержится следующее управляющее слово капала, загружает его в регистры канала и затем восстанавливает содержимое регистров процессора.

Так как при выполнении зацепления по данным каналу 1 время от времени требуется занимать процессор 2 для получения последующего управляющего слова канала, то время выполнения операции ввода-вывода с использованием цепочки данных увеличивается, и, следовательно, снижается скорость передачи данных.

Уменьшить время выполнения цепочки данных можно за счет предварительной выборки последующего управляющего слова канала в снециальный регистр для того, чтобы после

окончания передачи блока данных сразу же загрузить его в регистры канала. В качестве специального регистра могут быть использованы или ячейка с фиксированным адресом в местной памяти процессора 2 или регистр, реализованный аппаратно. Но при выполнении операции ввода может оказаться, что вводимые под управлением текущего управляющего слова канала данные используются как последующее управляющее слово канала, т. е.

вводимый блок является сомоопределенным.

Это обстоятельство или вообще заставляет отказаться от предварительной выборки управляющего слова канала при операциях ввода-вывода с зацеплением по данным или

же вводить соответствующие ограничения на программирование ввода-вывода.

Рассматриваемый селекторный канал 1 позволяет выполнять предварительную выборку управляющего слова канала всегда,

если определена цепочка данных, т. е. без учета ограничений, связанных с самоопределенными блоками данных, и тем самым сделать скорость передачи данных независимой от использования цепочек. Это достигается за счет регистра 10 адреса последующего управляющего слова, блока И формирования адреса управляющего слова канала, блока 12 сравнения и использования определенного регистра для хранения предварительно выбранного управляющего слова канала.

Выходы регистра 6 адреса данных и выходы регистра 10 адреса последующего управляющего слова канала подключаются к блоку 12 сравнения -при наличии сигнала предварительного зацепления, поступающего через управляющие шины 16 из блока 4 управления канала. Выход блока 2 сравнения подключен к блоку 4 управления канала и блоку 11 формирования адреса управляющего слова канала, который формирует и выдает на адресные шины 19 управляющего слова адрес регистра, в котором размещается предварительно выбираемое управляющее слово канала. При определении необходимости зацепления по данным производится предварительная выборка последующего управляющего слова канала из оперативной памяти и размещение его в определенном регистре. Адрес предварительно выбираемого управляющего слова канала заносится в регистр 10 адреса последующего управляющего слова канала через информационные шины 13 канала во время загрузки в регистры канала управляющей информации. Если в регистре 5 признаков операций установлен код команды считывания или обратного считывания и признак зацепления по данным, то блок 4 унравления канала выдает сигнал предварительного зацепления, который включает блок 12 сравнения и блок 11 формирования адреса управляющего слова канала. Если вводимый блок является самоопределенным, т. е. байты данных, принимаемые из внещнего устройства, должны быть помещены в область последующего управляющего слова канала в оперативной памяти, то при записи этих байтов в оперативную память блок 12 сравнения вырабатывает сигнал сравнения 20, который поступает в блок 4 управления канала и блок 11 формирования адреса управляющего слова канала. По сигналу сравнения 20 в блоке 11 формирования адреса управляющего слова канала формируется адрес определенного регистра и выдается на адресные шины 19 управляющего слова, кроме записи в оперативную память байтов управляющего слова канала происходит их запись в регистр. Модификация адреса управляющего слова канала при записи его в регистр производится при по.мощи тех же сигналов, что и модификация регистра 6 адреса данных. Разрешение на использование этих сигналов блоком 11 формирования адреса управляющего слова канала вырабатывается в блоке 4 управления канала по сигналу сравнения 20. Л1одификация адреса управляющего слова канала прекращает ся, как только происходит запись регистра по следнего байта управляющего слова канала. После окончания передачи блока данных роцессор 2 загружает управляющую инфорацию из онределенного регистра в регистры анала. Следовательно, управляющая информация может быть сразу загружена в регистры канала, как только исчерпается текущий счетчик байтов, без затраты времени на освобожение и восстановление содержимого регистров процессора и на формирование адреса оперативной памяти, по которому хранится управляющее слово канала. Если загруженное управляющее слово канала является не последним в цепочке, т. е. в нем установлен признак зацепления по данным, то в регистр 1и адреса носледующего управляющего слова канала заносится через информационные шины 13 канала адрес последующего управляющего слова канала. Если признак зацепления по данным не установлен, то канал по окончании передачи данных представляет процессору конечное состояние, что свидетельствует о заверщении операции ввода-вывода. Формула изобретения Селекторный ка«ал, содержащий блок управления канала, соединенный с соответствующими входами и выходами селекторного канала, регистр признаков операции, регистр адреса данных, регистр счета байтов, регистр состояния и блок управления интерфейсом, соединенные с блоком управления канала и с адресными и информационными шинами селекторного канала, отличающийся тем, что, с целью повышения быстродействия, в него введены регистр адреса последующего управляющего слова канала, блок формирования адреса управляющего слова канала и блок сравнения, первый и второй входы которого подключены к выходам регистра адреса данных и регистра адреса последующего управляющего слова канала соответственно, выход блока сравнения соединен с первыми входами блока унравления канала и блока формирования адреса управляющего слова канала, второй вход которого, первый вход регистра адреса последующего управляющего слова канала и третий вход блока сравнения подключены к первому выходу блока управления канала, выход блока формирования адреса управляющего слова канала и второй вход регистра адреса последующего управляющего слова канала соединены с адресными и информационными шинами канала соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Селекторный канал | 1973 |

|

SU519703A1 |

| Устройство для управления диагностикой каналов | 1973 |

|

SU526876A1 |

| Устройство управления каналами | 1973 |

|

SU518769A1 |

| Селекторный канал | 1973 |

|

SU517019A1 |

| Устройство управления каналами | 1972 |

|

SU545983A1 |

| Селекторный канал | 1977 |

|

SU690472A1 |

| Мультиплексный канал | 1973 |

|

SU517022A1 |

| Селекторный канал | 1983 |

|

SU1103218A1 |

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с внешним устройством | 1984 |

|

SU1272337A1 |

| Устройство для сопряжения электронно-вычислительной машины с внешним устройством | 1986 |

|

SU1388880A2 |

Авторы

Даты

1975-11-15—Публикация

1973-07-18—Подача