(54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с блокировкой неисправных элементов памяти | 1976 |

|

SU641503A1 |

| Запоминающее устройство с самоконтролем | 1982 |

|

SU1037350A1 |

| Запоминающее устройство с самоконтролем | 1989 |

|

SU1718276A1 |

| Запоминающее устройство с самоконтролем | 1982 |

|

SU1065884A1 |

| Запоминающее устройство с блокировкой неисправных ячеек | 1974 |

|

SU492000A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU368647A1 |

| Запоминающее устройство с автономным контролем | 1984 |

|

SU1226534A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1249591A1 |

| Динамическое запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1133625A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1185400A1 |

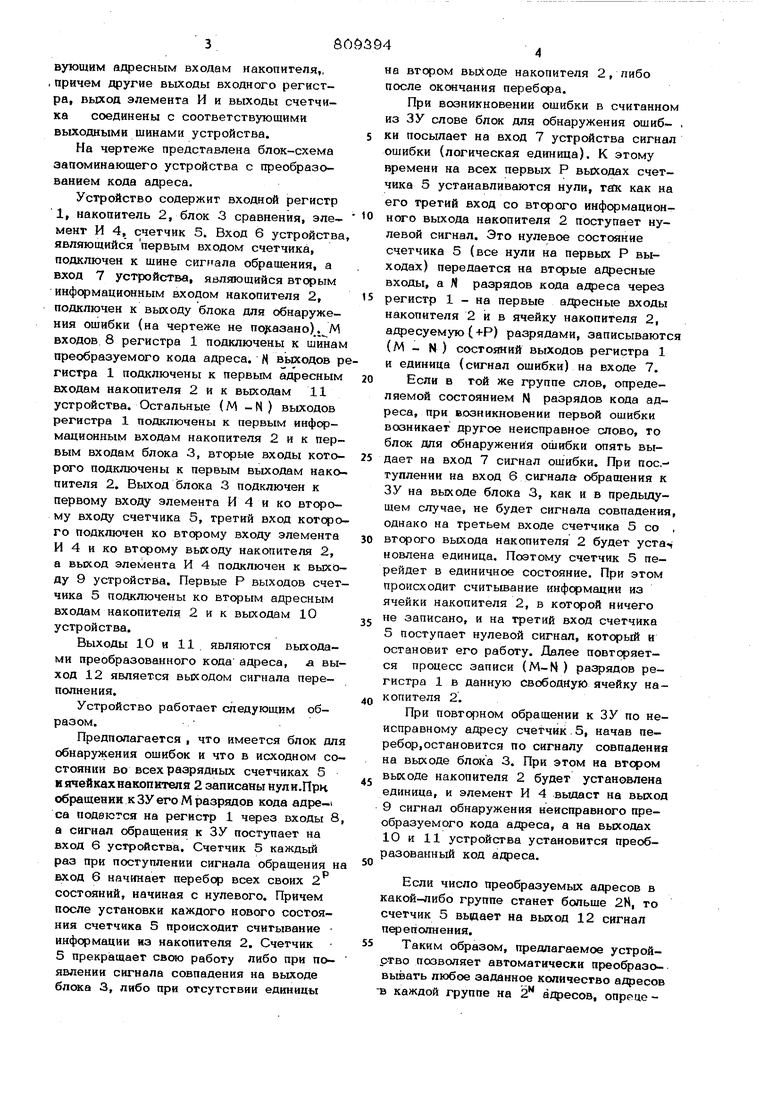

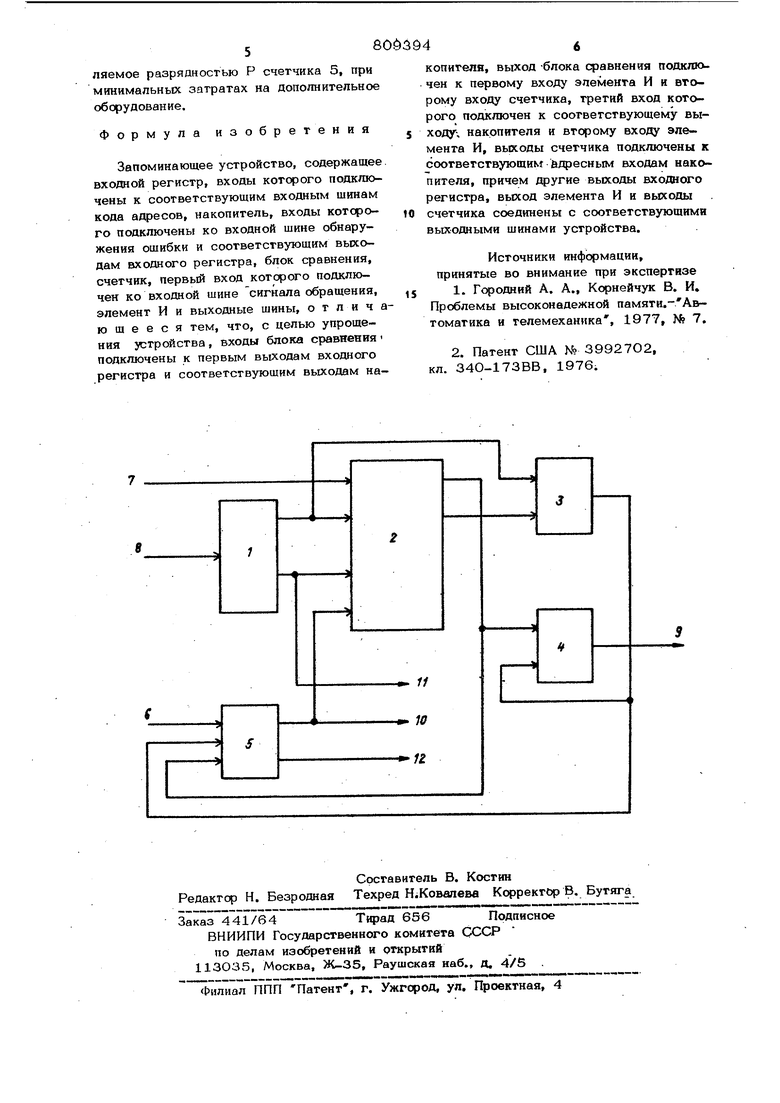

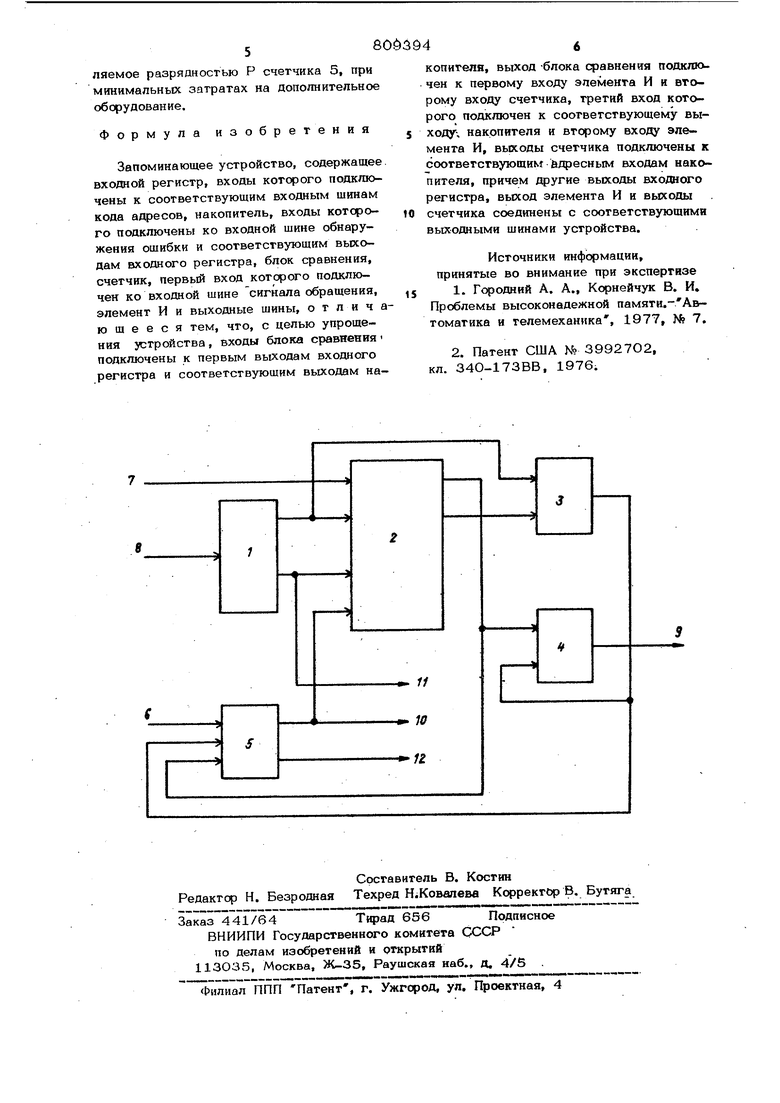

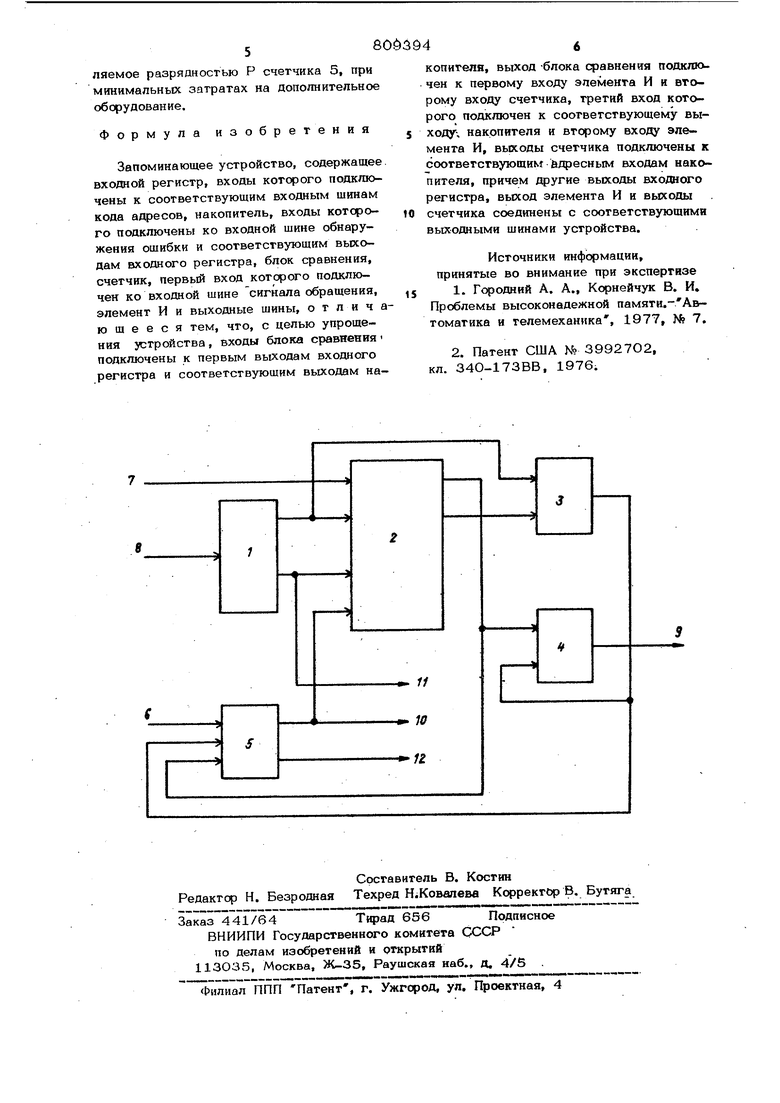

Изобретение относится к вычислительной технике и может использоваться в си стемах обработки информации. Для повышения надежности запоминающих устройств (ЗУ) применяют замену отказавших ячеек памяти резервными, ра сположеиными в дополнигельном ЗУ малой емкости t1. Известно ЗУ с преобразованием кодов af jecoB неисправных ячеек памяти, содержащее три накопителя, счетчик, М-разрядный входной регистр, N выходов которого соединены с адресными входами первого накопителя, а (М-К ) его выходов- с адресными входами второго накопителя. Выходы первого и второго накопителей соединены с ащ)есными входами третьего накопителя. На вход счетчика поступает сигнал ошибки, а его выходы подключены к информационным входам всех грех накопителей. Выходы третьего накопителя ЯВЛ5ПОТСЯ выходами устройства 2. , Однако это устройство является относительно сложным, что определяется налцчием трех накопителей, причем емкость последнего резко возрастает с увеличением числа преофазуемых адресов. Цель изобретения - упрощение устройства. Указанная цель достигается тем, что Б запоминающем устройстве, содержащем входной регистр, входы которого подключены к соответствующим входным шинам кода адресов, накопитель, входы KorqjcTQ. подключены к входной шине обнаружения ощибки и соответствующим выходам входного регистра, блок сравнения, счетчик, первый вход которого подключен к входной шине сигнала офащения, элемент И и входные шины, входы блсжа сфавнеквя подключены к первьдм выходам входного регистра и соответствующим выходам накопителя, выход блока сравнения подключен к первому входу элемента И и второму входу счетч5Гка, третий вход которсго подключен к соответствующему выходу накопителя и второму входу элемента И, выходы счетчика подключены к соответствующим адресным входам иакопигеля,, ,причем другие выходы входного регистра, выход элемента И и выходы счетчика соединены с соответствующими выходными шинами устройства. На чертеже представлена блок-схема запоминающего устройства с преобразованием кода адреса. Устройство содержит входной регистр 1, накопитель 2, блок 3 сравнения, элемент И 4, счетчик 5. Вход 6 устройства являющийся первым входом счетчика, подключен к щине обращения, а вход 7 устройства, являющийся втсрым инффмационным входом накопителя 2, подключен к выходу блока для обнаружения ошибки (на чертеже не по|сазано).М входов 8 регистра 1 подключены к шина преобразуемого кода адреса. N выходов р гистра 1 подключены к первым адресным входам накопителя 2 и к выходам 11 устройства. Остальные (М -N ) выходов регистра 1 подключены к первым информационным входам накопителя 2 и к пер вым входам блока 3, вторые входы кото рого подключены к первым выходам нако пителя 2. Выход блока 3 подключен к первому входу элемента И 4 и ко входу счетчика 5, третий вход котор го подключен ко второму входу элемента И 4 и ко второму выходу накопителя 2, а выход элемента И 4 подключен к выхо ду 9 устройства. Первые Р выходов сче чика 5 подключены ко вторым адресным входам накопителя 2 и к выходам 10 устройства. Выходы 10 и 11 . являются вькодами преобразованного кода адреса, а вы ход 12 является выходом сигнала переполнения. Устройство работает следующим образом. Предполагается , что имеется блок дл обнаружения ошибок и что в исходном с стоянии во всех разрядных счетчиках 5 и ячейках накопителя 2 записаны нули.Прк обращении к ЗУ его М разрядов кода адреса подаются на регистр 1 через входы а сигнал обращения к ЗУ поступает на вход 6 устройства. Счетчик 5 каждый раз при поступлении сигнала обращения вход 6 начинает перебор всех своих 2 состояний, начиная с нулевого. Причем после установки каждого нового состояния счетчика 5 происходит считывание информации из накопителя 2. Счетчик 5 прекращает свою работу либо при появлении сигнала совпадения на выходе блока 3, либо при отсутствии единицы а втором выходе накопителя 2, пибо осле окончания перебора. При возникновении ошибки в считанном з ЗУ слове блок для обнаружения ошиб- , и посылает на вход 7 устройства сигнал шибки (логическая единица). К этому ремени на всех первых Р выходах счетика 5 устанавливаются нули, так как на го третий вход со второго информационного выхода накопителя 2 поступает нулевой сигнал. Это нулевое состояние счетчика 5 (все нули на первых Р выходах) передается на вторые адресные входы, а N разрядов кода адреса через регистр 1 - на первые адресные входы накопителя 2 и в ячейку накопителя 2, а/чэесуемую ( +Р) разрядами, записываются (М - Ы ) состояний выходов регистра 1 и единица (сигнал ошибки) на входе 7. Если в той же группе слов, определяемой состоянием N разрядов кода адреса, при возникновении первой ошибки возникает другое неисправное слово, то блок для обнаружения ошибки опять выдает на вход 7 сигнал ошибки. При пос.туплении на вход 6 сигнала обращения к ЗУ на выходе блока 3, как и в предыдущем случае, не будет сигнала совпадения, однако на третьем входе счетчика 5 со , второго выхода накопителя 2 будет уста новлена единица. Поэтому счетчик 5 перейдет в единичное состояние. При этом происходит считывание информации из ячейки накопителя 2, в которой ничего не записано, и на третий вход счетчика 5 поступает нулевой сигнал, который и остановит его работу. Далее повторяется процесс записи (M-N ) разрядов регистра 1 в данную свободную ячейку накопителя 2. При повторном обращении к ЗУ по неисправному адресу счетчик. 5, начав перебор,остановится по сигналу совпадения на выходе блока 3. При этом на втором вькоде накопителя 2 будет установлена единица, и элемент И 4 выдаст на выход 9сигнал обнаружения неисправного преобразуемого кода адреса, а на выходах 10и 11 устройства установится преобразованньй код адреса. Если число преобразуемых адресов в какой-либо группе станет больше 2N, то счетчик 5 выдает на выход 12 сигнал переполнения. Таким образом, предлагаемое устройство позволяет автоматически преобразовывать любое заданное количество адресов -в каждой группе на 2 апресов, опррце ляемое разрядностью Р счетчика 5, при минимальных затратах на дополнительное оборудование.

Формула изобретения

Запоминающее устройство, содержащее входной регистр, входы которого подключены к соответствующим входным щинам кода адресов, накопитель, входы котсрого подключены ко входной шине обнаружения ошибки и соответствующим выходам входного регистра, блок сравнения, счетчик, первый вход которого подключен ко входной шине сигнала обращения, элемент И и выходные шины, отличающееся тем, что, с целью упрощения устройства, входы блока сравнения подключены к первым выходам входного регистра и соответствующим выходам накопителя, выход -блока сравнения подключен к первому входу элемента И и второму входу счетчика, третий вход которого подключен к соответствующему выходу; накопителя и второму входу элемента И, вькоды счетчика подключены к соответствующим адресным входам накопителя, причем другие выходы входного регистра, выход элемента И и вьссоды

счетчика соединены с соответствующими выходными шинами устройства.

Источники информации,

принятые во внимание при экспертизе

Проблемы высоконадежной памяти.-Автоматика и телемеханика , 1977, № 7,

If 10

Авторы

Даты

1981-02-28—Публикация

1978-08-23—Подача