(54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ КВАДРАТНОГО КОРНЯ ИЗ ЧАСТНОГО И ПРОИЗВЕДЕНИЯ ДВУХ АРГУМЕНТОВ

2-SfJ J

n

r + i при CO. .

tr4 r{- f -o

,0, U,,,Z,.,V2-Hf,.,..y,

Й7. ..2..,-Zi,i2-

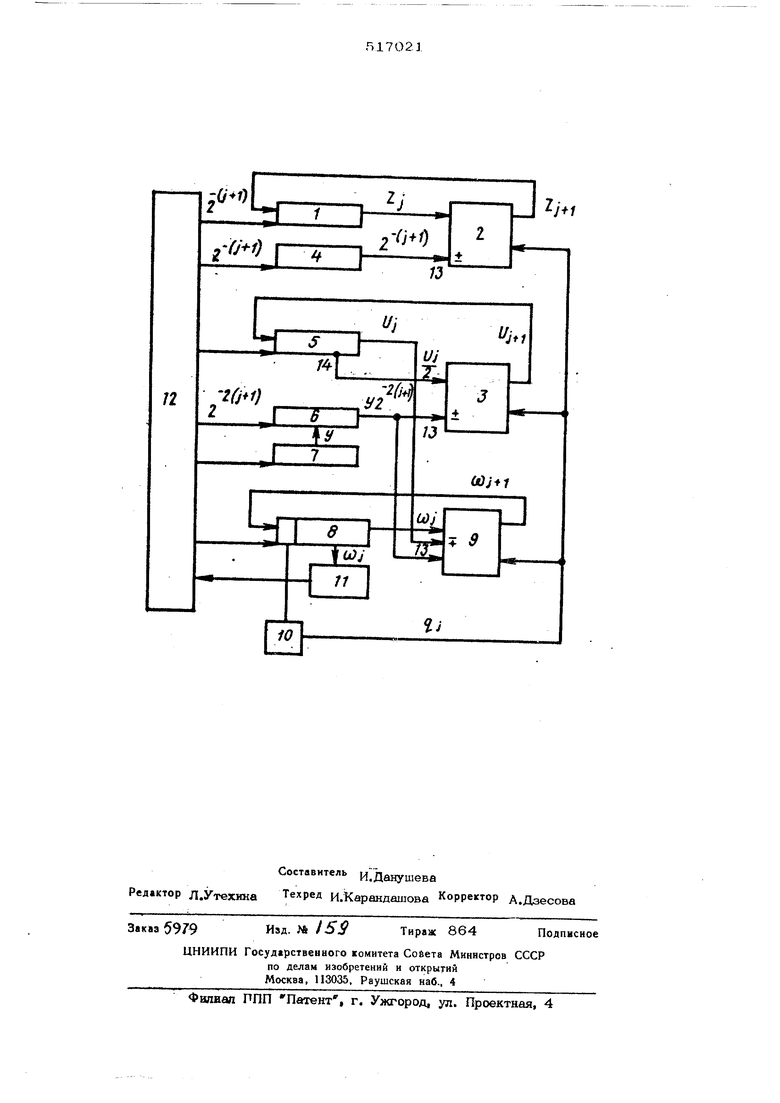

Bee указанные .вычисятитепьтше операдии огут быть реализованы в структ5фе, соержащей три накопительных сдвигающих егистра, три одноразрядных сумматора и 15 ад регистров сдвнпга,

На чертеже представлена блок схвма стройства I для получения квадратного орня из частного и произведения где-

обозначены накопительный сдвигающий ре- 20 истр 1 первого псевдоумножнтеля для значения квадратного корня из частного; одноразрадньте. сумматоры 2j 3 на два входа; одностороннюю намять 4, накопительный -регистр 5 . второго псёааоу1 1Нож1Н теля для значения квадратного корня из произведения; сдвигающий регистр 6, вход- ной регистр 7 аргумента V нак опитальный сдвигающий регистр 8 псевдоделителя; одноразрядный сумматор 9 на три входа элемент анализа знана. псёвдочас-тного 1О, элемент анализа сходимости очередного приближения аргумента Ни элемент управления 12.

Параллельно-последовательная .структура устройства обладает относительно БЫ сокой однородностью и состоит из стандарт. ных цифровых элементов одноразрядных сумматоров на два и на три входа, сдвигаю- ,40 ишх регистров, элементов совпадения, од-. носторонней памяти и,элементов управления. . Значение аргумента X (при5ем О 4 ) заносится в регистр 8, состоящий из { fl + Ш ) разрадов, где tfj . - число 45 раарадов аргумента, /м - число допол1аительных разрадов для компенсации погрешности.

Значение аргумента У (причем для данной записи алзЕ оритма 1 У ) за SO нооится во входной ft -разрядный ре гистр 7, содержимое которого сдвигается ( № fn )-разрадным регистром 6 л подает ся на управляющий вход 13 сумматора 3 и одновременно на третий вход сумматора S5

9.

Выход предпоследней ачейки накопительного регис1 ра 5 второго псевдо,ут 1нож1ггеля подан на основной вход од Юраарядного сумматора 3 выход которого подключен 60

ко вхоау накопительного регистра S. Вы , ход регистра S подключен к входу 13 однОразря.аног о сумматора 9.

К основному входу сумматора 9 поа ключен выход накопительного сдригаюшего регистра 8 пседдоделителя, квходу которого подключен выход суммато , ра 9 псевдоделителя. Знаковый разряд накопительного сдвигающего регистра 8 псевдоделителя соединен с элементом 1.О анализа знака псевдочастного. Выход элемента Ю анализа знака соединен g управляющими входами всех сумматоров. Выходы всех ячеек накопительного сдвигающего регистра 8 псевдоделителя сс единены с параллельными .входами элемента анализа сходимости 11, выход которого соединен с входом сброса элемента упра&э. лення 12. -:

Выход регистра 1 первого псевдоумножителя соединен с основным входом cjMматора 2, выход которого соединен с входо у{ регрютр.а первого псевдоумножителя,Ко входу 13 сумматора 2 подсоединен выход односторонней памяти, в. которой хранятся .константы вида. 2 J где J О, l;.,., й. .

Управление пропессом вычисления путем подачи соответствующих тактовых с.цЕига5о« ших импульсов, осуществляется элементом управления 12.

Параллельно-последовательная структура определяет параллельное вычисление приве -з денных pekyppeHTHbix соотношений алгорит дама, .кажаое из которых, вычисляется последовательно, в каждой .итерации .за (И + тактов. ®

Число итераций .для требуемой точности вычисления (1О-16 дв, разрядов) при решении задач управления на единицу больше числа разряцоЕ.

В первой итерации из содержимого накопительного сдвигающего регистра 8 псевдоделнтеля вычитается :, сдвинутое ,на 2 разрнаа вправо от .цвоичйРой запятой аначе. ния второго аргумента У. По знаку полученной разности определяется в элементе анализа знака псевдоделимого очередная ци ра : псев.аочастного в специальном элементе счисления (+ 1,, - 1). Если очере.а ное приближение значения аргумента больше самого аргумента X, то разность в регист-ре псевдоделения меньше нуля, и .. очередная (на следующей итерации) цифра псеацочастного равна -1. При этом а одк разрядных сумматорах 2 и 3 выполняется операция вычитания, а по управляющему вхо.а} трехвходойого сумматора 9 - спе,рация сложения. В начальном состоянии в регистрах 1 (первого) и .5 (второго) «псевдоумножит лей содержимое равно нулю. В первой ите рации в регистр 1 первого псеццоумножителя записывается с соответствующим зна ком значение первой константы (2 ), второго аргумента У, Процесс псевдоумно ,жения аналогичен умножению и необходим .цля преобразования очередной цифры цсевдочастного в двоичную систему счисления значений квадратного корня-на частного (регистр 1) и произведения (регистр 5). При значении очередного приближения аргумента меньше действительного X оче- редная цифра, псеацочастного 0 +1, к перемены операций в сумматорах не пре исходит. Процесс вычисления каждой итерации повторяется ( Jfi. - 1) раз. В конце процео са Еьтчясления в. регистрах 1 и 5 записаны значения згказан -1ых функций. Быстро.цействие .предлагаемого устройст с параллельно-последовательной .. структурой определяется в тактах соотношением ( Л. + /tj) И значительно больше, чем iAV;;; использовании известных .уст- . ройстз, Для подавляюшего большинства значений аргументов точное значение .вычисляемых функкий пол аатся при числа Итера- 1Ь--й :ленъше ( ft + 1). Для сокращения вре мел вычисления в- структуру зьеден элемент ащллэа сходимости 11, представляю щий собой лемент сревнения с нулем,,содержимого регистра 8 псевдоделителя, В случае когда все разряды регистра 8 ноеь-ноделителя незначащие, с выхода элемента анализа вьщается сигнал сброса пстаноЕй и) элемента управления на еледующей ьгерацки, чем достигается асинх- pCHKi ;й режим элемента управления. Напри мер при X 0,5 и У IjO для получения точного значения фуз-шции необходима -:Ч)ль-о .дкр итерация. Для четырех, значе- ; НИИ аргументов необхо.цимы две итерации и т. .ц, I Значение ква,цратного корня из произве- |дения в накопительном регистре 5 псевдоI умножителя в конце процесса сдвинуто I вправо на ( tt + 1) разрядов, поэтому двоичная запятая при чтении также переI носится вправо на (Н + 1) разрядов I структурным путем. Формула Ичзобретёниа i Устройство для вычисления ква.арат;ного корня из частного и произведения двух аргументов, содержащее накопительные : I сдвигающие регистры и регистр памяти, управляющие входы которых соединены с 1 соответствующими выходами блока управj ления, одноразрядные комбинационные , I сумматоры, управляющие входыкоторых соединены с выхо.цом элемента анализа I знака; вход элемента анализа знака нек с вы1одом знакового разряс1а накопи-, тельного сдвигающего $1егистра псевдоделителя, отличающееся тем,, i что,, с целью повыщения бьютродействия, I оно дополнительно содержит элемент ана-, ; лиза сходимости, накопительные сдвигаю|щие регистры и одноразрядный комбинационi ный сумматор; причем, управляющий вход одноразрядного комбинационного сумматора второго пседцоумножителя сое.цинен с выходом накопительного сдвигающего регистрй . второго аргумента, а основной вхо.ц этого I сумматора с выходом , предпоследнего I разряда накопительного сдвигающего регистipa второго псевдоумножителя, выход котоIporo соединен с управляющим входом одно-, разрядного комбинационного сумматора I псеццоделителя; третий вхо.д этого сумматоj pa соединен с выходом накопительного сдвиj тающего регистра второго аргумента; вы- ;хоцы всех разрядов накопительного сдвига- ющего регистра псев.аоделителя г-ое,аикень1 со входами элемента анализа сходимости, 1ВЫХОД которого с.оединен со входом. сбрагя {блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления кубического корня | 1973 |

|

SU516037A1 |

| Устройство для вычисления гиперболического тангенса | 1973 |

|

SU526890A1 |

| Устройство для вычисления тригонометрического тангенса | 1973 |

|

SU537344A1 |

| Устройство для вычисления логарифмической функции | 1973 |

|

SU541167A1 |

| Двоичное устройство деления | 1975 |

|

SU541171A2 |

| Арифметическое устройство | 1979 |

|

SU773619A1 |

| Устройство для вычисления элементарных функций | 1981 |

|

SU1032455A1 |

| Устройство для вычисления экспоненциальной функции | 1973 |

|

SU538366A1 |

| Устройство для вычисления корня четвертой степени | 1975 |

|

SU561184A1 |

| Устройство для вычисления элементарных функций | 1975 |

|

SU553612A1 |

Авторы

Даты

1976-06-05—Публикация

1973-06-29—Подача