1

Изобретение отиосится к области вычислительной техни1ки и может быть исиользовано для аппаратной реализации подпрограммы вычисления элементарных функпий в специализированных цифровых вычислительных машинах с фиксированной запятой.

Известно устройство для вычисления корня, содержащее накопительные сдвигающие регистры, регистр памяти, блок управления, одноразрядные комбинационные сум(маторы и элемент анализа сходимости.

Недостатком известного устройства является сравнительно низ«ое быстродействие.

Цель изобретения - повышение быстродействия устройства.

Это достигается тем, что предлагаемое устройство дополнительно содержит одноразрядные сумматоры и блок формирования коистаит, первый выход которого соединен с входом одноразрядного комбинационного сумматора псевдоумножителя, второй выход блока формирования констант соединен через два одноразрядных сумматора с уп|равляемым входом одноразрядного сумматора псевдоделителя, выходы предпоследнего и последнего разрядов накопительного сдвигающего регистра первого псевдоу множителя соединены с входами соответствующих одноразрядных суММаторов.

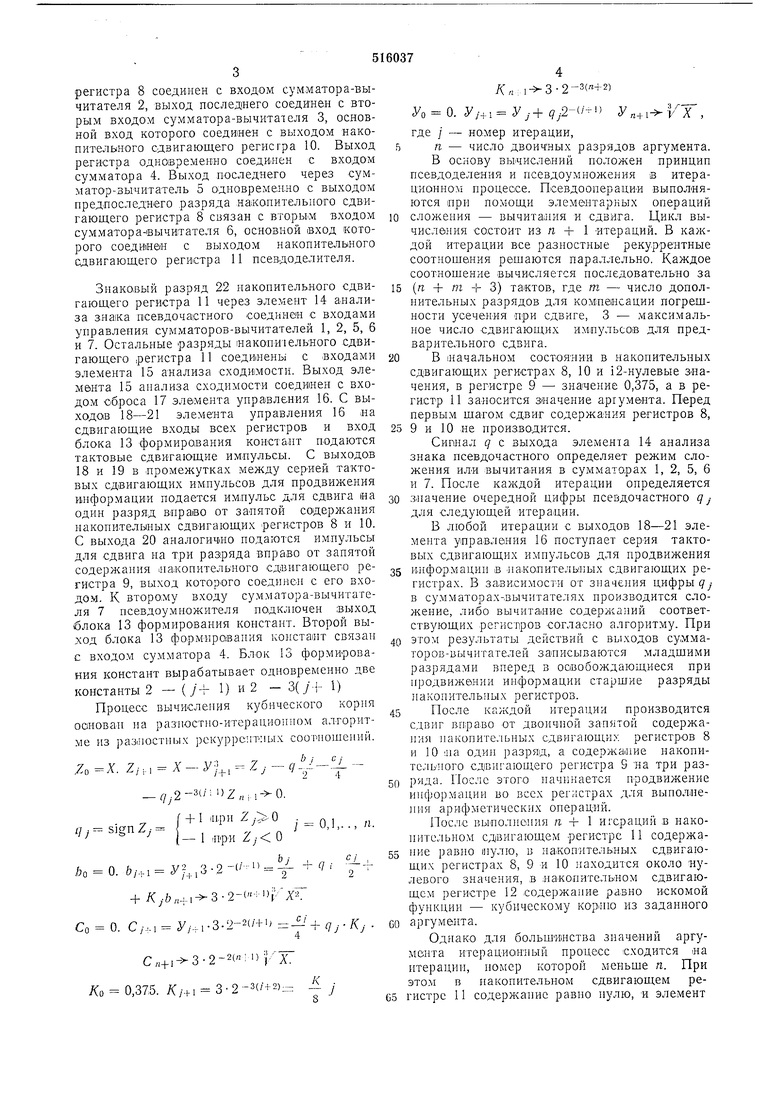

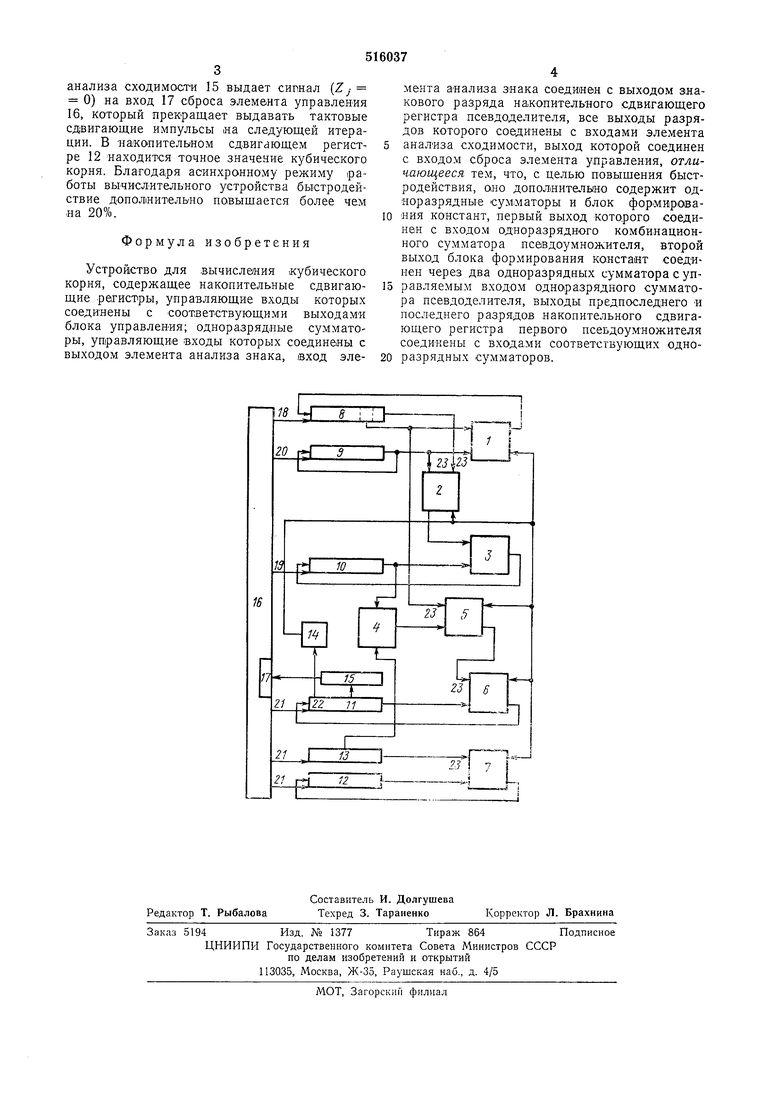

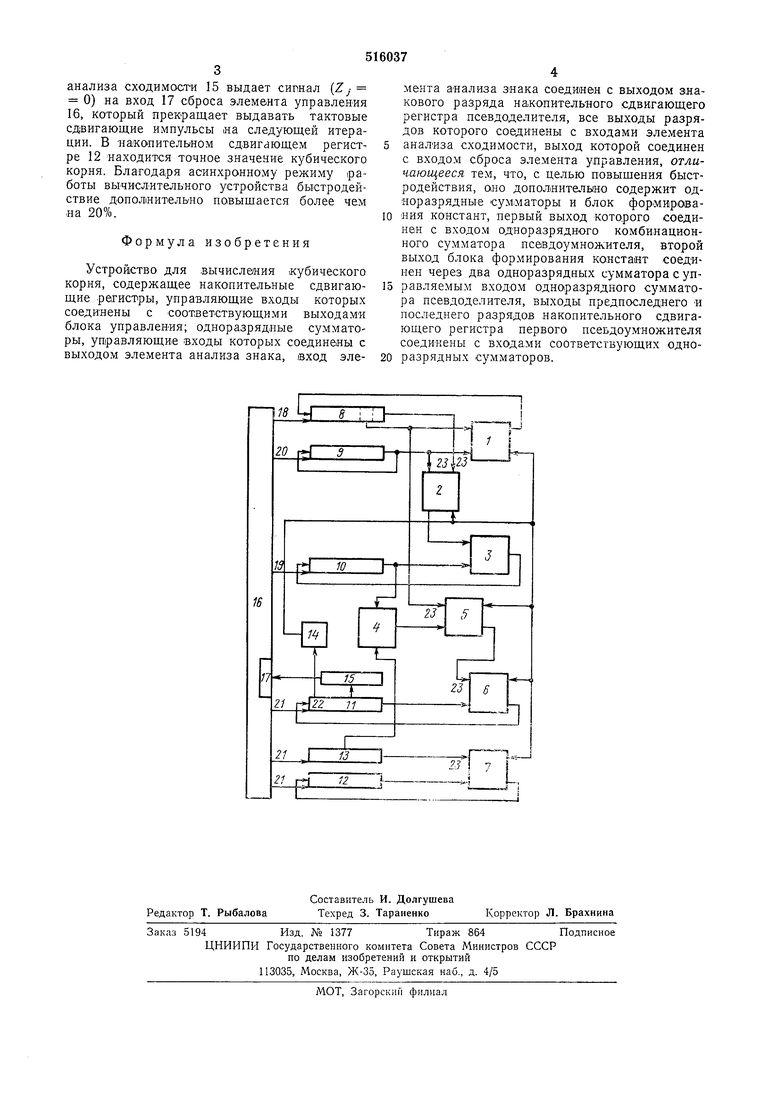

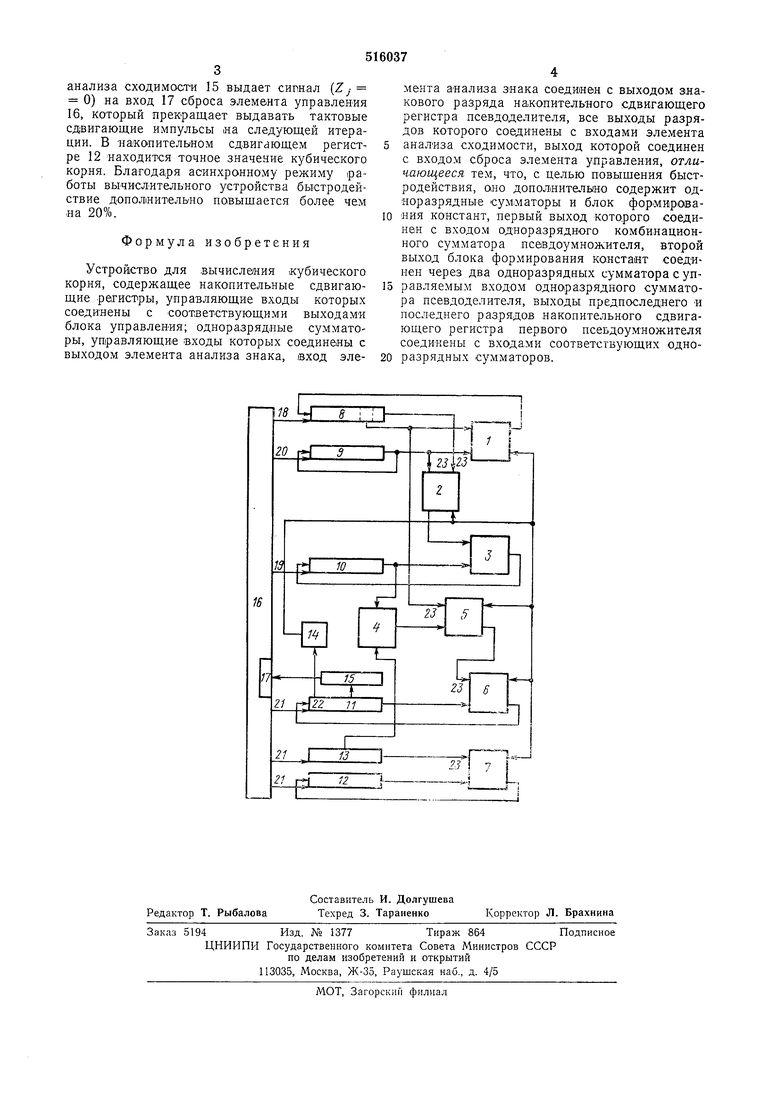

На чертеже иоказаата блок-схема устройства для вычисления кубического корня, где 1-7 - одноразрядные сумматоры-вычитатели; 8-12 - накопительные сдвигающие регистры; 13 - блок формирования констант;

14- элемент анализа знака псевдочастного;

15- элемент аиалнза сходимости; 16 - элемент управления; 17 -вход сброса элемента управления; 18, 19 - выходы тактовых сдвигающих импульсов для продвижения информации и первоначального сдвига на одни разряд; 20 - выход тактовых сдвигающих импульсов для продвижения информации и первоначального сдвига на три разряда; 21 - выход та.ктовых сдвигающих импульсов для продвижения информации; 22 - знаковый разряд псевдочастного; 23 - управляемый вход сумматора-йычнтателя.

Иараллельно-последовател1м1ая структура устройства, обеспечивающая оптимальное соотношение между быстродействием и СЛОЖиостью, состоит из четырех рециркуляционных ячеек. Каждая ячейка состоит из накопительного сдвигающего регистра и одноразрядного сумматора-вычитателя, вход и выход :которого соединены с выходом и входом накопительного регистра.

Вход сумматора-вычитателя 1 соединен с выходол предпоследнего разряда накопительного сдвигающего регистра 8. Выход последпего разряда накопительного сдвигающего

регистра 8 соединен с входом сумматора-вычитателя 2, выход последиего соединен с вторым входом сумматора-вычитателя 3, основной вход которого соединен с выходом накопительного сдвигающего регистра 10. Выход регистра одновременно соединен с входом сумматора 4. Выход последнего через сумматор-Бычитатель 5 одновременно с выходом предпоследнего разряда накопительного сдвигающего регистра 8 связан с вторым входом сумматора-вычитателя 6, основной вход которого соединен с выходом накопительного сдвигающего регистра 11 псевдоделителя.

Знаковый разряд 22 накопительного сдвигающего регистра 11 через элемент 14 анализа з,на1ка псевдочастного соединен с входами управления сумматоров-вычитателей 1, 2, 5, 6 и 7. Остальные разряды 1нако:пи1ельного сдвигающего регистра 11 соединены с входами элемента 15 анализа сходимости. Выход элемента 15 анализа сходимости соединен с входом сброса 17 элемента управления 16. С выходов 18-21 элемента управления 16 на сдвигающие входы всех регистров и вход блока 13 формирования консталт подаются тактовые сдвигающие импульсы. С выходов 18 и 19 в промежутках между серИей тактовых сдвигающих имнульсов для продвижения информации подается имлульс для сдвига на один разряд вправо от запятой содержания накопителыных сдв-игающих регистров 8 и 10. С выхода 20 аналогично подаются импульсы для сдвига на три разряда вправо от запятой содержания накопительного сдвигающего регистра 9, выход которого соединен с его входом. К второму входу сумматора-вычитателя 7 псевдоумножителя подключен выход блока 13 формирования констант. Второй выход блока 13 формирования констант связан с входом сумматора 4. Блок 13 формирования констант вырабатывает одновременно две константы 2 - (у+ 1) и 2 - 3(у f 1)

Процесс вычисления кубического корня основан на разностно-итерационном алгоритме из разоюстных рокуррситпых соорнощений.

,Zo х. z/и - -7-.j /- - r/,.2-3(,,.

+ 1 1при Zy о

signZy - 1 1при 2:у О

.0 -(/тП

.Ьо 0. &/.и У,1иЗ

+ ,(

Со 0. Су.-, У,чгЗ-2-2(/+и dj-Kj .

Ся+,3-2-2(«:)гТ Хо 0,375. (;.,, 32-з().:. 7

Д„: (Я+2)

Уо 0. У/+1 У у + (у2-(/-) У „+1 -КГ , где / - номер итерации,

5 п - число двоичных разрядов аргумента. В основу вычислений положен иринцип псевдоделения и псевдоумножения в итерационном процессе. Псевдооперации выполняются при помощи элементарных операций 10 сложения - вычитания и сдвига. Цикл вычисления состоит из п + 1 Итераций. В каждой итерации все разностные рекуррентные СООТНОЩ6НИЯ рещаются параллельно. Каждое соотношение вычисляется последовательно за 15 (п + т -г 3) тактов, где т - число дополнительных разрядов для компенсации погрешности усечения при сдвиге, 3 - максимальное число сдвигающих импульсов для предварительного сдвига.

20 В начальном состоянии в накопите«пьных сдвигающих регистрах 8, 10 и 12-нулевые значения, в регистре 9 - значение 0,375, а в регистр И заносится значение аргумента. Перед первым шагом сдвиг содержания регистров 8, 25 9 и 10 не производится.

Сигнал q с выхода элемента 14 анализа знака псевдочастного определяет режим сложения ИЛИ вычитания в сумматорах 1, 2, 5, 6 и 7. После каждой итерации определяется 30 значение очередной цифры псевдочасгного qj для следующей итерапии.

В любой итерации с выходов 18-21 элемента управления 16 поступает серия тактовых сдвигающих импульсов для продвижения 35 информации в накопительных сдвигающих регистрах. В зависимости от значения цифры qj в сумматорах-вычитателях нроизводится сложение, либо вычитание содержаний соответствующих регистров согласно алгоритму. При 40 этом результаты действий с выходов су.мматоров-Бычитателей занрюываются младщими разрядами вперед в освобождающиеся при продвижении информации старшие разряды накопительных регистров.

45 После каждой итерации производится сдвиг вправо от двоичной запятой содержа1 ия naiconnTe.ibHbix сдвигающих регистров 8 и 10 на один разряд, а содержание накопительного сд1внгаюн,его регистра 9 на три разряда. После этого начинается продвижение информации во всех рег гстрах для выполне)1ия арифметических операций.

После выполнения п + 1 итераций в накопительном сдвигающем регистре 11 содержа5 ние равно нулю, в накопительных сдвигающих регистрах 8, 9 и 10 находится около нулевого значения, в накопительном сдвигающем регистре 12 содержание равно искомой функции - кубическому корню из заданного O аргумента.

Однако для большинства значений аргумента итерацио1нный процесс сходится на итерации, номер которой меньше п. При этом в накопительном сдвигающем регистре 11 содержание равно нулю, и элемент

анализа сходимости 15 выдает силнал (Z j 0) на вход 17 сброса элемента управления 16, который прекращает выдавать тактовые сдвигающие импульсы «а следующей итерации. В Накопительном сдвигающем регистре 12 находится точное значение кубического корня. Благодаря асинхронному режиму работы вычисл-ительного устройства быстродействие дополнительно повыщается более чем на 20%.

Формула изобретения

Устройство для вычисления кубического корня, содержащее накопительные сдвигающие регистры, управляющие входы которых соединены с соответствующими выходами блока управления; одноразрядные сумматоры, управляющие входы которых соединены с выходом элемента анализа знака, вход элемента анализа знака соединен с выходом злакового разряда накопительного сдвигающего регистра псевдоделителя, все выходы разрядов которого соединены с входами элемента

анализа сходимости, выход которой соединен с входом сброса элемента управления, отличающееся тем, что, с целью повыщения быстродействия, оно дополнительно содержит одноразрядные cyMiMaTopH и блок фор|Мирования констант, первый выход которого соединен с входом одноразрядного комбинационного сумматора пс&вдоумножителя, второй выход блока формирования констант соединен через два одноразрядных сумматора с управляемым входом одноразрядного сумматора псевдоделителя, выходы предпоследнего « последнего разрядов накопительного сдвигающего регистра первого псеьдоумножнтеля соединены с входа ми соответствующих одноразрядных сумматоров.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления квадратного корня из частного и произведения двух аргументов | 1973 |

|

SU517021A1 |

| Устройство для вычисления гиперболического тангенса | 1973 |

|

SU526890A1 |

| Устройство для вычисления тригонометрического тангенса | 1973 |

|

SU537344A1 |

| Устройство для вычисления логарифмической функции | 1973 |

|

SU541167A1 |

| Устройство для вычисления гиперболических синуса и косинуса | 1973 |

|

SU536490A1 |

| Устройство для вычисления экспоненциальной функции | 1973 |

|

SU538366A1 |

| Двоичное устройство деления | 1975 |

|

SU541171A2 |

| Двоичное устройство деления | 1974 |

|

SU497585A1 |

| Устройство для вычисления обратного гиперболического тангенса | 1973 |

|

SU465630A1 |

| Устройство для вычисления экспоненциальной функции | 1977 |

|

SU711578A2 |

Авторы

Даты

1976-05-30—Публикация

1973-11-16—Подача