1

Изобретение относится к вычислительной технике и может использоваться нри конструировании вычислительных машин и систем.

Известно устройство преобразования временных интервалов в двоичный код для процессора сбора, обработки и передачи многоканального потока информации, еодержащее регистр адреса массива двоичных кодов, регистр адреса обработки, регистр конечного адреса обработки, схе.му сравнения, буфериый регистр, счетчик и дешифратор, нричем входы регистра адреса обработки, регистра адреса массива двоичных .кодов и регистра конечного адреса обработки соединены с шиной чтения и шиной нмнульсов записи процессора, а выход регистра адреса обработки соединен с первым входом схемы сравнения и входом нроцессора, выход регистра адреса массива двоичных кодов подключен к процессору, выход регистра конечного адреса обработки соединен с вторым входом схемы сравнения, выход которой соединен с входом процессора, первый вход буферного |регистра нодключен к шине импульсов записи, а его выход соединен с входом процессора, шина импульсов записи через счетчик и дешифратор соединеиа е входом процессора.

Недостатками известного устройства являются невысокая помехсзаш,ищенность и невысокая достоверность регистрируемой информации.

Цель изобретения - увеличеиие помехозащищенности и повышение достоверности принимаемой ииформации.

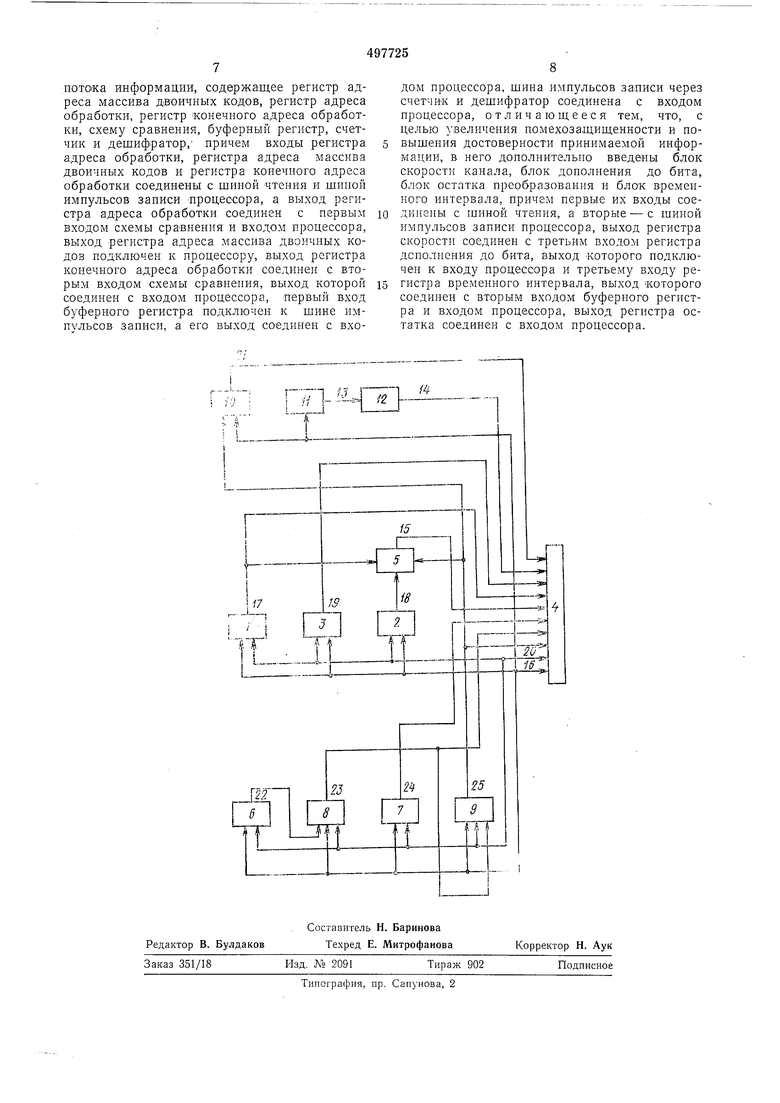

Для этого в устройство дополнительно введены блок скоростн капала, блок допол)1ення до бита, блок остатка преобразования и блок временного интервала, причем первые их входы соединены с шиной чтения, а вторые - с шиной импульсов запнсн нроцессора, выход регистра скорости соединен с третьим входом регистра донолнения до бита, выход которого подключен к входу процессора и к третьему

входу регистра временного интервала, выход которого соединен с вторым входом буферного регистра и входом процессора, выход регистра остатка соединен с входом процессора. На чертеже нзображена структурная схема

устройства нреобразования временных интервалов в двоичный код.

Устройство состоит из регистра 1 адреса обработки, осуществляющего храненне очередного адреса массива .временных меток канала,

регистра 2 конечного адреса обработки, в котором хранится конечный адрес массива временных .меток канала, преобразуемого в двоичный код, регистра 3 адреса массива двоичных кодов, фиксирующего адреса, по которым

3 процессор 4 осуществляется запись двоичных кодов, полученных в процессе преобразования массива временных меток, схемы 5 срйвнения, которая реализует функции сравнения на равенство, записан-ных в регистре 1 адреса обработки и регистре 2 конечного адреса обработки, блока 6 скорости канала, осуществляющего хранение кода длительности бита, определяющего скорость передачи данного канала, блока 7 остатка преобразования, в котором хранится значение («О или «1) и код остатка предыдущего бита, блока 8 дополнения до -бита, осуществляющего в процессе преобразования хранение кода дополнения до бита, блока 9 временного интервала, в котором хранится состояние временного интервала («О или «1), код длительности временного интервала и зпачепие бита («О или «1), полученного в процессе преобразования временных интервалов в двоичный код, буферного регистра 10, в котором до занесения в процессор 4 накапливаются двоичные коды, полученные в результате преобразования iBpeменных меток, счетчика 11, подсчитывающего число битов, записываемых в буферный регистр 10, дещифратора 12, фиксирующего момент заполнения буферного регистра 0 в процессе преобразования, кодовых шин 13, связывающих счетчик И с дешифратором 12, шины 14 выходной дещифратора 12, соединяющей его с Процессором 4, щ1-шы 15 выходной схомы 5 сравнения, соединяющей ее с процессором 4, щины 16 импульсов записи процессора 4, соединяющей его с регистром 1 адреса обработки регистром 2 конечного адреса обработки, регистром 3 массива двоичных кодов, блоком 6 скорости канала, блоком 7 остатка преобразования, блоком 8 дополнения до бита, блоком 9 временного интервала, буферным регистром 10 и счетчиком 11, адресных щин 17, связывающих регистр 1 адреса обработки с входом процессора 4 и первым входом схемы 5 сравнения, выходных кодовых щин 18, связывающих выход регистра 2 конечного адреса обработки с вторым входом схемы 5 сравнения, адресных щин 19, которые связывают регистр 3 адреса массива двоичных кодов с входом процессора 4, кодовых щин 20 чтения, по которым из процессора 4 осуществляется запись информации в регистр 1 адреса обработки, регистр 2 конечного адреса обработки, регистр 3 массива двоичных кодов, блок 6 скорости канала, блок 7 остатка преобразования, блок 8 дополнения до бита и блок 9 временного интервала, кодовых щин 21, по которым двоичные коды, полученные в результате преобразования и хранящиеся в буферном регистре 10, записываются в процессор 4, выходных кодовых щин 22, которые соединяют выход блока 6 скорости с входом блока 8 дополнения до бита, выходных кодозых щин 23, связывающих блок 8 дополнения до бита с входами блока 9 временного интервала и процессора 4, выходных кодовых щин 24, соединяющих блок 7 остатка преобразования с входом процессора 4, выходных кодовых щин 25, которые соединяют выход блока 9 временного интервала с входами процессора 4 и буферного регистра 10. Устройство работает следующим образом. В процессоре 4 формируется массив временных меток, отображающий изменения состояний данного канала во времени. Массив представляет собой совокупность записей состояния канала в сопровождении кода текущего времени. Устройство управления процессора 4 последовательно по щинам 16 импульсов записи вырабатывает сигналы, по которым по кодовым щинам 20 чтения переписывается информация, задающая режим работы, из процессора 4 в устройство. Затем в процессор 4 по адресным щинам 17 переписывается из регистра 1 адреса обработки код адреса, по которому устройство управления процессора 4 осуществляет чтение начальной ячейки массива временных меток, при этом в процессоре 4 получаем код первого момента изменения состояния канала (i) и состояние канала («О или «1). По сигналу устройства управления процессора 4, который поступает по щинам 16 импульсов записи, в блок 9 временного интервала из процессора 4 по кодовым шинам 20 чтения переписывается состояние канала, после чего на регистр 1 адреса обработки поступает сигнал из процессора 4

5 и формирует в нем код адреса следующей ячейки массива временных меток. Код нового адреса, по которому устройство управления процессора 4 осуществляет чтение следующей ячейки массива временных меток, поступает

5 по адресным щинам 17 в процессор 4 и в ием получаем код времени второго момента изме нения состояния канала (tz) и состояние канала в этот момент. В процессоре 4 осуществляется вычисление кода длительности временного интервала, представляющего собой разность значений кодов моментов времени k и /1. Полученный результат по сигналу устройства управления процессора 4, поступающему по шинам 16 импульсов записи, переписывается в блок 9 временного интервала. После этого в процессор 4 по выходным кодовым щинам 23 осуществляется перезапись кода дополнения до бита из блока 8 дополнения до бита и производится сравнение величин

0 кодов длительности полученного временного интервала и дополнения до бита. Если при этом величина длительности временного интервала больще или равна величине дополнения до бита, то дальнейщая устройства осуществляется следующим образом.

В процессоре 4 производится вычисление разности значений временного интервала и дополнения до бита, полученное значение разности по сигналу устройства управления процессора 4, поступающему по щинам 16 записывается в блок 9 временного интервала, после чего в процессор 4 по выходным кодовым шинам 24 и 25 соответственно заносится код остатка из блока 7 остатка преобразования и код дополнения до бита из блока 8 дополнения до бита. В процессоре 4 производится сравнение величины остатка и дополнения до бита. Если величина дополнения до бита меньше величины остатка, то устройство уиравления процессора 4 вырабатывает сигнал, поступающий по шинам 16 импульсов записи, по которому в блоке 9 вре:ленного интервала формируется значение бита, после чего устройство управления процессора 4 вырабатывает сигналы, один нз которых устанавливает в «ноль блок 7 остатка преобразования, другой сигнал по шипе 16 импульсов записи поступает на блок 8 дополнения до бита и осуществляет по выходным кодовым щинам 22 перепись в последний кода длительности б):та из блскс о скорости, третий сигнал по шинам 16 осуществляет запись в первый разряд буферного регистра 10 нз блока 9 временного интервала хранящегося в нем бита, полученного в результате преобразования временного интервала. Затем устройство управления процессора 4 вырабатывает сигнал, который осуществляет сдвнг на одни разряд в буферном регистре 10 и увеличивает на еднницу содержимое счет-ика 11. После этого снова осуществляется сравненне величин временного интервала и дополнения до бита. В случае, если величина временного интервала больше величины дополнения до бита, устройство осуществляет работу аналогично описанному до тех пор, пока величина дополнения до бита не станет больше величины длительности временного интервала. Если при сравнении в процессоре 4 гелн;Ин .дополнения до бита и остатка преобразования, величина дополнення до бита оказывается больше величины остатка, то устройство управления процессора 4 вырабатывает по шинам 16 и лпульсов записи сигнал, который осуществляет перепись состояния остатка из блока 7 остатка преобразования в блок 9 временного интервала, после чего работа устройства продолжается как и в предыдушем случае. Если при сравнении кодов длительности временного интервала и кода дополнения до бита величина длительности будет меньше величины дополнения до бита, то в процессор 4 по выходным кодовым шинам 24 из блока 7остатка преобразования переписывается код остатка и производится перепись состояНИИ остатка из блока 7 остатка преобразования и временного интервала из блока 9 временного интервала. Еслн состояния остатка и временного интервала coiвпaдaют, в процессоре 4 происходит сложение величин остатка и длительности временного интервала. Результат сложения по сигналу устройства управления процессора 4, вырабатываемому по шинам 16 импульсов записи, переписывается в блок 7 остатка преобразования. После этого в процессор 4 по кодовым шинам 23 из блока 8дополнения до бита переписывается код дополнения до бита и производится вычисление разности значений дополнения до бита и временного интервала. Полученный результат переписывается в блок 8 дополнения до бита. Если состояние остатка и временного интервала не совпадают и при этом величина остатка больше или равна длительиостн временного интервала, то в процессоре 4 происходит вычитание длительности временного интервала из величины остатка, а в дальнейшем работа устройства происходит как и в предыдущем случае. Пели состояния остатки и временного интервала не совпадают и HJIH этом величина остатка мепьше величины длительности временного интервала, то из величины длительности временного интервала вычитается величина остатка. Дальнейшая работа устройства происходит как и в предыдущих случаях за исклю гением того, что в .момент пе зепнси из процессора 4 в блок 7 остатка 1:з блока 9 времен1 ого интервала в этот же блок переписывается состояние временного интервала. Следующий цикл работы устройства происходит аналогично описанному. Двоичные разряды, полу1енные в результате последоватгльиых преобразований временных интервалов, накапливаются в буферном регистре, одпспремеиио с:етчик II осуществляет подсчет количества битов, поступающих в буферный регистр 10 и в момент, когда количество принятых в буферный регистр 10 битов будет «равно коли еству разрядов ячеек процессора 4, дешифратор 12 по шине 27 выхо;игой дсш ;фратора вырабатывает сигнал в устройство управления процессора 4, по которому в конце очередного цикла работы согласно кода адреса, записанного в регистре 3 адреса массива двоичных разрядов, в массив двоичных разрядов процессора 4 из бу(рерного регистра 10 переписываются коды, полученные в процессе преобразования. Далее устройство управления процессора 4 вырабатывает сигнал, yвeли ивaющий содержимое регистра 3 адреса массива двоичных кодов на единицу, после чего начинается очередной цикл преобразования. Процесс преобразования продолжается до тех пор покл схема 5 сравнения не зафиксирует равенство кодов, за писанных в регистре 1 адреса обработки и регнстре 2 конечного адреса обработки. В этом случае схема 5 сравпення по щпне 15 выходной схемы сравнения посылает в устройство управления нроцессора 4 слгиал, по которому в конце очередного цикла работы устройства преобразования временнь;х интервалов в двоичные коды устройство управления процессора 4 по кодовым шипам 23 и 24 осуществляет запись в процессор 4 кодов дополнения до бита из блока 8 дополнения до бита, кода и еостояния остатка нз блока 7 остатка преобразования, которые исполь30Baiibi при последующих преобразованиях массива временных метек данного канала. Предмет изобретения Устройство преобразования временных интервалов в двоичный код для процессора сбора, обработки и передачи многоканального

потока информации, содержащее регистр адреса массива двоичных кодов, регистр адреса обработки, регистр конечного адреса обработки, схему сравнения, буферный регистр, счетчик и дешифратор,- причем входы регистра адреса обработки, регистра адреса массива двоичных кодов и регистра конечного адреса обработки соединены с шпной чтения и шиной импульсов записи Процессора, а выход регистра адреса обработки соединен с первым входом схемы сравнения и входом процессора, выход регистра адреса массива двоичных кодов подключен к процессору, выход регистра конечного адреса обработки соединен с вторым входом схемы сравнения, выход которой соединен с входом процессора, первый вход буферного регистра подключен к шине ИМПУЛЬСОВ записи, а его выход соединен с входом процессора, шина импульсов записи через счетчик и дешифратор соединена с входом процессора, отличающееся тем, что, с целью увеличения помехозащищенности и повышения достоверности принимаемой информации, в него дополнительно введены блок скорости канала, блок дополнения до бита, блок остатка преобразования и блок временного интервала, причем первые их входы соединеиы с шиной чтения, а вторые - с шиной импульсов записи процессора, выход регистра скорости соединен с третьим входом регистра дополнения до бита, выход которого подключен к входу процессора и третьему входу регистра временного интервала, выход которого соединеп с вторым входом буферного регистра и входом процессора, выход регистра остатка соединен с входом процессора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство преобразования временных интервалов в двоичный код для процесса сбора,обработки и передачи многоканального потока информации | 1982 |

|

SU1015494A2 |

| Устройство для синхронизацииВВОдА иНфОРМАции из КАНАлА СВязи | 1979 |

|

SU798774A1 |

| Устройство для преобразования временных интервалов в двоичный код | 1980 |

|

SU945980A1 |

| УСТРОЙСТВО КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ | 1994 |

|

RU2115231C1 |

| Устройство для сопряжения каналов ввода-вывода | 1975 |

|

SU559234A1 |

| ПРОЦЕССОР ДЛЯ ЦИФРОВОЙ СИСТЕМЫ ОБРАБОТКИ ДАННЫХ | 1971 |

|

SU305477A1 |

| Устройство для сопряжения процессора с памятью | 1986 |

|

SU1363229A1 |

| Устройство для сопряжения процессора с каналами связи | 1978 |

|

SU763882A1 |

| Устройство для сопряжения вычислительной машины с телеграфными каналами связи | 1986 |

|

SU1392571A1 |

| Устройство контроля электропитания процессора | 1984 |

|

SU1188741A1 |

Авторы

Даты

1975-12-30—Публикация

1972-09-08—Подача