1

Изобретение относится к области вычислительной техники и может быть использовано в системах контроля и диагностики неисправностей изделий -радиоэлектронной аппаратуры.

Известны устройства для поиска неисправностей, содержащие генератор тестов, выходы которого соединены с первыми входами контролируемого устройства, коммутатор, первые входы которого соединены с выходами контролируемого устройства, генератор тактовых импульсов, выход которого соединен с первым входом генератора тестов и вторым входом контролируемого устройства, и регистр сдвига.

Однако такие устройства отличаются сложностью, связаЕной с необходимостью задания кодов реакции.

Целью изобретения является упрощение устройства.

Поставленная цель достигается тем, что предлагаемое устройство содержит элемент «НЕ, триггер, элемент «И, элементы неравноаначности и счетчи.к, вход которого через элемент «И, соединенный с единичным выходом триггера, соединен с выходом генератора тактовых импульсов, с пер,вым входом сдвигового регистра и с первым входом элемента «НЕ, вход триггера соединен с выходом элемента «НЕ, вtopoй вход которого соединен с выходом сдвигового регистра, выходы триггеров разрядов сдвигового регистра соединены с первыми входами элементов неравнозначности, вторые входы которых соединены с выходами коммутатора, а выходы элементов неравнозначности соединены со входами триггеров разрядов сдвигового регистра, входы сброса счетчика и триггера соединены со входом коммутатора и вторым входом генератора тестов.

Это позволяет исключить задание вер.ных

кодов реакций и сформировать коды реакции

при использовании одного регистра сдвига

для контроля многовыходного устройства.

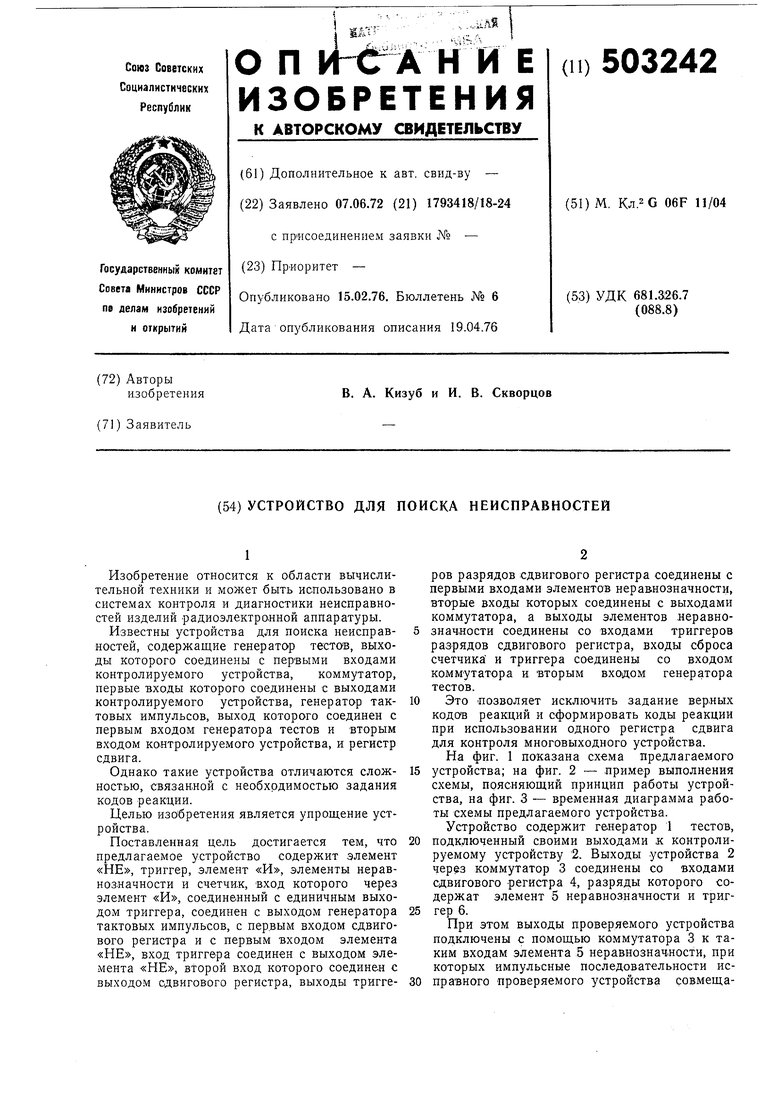

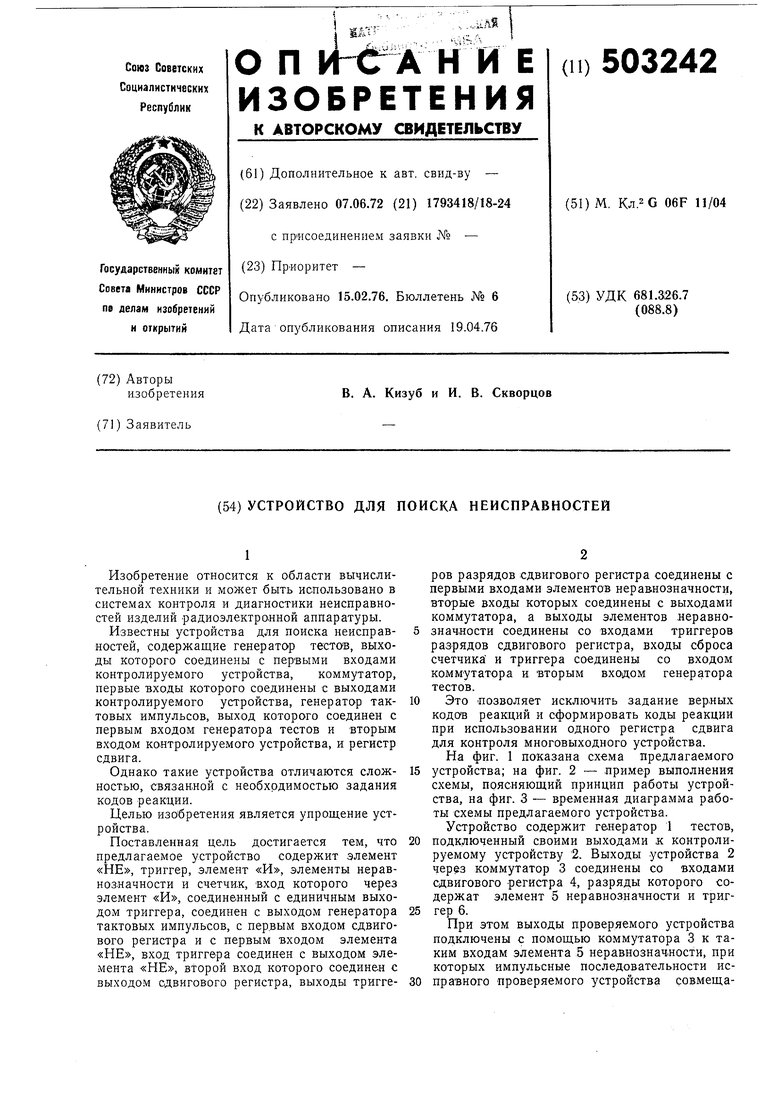

На фиг. 1 показана схема предлагаемого

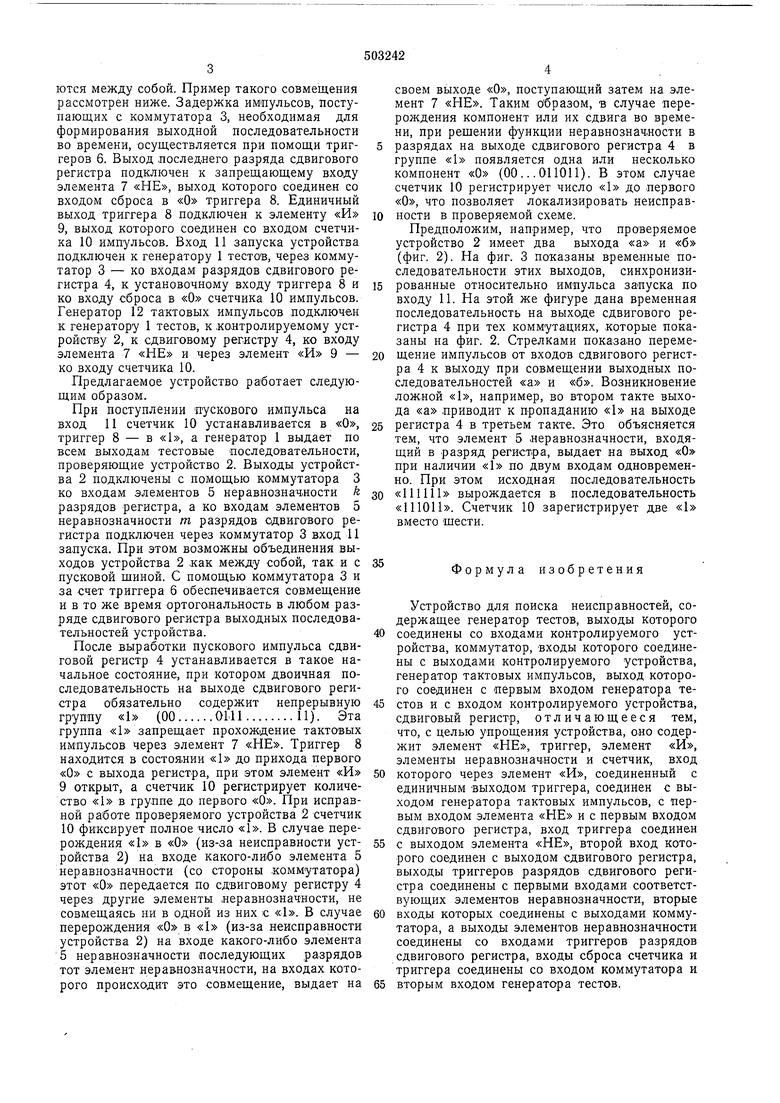

устройства; на фиг. 2 - пример выполнения схемы, поясняющий принцип работы устройства, на фиг. 3 - временная диаграмма работы схемы предлагаемого устройства. Устройство содержит генератор 1 тестов,

подключенный своими выходами к контролируемому устройству 2. Выходы устройства 2 через коммутатор 3 соединены со входами сдвигового -регистра 4, разряды которого содержат элемент 5 неравнозначности и триггер 6.

При этом выходы проверяемого устройства подключены с помощью коммутатора 3 к таким входам элемента 5 неравнозначности, при которых импульсные последовательности исправного проверяемого устройства совмещаются между собой. Пример такого совмещения рассмотрен ниже. Задержка импульсов, поступающих с коммутатора 3, необходимая для формирования выходной последовательности во времени, осуществляется при помощи триггеров 6. Выход последнего разряда сдвигового регистра подключен к запрещающему входу элемента 7 «НЕ, выход которого соединен со входом сброса в «О триггера 8. Единичный выход триггера 8 подключен к элементу «И 9, выход которого соединен со входом счетчика 10 импульсов. Вход 11 запуска устройства подключен к генератору 1 тестов, через коммутатор 3 - ко входам разрядов сдвигового регистра 4, к установочному входу триггера 8 и ко входу сброса в «О счетчика 10 импульсов. Генератор 12 тактовых импульсов подключен к генератору 1 тестов, к .контролируемому устройству 2, к сдвиговому регистру 4, ко входу элемента 7 «НЕ и через элемент «И 9 - ко входу счетчика 10.

Предлагаемое устройство работает следующим образом.

При поступлении пускового импульса на вход И счетчик 10 устанавливается в «О, триггер 8 - в «1, а генератор 1 выдает по всем выходам тестовые последовательности, проверяющие устройство 2. Выходы устройства 2 подключены с помощью коммутатора 3 ко входам элементов 5 неравнозначности k разрядов регистра, а ко входам элементов 5 неравнозначности т разрядов сдвигового регистра подключен через коммутатор 3 вход 11 запуска. При этом возможны объединения выходов устройства 2 ,как между собой, так и с пусковой шиной. С помощью коммутатора 3 и за счет триггера 6 обеспечивается совмещение и в то же время ортогональность в любом разряде сдвигового регистра выходных последовательностей устройства.

После выработки пускового импульса сдвиговой регистр 4 устанавливается в такое начальное состояние, при котором двоичная последовательность на выходе сдвигового регистра обязательно содержит непрерывную

группу «1 (0001-11И). Эта

группа «1 запрещает прохождение тактовых импульсов через элемент 7 «НЕ. Триггер 8 находится в состоянии «1 до прихода первого «О с выхода регистра, при этом элемент «И

9открыт, а счетчик 10 регистрирует количество «1 в группе до первого «О. При исправной работе проверяемого устройства 2 счетчик

10фиксирует полное число «1. В случае перерождения «Ь в «О (из-за неисправности устройства 2) на входе какого-либо элемента 5 неравнозначности (со стороны .коммутатора) этот «О передается по сдвиговому регистру 4 через другие элементы неравнозначности, не совмещаясь ни в одной из них с «1. В случае перерождения «О в «1 (из-за неисправности устройства 2) на входе какого-либо элемента

5 неравнозначности последующих разрядов тот элемент неравнозначности, на входах которого происходит это совмещение, выдает на

своем выходе «О, поступаю.щий затем на элемент 7 «НЕ. Таким образом, в случае перерождения компонент или их сдвига во времени, при рещении функции неравнозначности в разрядах на выходе сдвигового регистра 4 в группе «1 появляется одна или несколько компонент «О (00... 011011). В этом случае счетчик 10 регистрирует число «1 до первого «О, что позволяет локализировать неисправпости в проверяемой схеме.

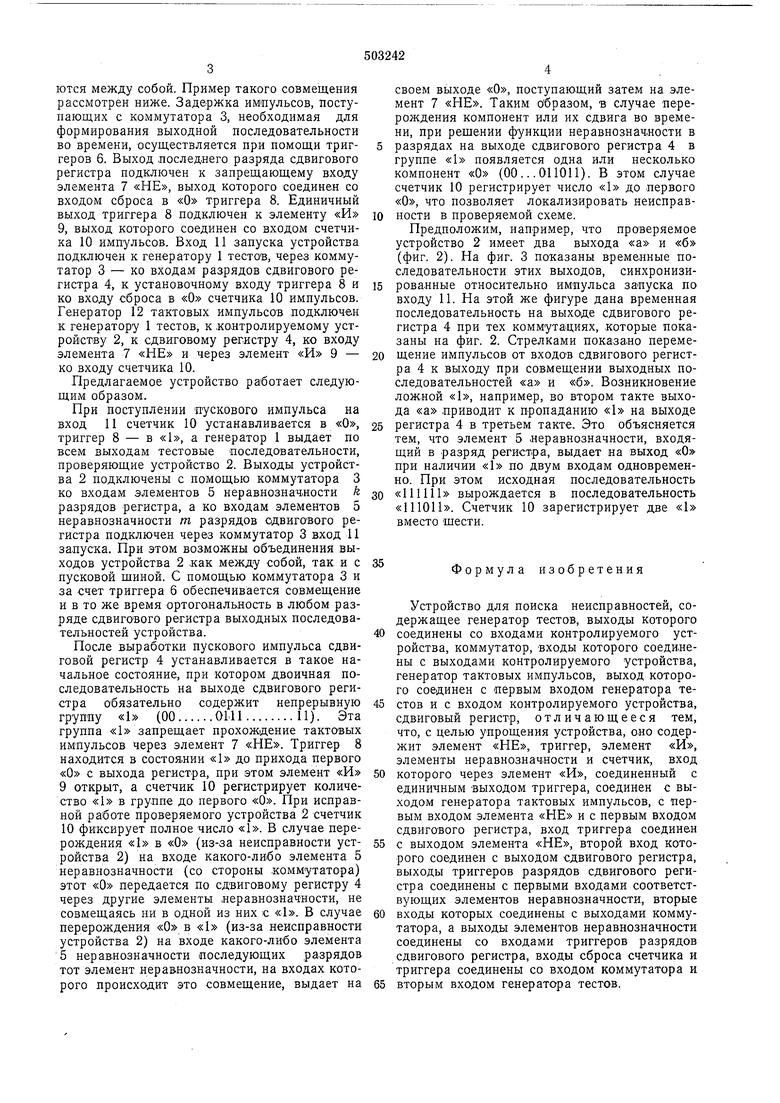

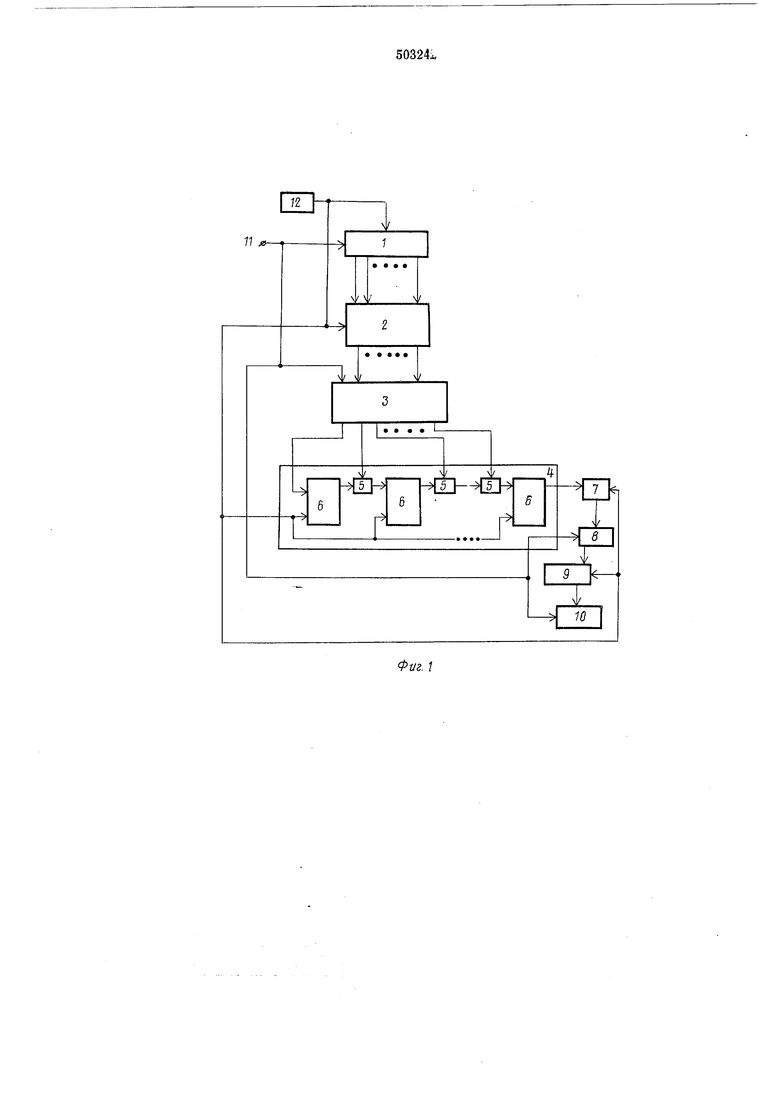

Предположим, например, что проверяемое устройство 2 имеет два выхода «а и «б (фиг. 2). На фиг. 3 показаны временные последовательности этих выходов, синхронизированные относительно импульса запуска по входу 11. На этой же фигуре дана временная последовательность на выходе сдвигового регистра 4 при тех коммутациях, .которые показаны на фиг. 2. Стрелками показано перемещение импульсов от входов сдвигового регистра 4 к выходу при совмещении выходных последовательностей «а и «б. Возникновение лож.ной «1, например, во втором такте выхода «а приводит к пропаданию «1 на выходе

регистра 4 в третьем такте. Это объясняется тем, что элемент 5 неравнозначности, входящий в разряд регистра, выдает на выход «О при наличии «1 по двум входам одновременно. При этом исходная последовательность

«111111 вырождается в последовательность «111011. Счетчик 10 зарегистрирует две «1 вместо шести.

Формула изобретения

Устройство для поиска неисправностей, содержащее генератор тестов, выходы которого

соединены со входами контролируемого устройства, коммутатор, входы которого соединены с выходами контролируемого устройства, генератор тактовых импульсов, выход которого соединен с первым входом генератора тестов и с входом контролируемого устройства, сдвиговый регистр, отличающееся тем, что, с целью упрощения устройства, о.но содержит элемент «НЕ, триггер, элемент «И, элементы неравнозначности и счетчик, вход

которого через элемент «И, соединенный с единичным выходом триггера, соединен с выходом генератора тактовых импульсов, с первым входом элемента «НЕ и с первым входом сдвигового регистра, вход триггера соединен

с выходом элемента «НЕ, второй вход которого соединен с выходом сдвигового регистра, выходы триггеров разрядов сдвигового регистра соединены с первыми входами соответствующих элементов неравнозначности, вторые

входы которых соединены с выходами коммутатора, а выходы элементов неравнозначности соединены со входами триггеров разрядов сдвигового регистра, входы сброса счетчика и триггера соединены со входом коммутатора и

вторым входом генератора тестов.

11

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для поиска кратных дефектов в группе объектов | 1983 |

|

SU1233157A1 |

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

| Устройство для контроля блоков памяти | 1981 |

|

SU951408A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU1014041A1 |

| Устройство для группового контроля логических блоков | 1986 |

|

SU1372323A1 |

| Устройство для контроля блоков оперативной памяти | 1983 |

|

SU1161993A1 |

| Устройство для контроля и диагностики дискретных объектов | 1980 |

|

SU942025A1 |

| Устройство для управления реконфигурацией резервированной вычислительной системы | 1991 |

|

SU1837296A1 |

| Система автоматического контроля параметров электронных схем | 1989 |

|

SU1700538A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU1001182A1 |

-иг.

Авторы

Даты

1976-02-15—Публикация

1972-06-07—Подача