1 .

Изобретение касается запоминающих ус-гройств

Известно запоминающее устройство с самоконтролем, содержащее накопитель, подключенный к регистру адреса, блок анализа соединенный с первым регистром числа, второй и третий регистры числа, блоки контроля и коррекции, преобразователи кодов, управляющие входы которых подключены к выходу одного из блоков контроля, а выход первого и вход второго преобразователей кодов соединены соответственно со входом и выходом первого регистра числа,

В предложенном устройстве вход первого преобразователя кодов подключен к вы- ходу третьего регистра числа, а выход второго преобразователя кодов - ко входу другого блока контроля.

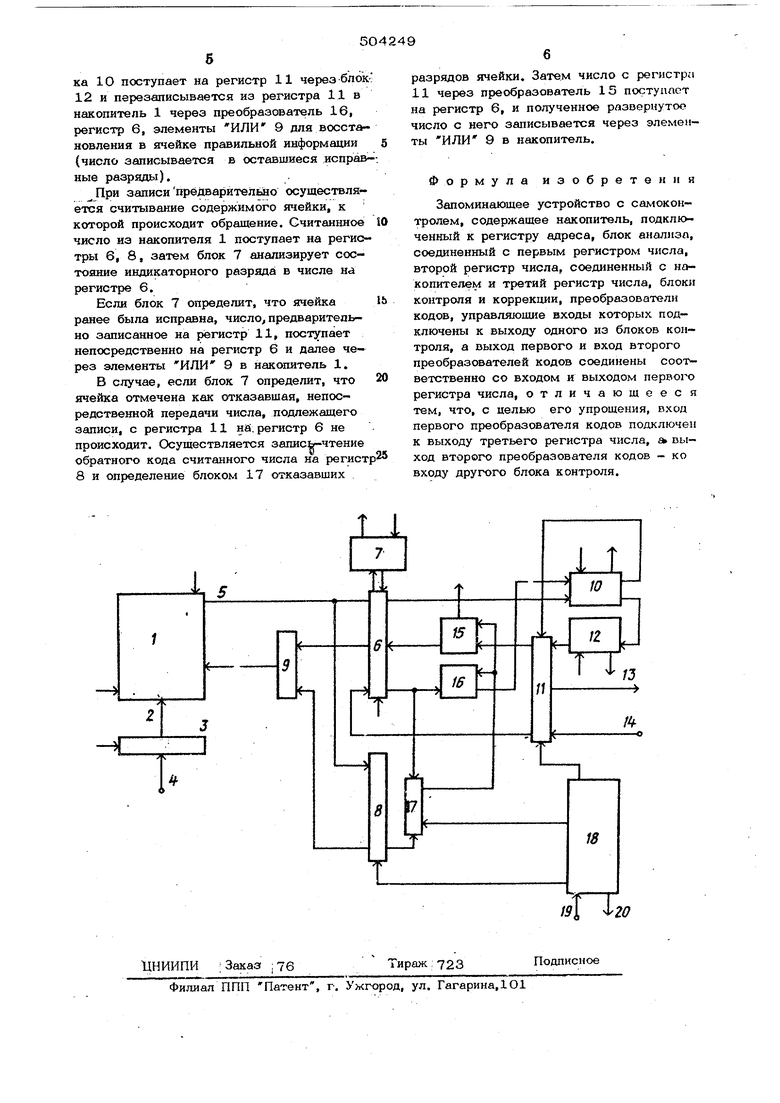

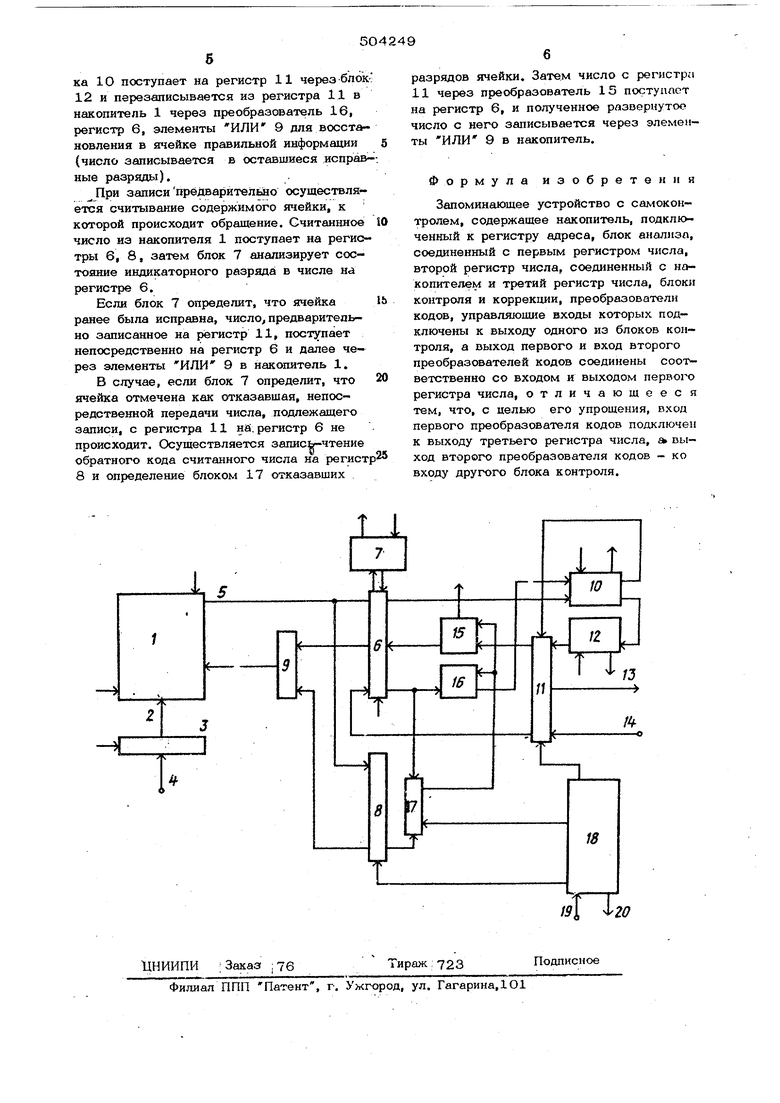

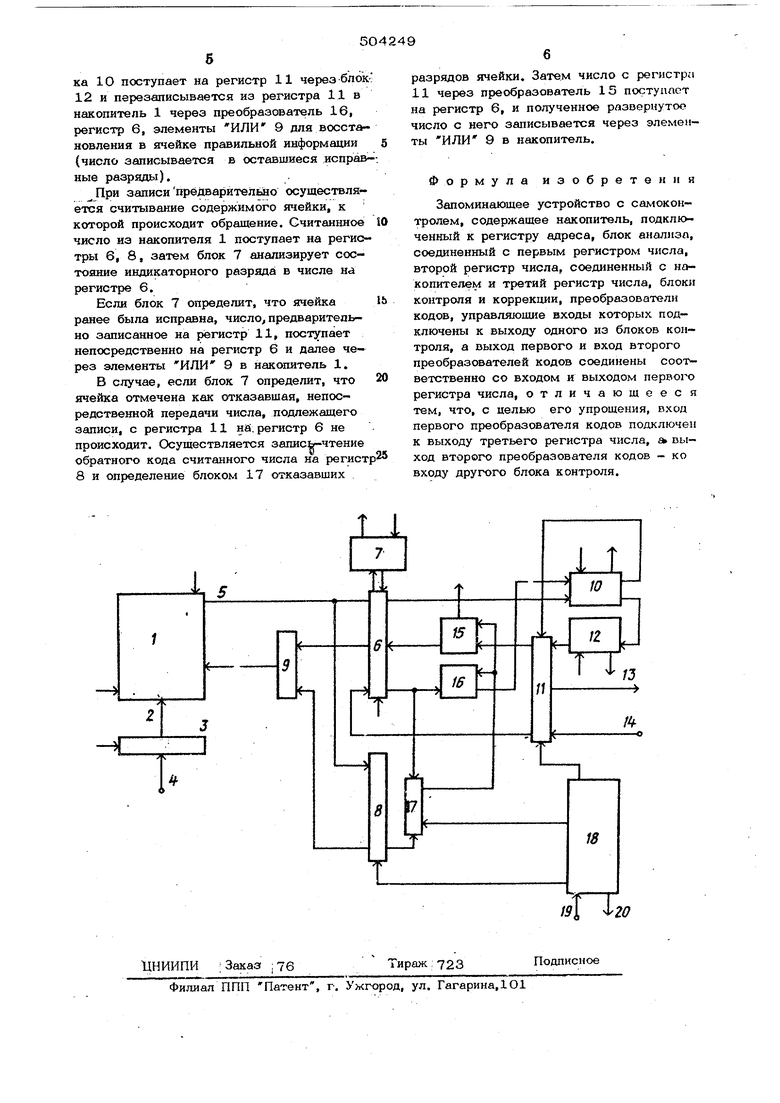

На чертеже приведена блок-схема предложенного устройства.

i Устройство содержит накопитель 1, каждая ячейка которого имеет определенное число резервных разрядов. Ко входу 2 на- копителя i подключен регистр адреса 3 с информационным входом 4. Информационный

выход 5 накопителя 1 соединен со входом первого регистра числа 6, подключенного к блоку анализа 7, и со входом второго регистра 8 числа. Выходы регистров 6, 8 чарез группу элементов ИЛИ 9 связаны с информационным входом накопителя 1. Другой выход регистра, 6 соединен со входом блока контроля 1О, один выход которого связан непосредственно со входом трет его регистра 11 числа, а другой выход соединен со вxoдo регистра 11 через блок коррекции 12. Один выход регистра 11 связан с выходом 13 устройства, другой выход регистра 11 соединен с другим входом региг-тра 6, а другой вход регистра Пев. зан со входом 14 устройства. Выход регистра 11 через преобразователь 15 кодов (в качестве преобразователя 15 может быть использован, например, шифратор) подклк чен ко входу регистра 6, а выход регист ра 6 через преобразовтхэль кодов 1G ( Е качестве преобразователя 16 мо/кот быть использован, например, игифрато) подклк:)- чей ко входу блока 1О. Уираидяюшт ; ихгьды преобразователеii 15, Hi co ;;iuii(M.i с выходом блока контроля 17, служащего для определения отказавших разрядов, входы которого связаны с выходами регистро 6 и 8. Для синхронизации работы перечис- ленных блоков устройства служит; блок уп равления 18, который имеет вход 19 и вы ход- 20. Для обращения к ячейке накопителя 1 адрес её необходимо подать на, вход 4 регистра 3.1 ,,, ;. При считывании число из накопителя 1 поступает на регистры 6, 8 и далее из регистра 6 в блок 10, Блок 10 опре деляет наличие ошибки в считанном числе Если сигнал ошибки из блока 10 отсутс- твует, число из него непосредственно поступает на регистр 11, а затем - на выход 13. Если сигнал ошибки имеет место, число принимае-гся на регистр 11 через блок 12. В результате на регистре 11 будет находиться исправленное число, которое может быть затем вьщано на выход 13, Для того, чтобы при последующих обращениях к отказавшей ячейке с.читьшаемое число не содержало; ошибок необходимо обеспечить запись этого числа в имеющиеся исправные разряды ячейки. Этот процесс будем называть разверткой числа. При считывании развернутого числа из отказавшей ячейки оно должно быть выбрано из исправных разрядов этой ячей ки. Этот процесс будем называть CBepi кой. числа. , Йтак,после приема исправленногочйела из блока 12 ща регистр 11 оно должно быть развернуто и записано в исправные разряды отказавшей ячейки. Для этого из регистра 8 в отказавшую ячейку накопителя 1 через элементы ИЛИ 9 записывают обратный код считанного числа и считывают его на этот же регистр 8. Таким образом, на регистрах 6, 8 будут находиться соответственно прямой и обратный коды числа, считанные из отказавшей ячейки:. Блок 17 по совпадению содержимого одноименных разрядов регис тров 6, 8 определяет отказавшие разряды ячейки - наксшителя 1 и запоминает пози- ции отказавших разрядов. Преобразовател 15 запрещает запись информации в разряды регистра 6, соответствующие отка завшим разрядам ячейки накопителя 1, обеспечивая развертку (распределение) правильного числа по разрядам регистра 6, которым соответствуют исправные разряды ячейки. Допустим а ячейку, содержащую два отказавших разряда, было записано следующее число 11О1, при считывании которого на регистр 6 поступило число : 000100 /подчеркнутые 1-и и 4-й ра:з- ряды, считая справа, отказали, &-й и 6-й: разряды являются рюзервными/. После аписи-чтения обратного кода считанного чила на регистр 8 поступит число 110010 и лок 17 определит, что 1-й, 4-й разряды тказали. При этом на регистре 11 бует находиться поступившее из блока 12 равильное число 1101, которое необходио записать в исправные разряды отказавей ячейки. При передаче числа 11О1 на егистре 11 через преобрапователь 15 на егистр б поступит следуюшее число 11.01. точками обозначены отказавшие 1-й, 4-й азряды, в которые информация не поступат, а сдвигается в исправные 2-и, 3-и и езервные 5-й, 6-и разряды). -..- .- . Развернутое число из регистра 6 поступает через группу элементов ИЛИ 9 в соответствующую ячейку накопителя 1. Для того, чтобы в дальнейшем при считывании числа из отказавшей ячейки знать, что ячейка отказала, блок 7 обеспечивает маркирование этой ячейки, например, путем установки в О специального индикаторного разряда (или группы индикаторных разрядов), находившегося в 1, когда ячейка была исправна. Так устройство работает, когда блок 7 сигнализирует, что ячейка,к которой происходит обращение, ранее была исправна. При обнаружении блоком 7 ранее отказавшей ячейки число из регистра 6 в блок 1О не поступает. Производится запись обратного кода считанного числа из регистра 8 в ют казавшую ячейку через группу элементов ИЛИ 9 и последующее чтение его на этот же регистр 8. Отказавшие разряды ячейки определяются блоком 17. Преобразователь 16 выбирает число из разрядов регистра 6, соответствующих исправным разрядам ячейки, т. е. осуществляет свертку числа. Для иллюстрации рассмотрим пример. Допустим, обращение происходит в указанной выше отказавшей ячейке. При этом на регистр 6 поступит с.ледующее число 11OO1Q. После записи-чтения обратного кода.считанного числа на регистр 8 поступит число OOQIOQ, и блок 17 определит, что 1-и, 4-и разряды (считая справа) отказа;ш. При передаче числа 11Q01Q из регистра,6 через преобразователь 16 в блок 10 поступит свернутое число 11О1. .-Блок 10 определяет наличие ошибки в свернутом числе. Если ошибка отсутствует, . число из блока 10 записывается непосредственно на регистр 11 и выдается на выход 13. Если же ошибка есть, число из блока 10 поступает на регистр 11 через блок12 и перезаписывается из регистра 11 в накопитель 1 через преобразователь 16, регистр 6, элементы ИЛИ 9 для восстановления в ячейке правильной информации (число записывается в оставшиеся исправ

ные разряды)

При записипредварительно осуществляется считывание содержимого $гчейки, к которой происходит обращение. Считаннное число из накопителя 1 поступает на регистры 6, 8, затем блок 7 анализирует состояние индикаторного разряда в числе на регистре 6.

Если блок 7 определит, что ячейка

ранее была исправна, число,предварительно записанное на регистр 11, поступает непосредственно на регистр 6 и далее через элементы ИЛИ 9 в накопитель 1.

В случае, если блок 7 определит, что ячейка отмечена как отказавшая, непосредственной передачи числа, подлежащего записи, с регистра 11 ни регистр 6 не происходит. Осуществляется запись-чтение обратного кода считанного числа на регист 8 и определение блоком 17 отказавших

разрядов ячейки. Затем число с регистра 11 через преобразователь 15 поступает на регистр 6, и полученное развериутоо число с него записывается через элементы ИЛИ 9 в накопитель.

Формула изобретения

Запоминающее устройство с самоконтролем, содержащее накопитель, подкли ченный к регистру адреса, блок анализа, соединенный с первым регистром числа, второй регистр числа, соединенный с накопителем и третий регистр числа, блоки контроля и коррекции, преобразователи кодов, управл5иошие входы которых подключены к выходу одного из блоков контроля, а выход первого и вход второго преобразователей кодов соединены соответственно со входом и выходом nepBOix) регистра числа, отличающееся тем, что, с целью его упрощения, вход первого преобразователя кодов подключен к выходу третьего регистра числа, выход второго преобразователя кодов - ко входу другого блока контроля.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1974 |

|

SU519767A1 |

| Запоминающее устройство с автономнымКОНТРОлЕМ | 1979 |

|

SU842977A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU920849A2 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU888214A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU936033A1 |

| Запоминающее устройство с самоконтролем | 1979 |

|

SU883975A2 |

| Запоминающее устройство с самоконтролем | 1976 |

|

SU595795A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU963109A2 |

| Резервированное запоминающее устройство | 1975 |

|

SU619966A1 |

| Оперативное запоминающее устройство с автономным контролем | 1983 |

|

SU1113855A2 |

1 Т

ю

±

15

/2

Т,з

16

П

/4

-

Авторы

Даты

1976-02-25—Публикация

1974-11-28—Подача