(54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО КОНТРОЛЕМ С АВТОНОМНЫМ ., гг,пЦ;г.« 1 b,.,,...v..... л liAYS fn/O ТЕХКйЧЙСКАй

теля подключен к выходу регистра адреса, выход - к первому входу первого и входу второго регистров числа, первые выходы которых соединены с одними из входов элементов ИЛИ, второй вход первого регистра числа подключен к выходу первого преобразователя кодов, вторые выходы первого и второго регистров числа соединены соответственно с первыми входами второго преобразователя кодов и блока контроля, второй вход которого подключен ко второму выходу, второго регистра числа, первый выход, третьего регистра числа соединен с первым входом первого преобразователя кодов, вторые входы преобразователей кодов подключены к выходу блока контроля, управляющие входы регистра адреса, накопителя, регистров числа и блока контроля подключены к одним из выходов блока управления, одни из входов которого соединены с управляющими выходами первого и второго регистров числа, содержит схему сравнения, входы которой подключены соответственно ко вторым выходам первого и третьего регистров числа, а выход соединен с третьим входом первого регистра числа, третий выход которого соединен с первым входом третьего регистра числа, второй вход которого подключен к выходу второго преобра зователя кодов, а второй выход - к другим входам элементов ИЛИ, выходы которых соединены с информационными входами накопителя, управляющие вход и выход схемы сравнения подключены соответственно к другим выходу и входу блока управления.

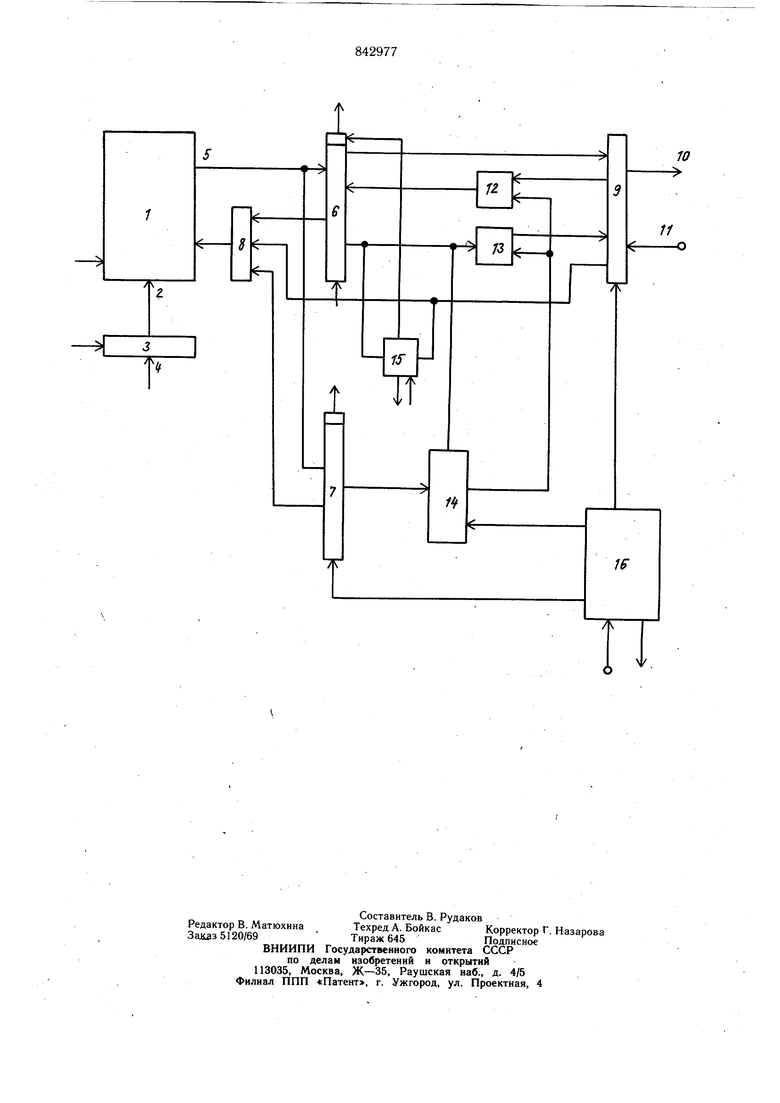

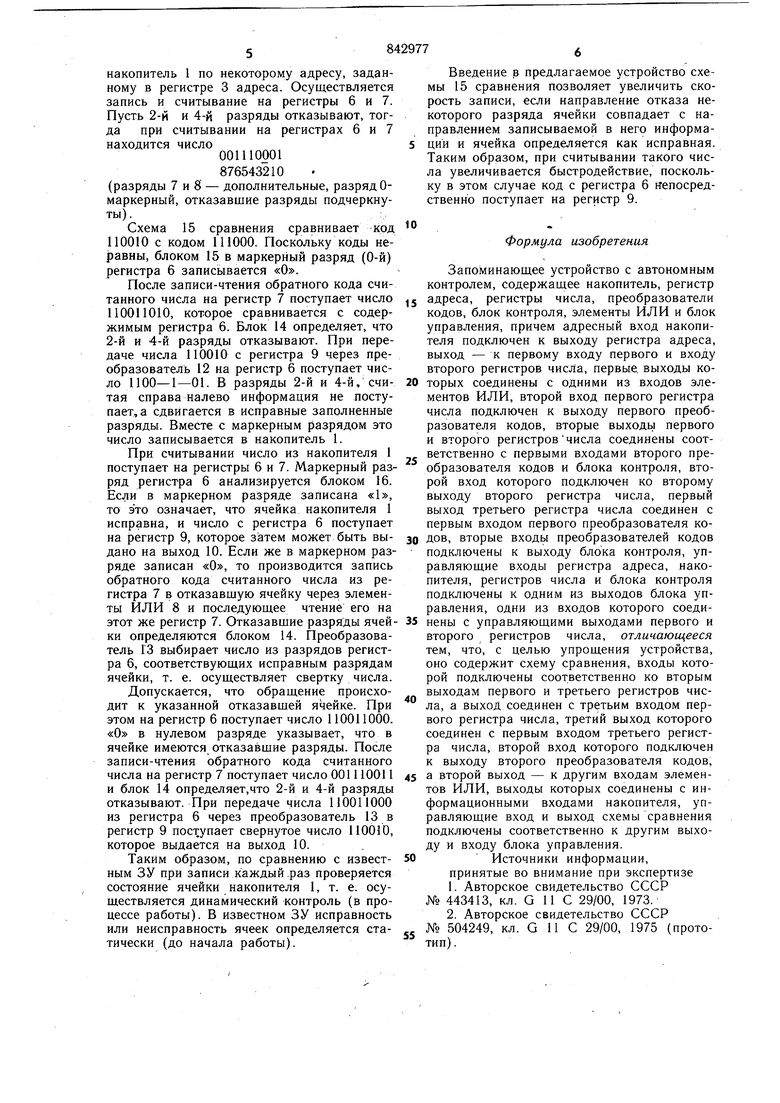

На чертеже приведена структурная схема предлагаемого устройства.

Устройство содержит накопитель 1, каждая ячейка которого имеет маркерный разряд и определенное число дополнительных разрядов. К адресному входу 2 накопителя 1 подключен регистр 3 адреса со входом 4. Информационный выход 5 накопителя 1 соединен с первым входом первого регистра 6 числа и входом второго регистра 7 числа. Первые выходы регистров 6 и 7 подключены к одним из входов элементов ИЛИ 8. Устройство содержит также третий регистр 9 числа, имеющие выход 10 и вход 11, являющиеся соответственно выходом и входом устройства, первый 12 и второй 13 преобразователи кодов, блок 14 контроля, схему 15 сравнения и блок 16 управления. Второй вход регистра 6 подключен к выходу преобразователя 12. Вторые выходы регистров 6 и 7 соединены соответственно с первыми входами преобразователя 13 и блока 14 контроля, второй вход котброго подключен ко второму входу регистра 7. Первый выход регистра 9 соединен с первым входом преобразователя 12. Вторые входы преобразователей 12 и 13 подключены к выходу блока 14 контроля. Входы схемы 15 сравнения подключены соответственно ко вторым выходам регистров 6 и 9, а выход

соединен с третьим входом регистра 6, третий выход которого соединен с первым входом регистра 9, второй вход которого подключен к выходу преобразователя 13, а второй выход - к другим входам элементов

ИЛИ 8, выходы которых соединены с информационными входами накопителя 1. Управляющие вход и выход схемы 15 сравнения подключены к соответствующим выходу и входу блока 16 управления.

Устройство работает следующим образом.

0 Обращение к ячейке накопителя 1 осуществляется по адресу, записанному в регистре 3 адреса. При записи число из регистра 9 поступает в ячейку накопителя 1 через элементы ИЛИ 8. Затем осуществляется считывание этого числа и через информационный выход 5 накопителя 1 оно поступает на регистрб 6 и7. Схема 15 сравнения осуществляет сравнение записываемого числа и вновь считанного. Если имеет место равенство, то все разряды ячейки накoJIитeля ) исправны и запись на этом заверщается. Если же имеет место неравенство, то по сигналу со схемы 15 сравнения в маркерный разряд регистра 6 записывается «О. Обозначается: логическая «1 в маркерном разряде означает, что ячейка исправна; «О - в ячейке имеются отказавщие разряды. Первоначально во всех маркерных разрядах ячеек накопителя 1 записана «1.

Запись «О в маркерный разряд регистQ ра 6 означает, что ячейка, к которой осуществляется обращение, содержит отказавщие разряды. В этом случае необходимо определить номера отказавщих разрядов с тем, чтобы записать информацию в оставщихся исправные основные и дополнительные разряды, т. е. выполнить развертку числа. При считывании развернутого числа из отказавщей ячейки оно выбрано из исправных разрядов этой ячейки, т. е. выполняется свертка числа.

Итак, записываемое число, находящееся

на регистре 9 должно быть развернуто и записано в исправные разряды. Для этого из регистра 7 в отказавшую ячейку накопителя 1 через элементы ИЛИ 8 записывают обратный код считанного числа и считыванием его на этот же регистр 7. Таким образом, на регистрах 6 и. 7 находятся соответственно прямой и обратный коды числа. Блок 14 по совпадению содержимого одноименного разрядов регистров 6 и 7 определяет отказавщие разряды ячейки накопителя 1 и запоминает номера позиций отказавщих разрядов. Преобразователь 12 запрещает запись информации в разряды регистра 6, соответствующие отказавщим разрядам ячейки накопителя 1, обеспечивая развертку правильного числа из регистра 9 по разрядам регистра 6, которым соответствуют исправные разряды ячейки.

Допустим, что в регистре 9 находится чис ло 110010, которое необходимо записать в накопитель 1 по некоторому адресу, заданному в регистре 3 адреса. Осуществляется запись и считывание на регистры 6 и 7. Пусть 2-й и 4-й разряды отказывают, тогда при считывании на регистрах б и 7 находится число 001110001 876543210 (разряды 7 и 8 - дополнительные, разряд 0маркерный, отказавшие разряды подчеркнуты) . Схема 15 сравнения сравнивает код 110010 с кодом 111000. Поскольку коды неравны, блоком 15 в маркерный разряд (0-й) регистра 6 записывается «О. После записи-чтения обратного кода считанного числа на регистр 7 поступает число 110011010, которое сравнивается с содержимым регистра 6. Блок 14 определяет, что 2-й и 4-й разряды отказывают. При передаче числа 110010 с регистра 9 через преобразователь 12 на регистр 6 поступает число 1100-1-01. В разряды 2-й и 4-й, считая справа налево информация не поступает, а сдвигается в исправные заполненные разряды. Вместе с маркерным разрядом это число записывается в накопитель 1. При считывании число из накопителя 1 поступает на регистры 6 и 7. Маркерный разряд регистра 6 анализируется блоком 16. Если в маркерном разряде записана «1, то это означает, что ячейка накопителя 1 исправна, и число с регистра 6 поступает на регистр 9, которое может быть выдано на выход 10. Если же в маркерном разряде записан «О, то производится запись обратного кода считанного числа из регистра 7 в отказавщую ячейку через элементы ИЛИ 8 и последующее чтение его на этот же регистр 7. Отказавщие разряды ячейки определяются блоком 14. Преобразователь ГЗ выбирает число из разрядов регистра 6, соответствующих исправным разрядам ячейки, т. е. осуществляет свертку числа. Допускается, что обращение происходит к указанной отказавшей ячейке. При этом на регистр 6 поступает число 110011000. «О в нулевом разряде указывает, что в ячейке имеются отказавшие разряды. После записи-чтения обратного кода считанного числа на регистр 7 поступает число 001110011 и блок 14 определяет,что 2-й и 4-й разряды отказывают. При передаче числа 110011000 из регистра 6 через преобразователь 13 в регистр 9 поступает свернутое число 110010, которое выдается на выход 10. Таким образом, по сравнению с известным ЗУ при записи каждый .раз проверяется состояние ячейки накопителя 1, т. е. осуществляется динамический контроль (в процессе работы). В известном ЗУ исправность или неисправность ячеек определяется статически (до начала работы). Введение в предлагаемое устройство схемы 15 сравнения позволяет увеличить скорость записи, если направление отказа некоторого разряда ячейки совпадает с направлением записываемой в него информации и ячейка определяется как исправная. Таким образом, при считывании такого числа увеличивается быстродействие, поскольку в этом случае код с регистра 6 непосредственно поступает на регистр 9. Формула изобретения Запоминающее устройство с автономным контролем, содержащее накопитель, регистр адреса, регистры числа, преобразователи кодов, блок контроля, элементы ИЛИ и блок управления, причем адресный вход накопителя подключен к выходу регистра адреса, выход - к первому входу первого и входу второго регистров чисЛа, первые, выходы которых соединены с одними из входов элементов ИЛИ, второй вход первого регистра числа подключен к выходу первого преобразователя кодов, вторые выходы первого и второго регистровчисла соединены соответственно с первыми входами второго преобразователя кодов и блока контроля, второй вход которого подключен ко второму выходу второго регистра числа, первый выход третьего регистра числа соединен с первым входом первого преобразователя коДов, вторые входь преобразователей кодов подключены к выходу блока контроля, управляющие входы регистра адреса, накопителя, регистров числа и блока контроля подключены к одним из выходов блока управления, одни из входов которого соединены с управляющими выходами первого и второго регистров числа, отличающееся тем, что, с целью упрощения устройства, оно содержит схему сравнения, входы которой подключены соответственно ко вторым выходам первого и третьего регистров числа, а выход соединен с третьим входом первого регистра числа, третий выход которого соединен с первым входом третьего регистра числа, второй вход которого подключен к выходу второго преобразователя кодов, а второй выход - к другим входам элементов ИЛИ, выходы которых соединены с информационными входами накопителя, управляющие вход и выход схемы сравнения подключены соответственно к другим выходу и входу блока управления. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 443413, кл. G 11 С 29/00, 1973. 2.Авторское свидетельство СССР № 504249, кл. G 11 С 29/00, 1975 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1974 |

|

SU504249A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU920849A2 |

| Запоминающее устройство с самоконтролем | 1974 |

|

SU519767A1 |

| Запоминающее устройство с автономным контролем | 1983 |

|

SU1081669A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU936033A1 |

| Запоминающее устройство с самоконтролем | 1979 |

|

SU883975A2 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU888214A1 |

| Резервное запоминающее устройство | 1976 |

|

SU604036A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU963109A2 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1133623A2 |

Авторы

Даты

1981-06-30—Публикация

1979-07-12—Подача