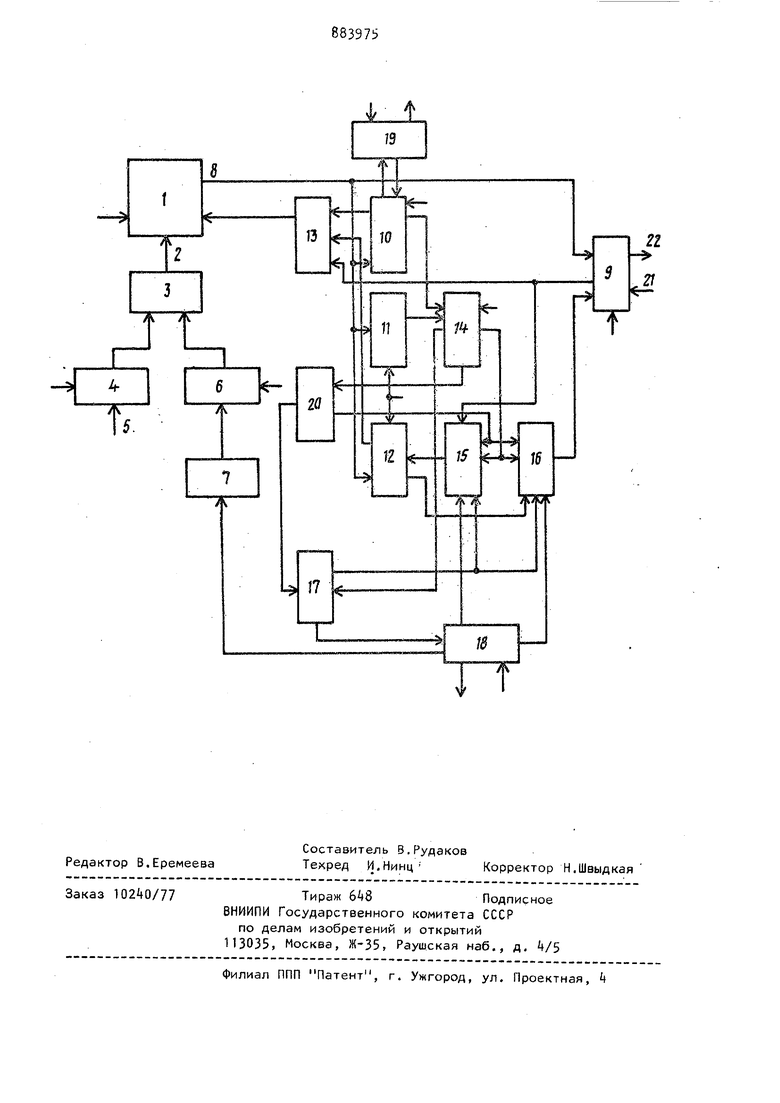

Изобретение относится к запоминающим устройствам. По основному авт.свт. № 7 +8515 известно устройство, содержащее накопитель, регистры числа, группы элементов ИЛИ, регистры адреса, счетчик адресов, блок контроля, блок управления и блок местного управления, причем выход накопителя подключен к первым входам первого, второго итретьего регистров числа, входы накопителя соединены с выходами элементов ИЛИ, входы элементов ИЛИ первой группы подключены к выходам первого и второго регистров адреса, вход которого соединен с выходом счетчика адресов, первый выход второго и выход первого регистров числа подключены к одним из входов второй группы элементов ИЛИ, вторые входы и выходы второго регистра числа соединены, соответственно, с выходом блока местного управления и первым входом блока конт роля, второй вход которого соединен С выходом третьего регистра числа, один из выходов блока управления подключен к управляющим входам накопителя, первого и второго регистра адреса, счетчика адресов, первого, второго и третьего регистров числа, блока контроля и блока местного управления. Устройство содержит также четвертый регистр числа, коммутаторы и счетчик адресов, причем входы четвертого регистра числа подключены, соответственно, к выходам накопителя и первого коммутатора, а выходы - к другим входам элементов ИЛИ второй группы и к первому входу второго коммутатора , выход которого подключен к первому входу первого коммутатора, вторые и третьи входы первого и второго коммутатора соединены, соответственно, с первыми выходами блока накопителя и счетчика разрядов, вторые входы которых подключены, соответственно, ко входам счетчика разрядов и блока управления, управляющие 8 входы четвертого регистра числа и коммутаторов соединены с другими выходами блока управления ll . Недостатком этого устройства является то, что в резервных ячейках не должно быть отказавших разрядов, oi раничивающих обращение к запоминающему устройству, так как ячейки с отказавшими разрядами не могут быть использованы в качестве резервных, что снижает надежность устройства. Цель изобретения - повышение надеж ности устройства за счет сохранения работоспособности устройства в случае, когда резервные ячейки имеют отказавшие разряды. Поставленная цель достигается тем что устройство содержит регистр адре са отказов, вход которого соединен с выходом блока контроля, первый выхьд - со входом счетчика разрядов, а второй выход подключен ко входам коммутаторов. На чертеже .представлена структурная схема предлагаемого устройства. Устройство содержит накопитель 1, имеющий входы 2, первую группу элементов -ИЛИ 3, первый регистр А адреса, имеющий вход 5, второй регистр 6 адреса, счетчик 7 адресов. К выходам 8 накопителя 1 подключены одни из вх дов первого регистра 9 числа, второг регистра 10 числа, вход третьего регистра 11 числа и один из входов четвертого регистра 12 числа. Устройство содержит также вторую группу элементов ИЛИ 13, блок контроля И, первый 15 и второй 1б комму таторы, су|етчик 17 разрядов, блок 18 управления, блок 13 местного управле ния, регистр 20 адреса отказов. При этом выходы 2 накопителя 1 соединены с выходами элементов ИЛИ 3 выходы которых подключены к выходам первого, k и второго 5 регистров адре са. Вход регистра 6 соединен с выходом 7 адресов.Выход регистра 9 числа и один из выходов регистра 10 числа подключены к одним из входов элементов ИЛИ 13, выход которых подключен к входу накопителя 1. Другие вход и выход регистра 10 числа соединены, соответственно, с выходом блока 19 местного управления и первым входом блока 14 контроля, второй вход которого подключен к выходу третьего регистра 11 числа, а один из выходов ко входу регистра 20, первый и аторой выходы которого подключены, со4тветственно, ко входу счетчика разрядов и к входам первого 15 второго 16 коммутаторов. Устройство работает следующим образом. В исходном состоянии счетчик 17 разрядов обнулен. Для каждого линейного участка программы или для массива чисел, которые записываются или считываются последовательно выделяются резервные ячейки накопителя 1. В счетчик 7 адресов при этом записывается адрес первой резервной ячейки, а на вход 5 основного регистра 4 адреса поступает адрес первой ячейки записываемого или считываемого массива чисел. При записи информации сначала осу-. ществляется контроль исправности разрядов резервной ячейки. Адрес резервной ячейки из счетчика 7 передается через регистр 6 адреса на вход 2 накопителя 1. Производится чтение содержимого резервной ячейки на регистр 10 затем осуществляется запись-считывание обратного кода содержимого резервной ячейки на регистр 11. Содержимое регистров 10 и 11 подается на блок И контроля. 8 случае, если отказавших разрядов в ячейке нет, то регистр 20 и счетчик 17 разрядов остаются в О состоянии. При наличиии отказавших разрядов в соответствующие им разряды регистра 20 записывается 1, в счетчик 17 - количество отказавших разрядов, а в маркерный разряд резервной ячейки накопителя - 1. Далее осуществляется запись массива числа. Число поступает в регистр 9, и содергжимое регистра 4 адреса через элементы ИЛИ 3 подается на вход накопителя 1. Обратный код из регистра 9 через элементы ИЛИ 13 записывается в ячей ку накопителя 1, затем содержимое ячейки считывается «а регистр 11 и осуществляется запись-считывание прямого кода числа на регистр 10. Если блок 14 контроля не обнаружил в ячейке отказавшие разряды, то в регистр 4 поступает следующий адрес и аналогично производится запись второго числа. Если же в ячейке есть отказавшие разрядь, то блок 14 контроля, счетчик 17 разрядов и дополнительный регистр 20 выдает на коммутатор 15 сигналы, по которым из регистра 9 в младшие разряды регистра 12 передаются разряды числа, соответствующие отказавшим разрядам ячейки, причем в 58 разряды регистра 12, соответствующие 1 регистра 20 (т.е. отказавшие разряды резервной ячейки), запись не производится, они пропускаются и не используются. Затем с блока k контроля в счетчик 17 разряда записывается код , соотч етствующий количеству отказавших разрядов ячейки. Из блока 18 управления и блок 19 местного управления поступает сигнал, по которому в маркерный разряд ячейки н копителя 1 через регистр 10 записывается 1. Аналогично производится запись числа во вторую отказавшую ячейку. Только соответствующие разряды регистра 9 записываются с следую- щих младших незанятых разрядов регист ра 12 (с пропуском разрядов,соответствующих отказавшим разрядам резервной ячейки). После того, как все разряды регистра 12 .заполнятся счетчик разрядов выдает сигнал заполнения в блок 18 управления. Адрес резервной ячейки из счетчика 7 адресов поступает на регистр 6 адреса и через элементы ИЛИ 3 на вход 2 накопителя 1. Содержимое регистра 12 через .элементы ИЛИ 3 записывается в первую резервную ячейку массива чисел. После этого по сигналу из блока 18 управления в счетчике 7 адреса формируется адрес следующей резервной ячейки. Чтение информации производится сле дующим образом. В регистр k адреса подается адрес первой ячейки считываемого массива чи ла, а в счетчик 7 адреса записывается адрес первой резервной ячейки массива чисел. Счетчик 17 разрядов при это находится в нулевом состоянии. По сиг налу из блока 18 управления производится передача содержимого счетчика 7 адреса, через регистр 6 адреса и элементы ИЛИ 3 на вход накопителя 1. Про изводится чтение числа из резервной 12 и 10. Если в ма ячейки на регистры керном разряде резервной ячейки код II 111 ,то осуществляется запись-чтение ; обратного кода на регистр 11. Содержимое регистров 10 и 11 подается на блок И контроля. По сигналам блока 1 записывается 1 в разряды регистра 20, соответствующие отказавшим раз рядам резервной ячейки, а в счетчик 17 записывается количество этих разрядов. Если в маркерном разряде код О то счетчик 17 и разряды 20 остаются в О состоярегистра5 Затем из регистра 6 адреса поступает адрес первой ячейки считываемого массива числа и производится чтение на регистры 9 и 10. Если в маркерном разряде код О то, следовательно, в ячейке не было отказавших разрядов и число из регистра 9 поступает на его выход. Если же в маркерном разряде код 1, то производится запись-чтение обратного кода числа на регистр 11. Содержимое регистров 10 и 11 подается на блок 1 контроля. По сигналам блока 14 контроля, регистра 20, счетчика 17 разрядов через второй коммутатор 16 производится передача младших разрядов регистра 12 в регистр 9, причем разряды регистра 12, соответствующие взведенным разрядам регистра 20, пропускаются. Отказавшие разряды основной ячейки, таким образом, подменяются разрядами резервной ячейки. Число из регистра 9 поступает на его выход. В счетчИк 17 разрядов записывается код, соответствующий количеству использованных разрядов регистра 12. Если все разряды регистра 12 использованы, на что указывает соответствующее состояние счетчика 17 разрядов, то по сигналу из блока 18 управления счетчика 7 адреса формируется адрес следующей резервной ячейки. Содержимое резервн й ячейки считывается на регистр 12 и аналогично продолжается считывание массива числа с подменой отказавших разрядов. Предлагаемое устройство позволяет использовать в качестве резервной ячейки любую ячейку накопителя независимо от наличия в ней отказавших разрядов. Формула изобретения Запоминающее устройство с самокрнтолем по авт.св. № , отлиающееся тем, что, с целью овышения надежности устройства, но содержит регистр адреса откаов, вход которого подключен к выхоу блока контроля, первый выход - ко ходу счетчика разрядов, а второй ыход - ко входам коммутаторов. Источники информации ринятые во внимание при экспертизе 1. Авторское свидетельство СССР. , кл. G П С 29/00, 1978 прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1980 |

|

SU888214A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU911627A2 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU963109A2 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1152044A2 |

| Запоминающее устройство с самоконтролем | 1978 |

|

SU748515A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1133623A2 |

| Резервное запоминающее устройство | 1976 |

|

SU604036A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1399823A1 |

| Ассоциативное запоминающее устройство | 1979 |

|

SU826421A1 |

| Запоминающее устройство с автономнымКОНТРОлЕМ | 1979 |

|

SU842977A1 |

I r

Авторы

Даты

1981-11-23—Публикация

1979-04-05—Подача