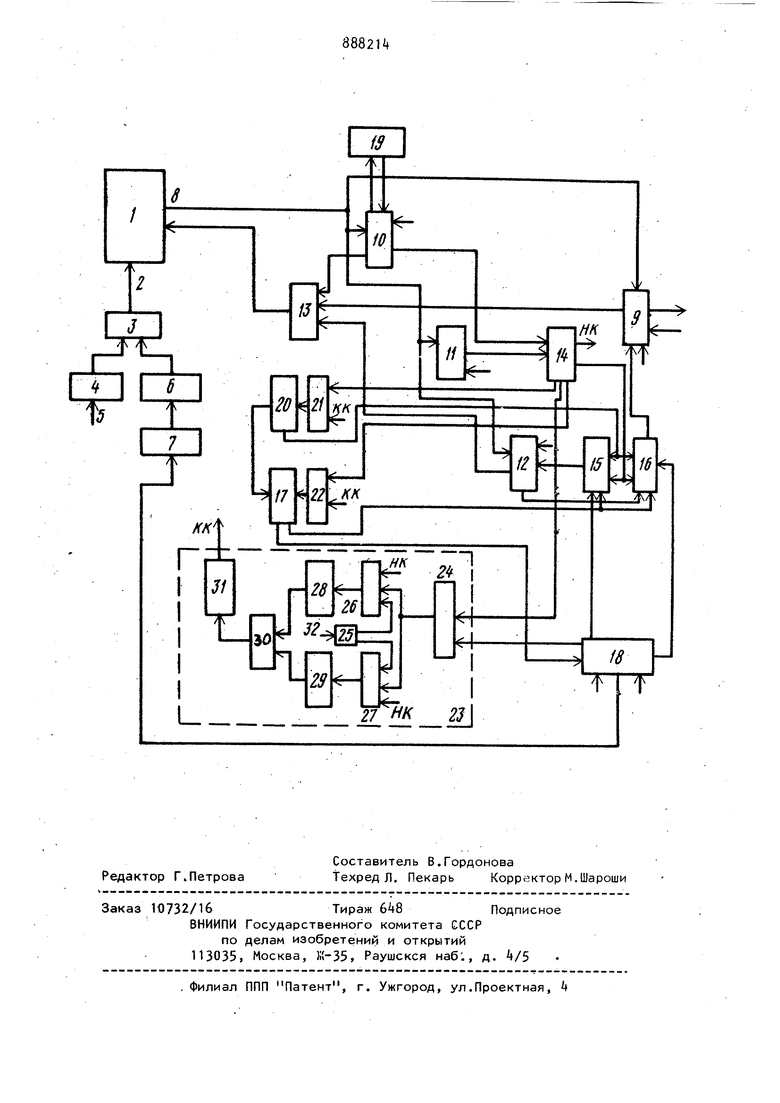

Изобретение относится к вычислительной технике и Может быть применено для изготовления запоминающих устройств. Известно запоминающее устройство с самоконтролем 1, содержащее накопитель, регистры числа, группы элементов ИЛИ, регистры адреса, счетчик адресов, блок контроля, бло управления и блок местного управления. Недостатком известного устройст ва является его узкие функциональн возможности, заключающиеся а том, что в резервных ячейках не должно быть отказавших разрядов. Это накладывает существенные ограничения на организацию обращения к запоминающему устройству, так как ячейки с отказавшими разрядами не могут бы использованы в качестве резервных, и, в конечном счете, снижают надежность устройства. Наиболее близким решением по технической сущности к изобретению является запоминающее устройство с самоконтролем 2, содержащее накопитель, регистры числа, группу элементов ИЛИ, регистрь адреса, счетчик адрбса, блок контроля, коммутаторы, счетчик разрядов, блок управления , блок местного управления и регистр резервных ячеек. Недостатком известного устройства является его невысокая надежность. В случае появления хотя бы одного сбоя при обращении t устройству нарушается последовательность использования разрядов резервных ячеек, что приводит к неправильному формированию данных целого массива. Покажем это на примере. Предположим, что при записи данных в п-ю рабочую ячейку потребовалось разрядами резервной ячейки подменить три отказавших разряда, в (п +.1)-ю - 1 разряд, в (п + 2)-ю - 2 разряда и т.п. Тогда разряды резервной ячейки будут задействованы следующим образом: р t р ,5 Р 6 р 7 р Разряды и-и (п+1)-и (п+2)-и Ячейки В режиме считывания количество от казавших разрядов рабочей ячейки контролируется и результаты контроля используются при обращении к резервной ячейке для подмены отказавших разрядов. Допустим , что при контроле количества отказавших разрядов п-й рабочей ячейки произошел сбой и по результатам контроля оказалось, что в ней не три отказавших разряда, а четыре. Тогда подмена отказавшихся разрядов для п-й и всех последующих рабочих ячеек этого массива будет осуществляться ошибочно; .Запись 1р IP Зр 4-р 5р 6р 7р Чтение АналогичноМОЖ+1О показать существенное влияние сбоев на работоспособ ность устройства и в режиме записи, и при контроле резервных ячеек. Цель изобретения заключается в по аышении надежности устройства. Поставленная цель достигается тем WTO в запоминающее устройство с самоконтролем, содержащее накопитель, адресные входы которого подключены к выходам элементов ИЛИ первой групп информационные эходы - к выходам эл ментов ИЛИ второй группы, а выходы к первым входам первого, второго, третьего и четвертого регистров 4Viсел, блок контроля, первые и вторые входы которого подключены соответст венно к первым выходам второго регистра числа и к выходам третьего р гистра числа, первые выходы блока контроля подключены к первым входам первого и второго коммутаторов, вторые входы которых подключены к первым выходам регистра резервных ячеек, счетчик разрядов, первый вхо которого подключен к второму выходу регистра резервных ячеек, а первый выход - к третьим входам первого и второго коммутаторов, второй выход счетчика разрядов подключен к перво му входу блока управления, первый и второй выходы которого подключены к четвертым входам соответственно первого и второго коммутаторов, выходы первого и второго коммутаторов подключены соответственно к второму входу четвертого регистра числа и к второму входу первого регистра, выходы которого подключены к первым входам элементов ИЛИ второй группы, вторые и третьи входы элементов ИЛИ второй группы подключены соответственно к вторым выходам втрого регистра числа и к первым выходам четвертого регистра числа, вторые выходы которого подключены к пятым входам второго коммутатора, счетчик адреса, вход которого подключен к третьему выходу блока управления, а выходы - к входам второго регистра адреса, выходы второго регистра адреса подключены к первым входам элементов ИЛИ первой группы, вторые входы которых подключены к выходу первого регистра адреса, вторые входы второго и третьего регистров числа подключены к соответствующим выходам блока управления, дополнительно введены элементы И первой и второй групп и блок анализа сбоев, первый вход которого подключен к второму выходу блока контроля, второй вход - к четвертому выходу блока управления, а выход блока анализа сбоев подключен к первым входам элементов И первой и второй групп, первые входы которых подключены соответственно к третьим и к четвертым выходам блока контроля, выходы элементов И первой и второй групп подключены соответственно к входам регистра резервных ячеек и к входам счетчика разрядов. Блок анализа сбоев содержит третий коммутатор, элементы И третьей и четвертой групп, первые входы которых подключены к выходам третьего коммутатора, входы которого являются входами блока анализа сбоев, триггер, первый и второй выходы которого подключены к вторым входам элементов И соответственно первой и второй групп, первый и второй регистры сбоев, входы которых подключены к выходам элементов И соответственно первой и второй групп, схему сравнения, первый и второй входы которой подключены к выходам соответственно первого и второго регистров сбоев, и счетчик циклов, вход которого подключен к выходу схемы сравнения, выход счетчика циклов является выходом блока анализа сбоев. На чертеже представлена структурная схема предлагаемого устройства. Устройство содержит накопитель 1 имеющий адресные входы 2, первую группу элементов ИЛИ 3, первый регистр адреса, имеющий вход 5, вто рой регистр 6 адреса, счетчик 7 адр сов, выходы 8 накопителя 1, к которы подключены одни из входов первого ре гистра 9 числа, второго регистра 10 числа, третьего регистра 11 числа 5 и один из входов четвертого регистра 12 числа, вторую группу элементов ИЛИ 13, блок И контроля, первый И и второй 16 коммутаторы, счетчик 17 разрядов блок 18 управления, блок 19 местного управления, регистр 20 резервных ячеек, первую 21 и вторую 22 группы элементов И и блок 23 анализа сбоев. Блок 23 состоит из третьего коммутатора 24, триггера 25, третьей 26 и четвертой 27 групп элементов И, первого 28 и второго 29 регистров сбоев, схемы 30 сравнения и счетчика 31 циклов. Устройство работает следующим образом. В исходном состоянии счетчик 17 обнулен, триггер 25-е О состоянии. Для каждого линейного участка программы или для массива чисел, которые будут записываться или считываться последовательно, выделяются резервные ячейки накопителя 1.8 сче чик 7 при этом записывается адрес пе вой резервной ячейки, а на вход 5 регистра поступает адрес первой яч ки записываемого или считываемого массива чисел. При записи информации сначала осу ществляется контроль исправности раз рядов резервной ячейки. Адрес резерв ной ячейки из счетчика 7 передается через регистр 6 на входы 2 накопителя 1. Производится чтение содержимог резервной ячейки на регистр 10, затем осуществляется запись - считывание обратного кода содержимого резервной ячейки на регистр 11. Содержимое регистров 10 и 11 подается на блок Ik. В случае, если отказавших разрядов в ячейке нет, то регистр 20 и счетчик 17 остаются в О состояни При наличии отказавших разрядов блок Т вырабатывает сигнал НК (На.чало контроля), подготавливая к работе блок анализа сбоев, для проведения проверки характера отказов неисправных разрядов (устойчивый отказ или неустойчивый отказ, т.е. сбой) . Через коммутатор 2k, группу элементов И 26 (так как триггер 25 в О) в разряды регистра 28, соответствующие отказавшим разрядам, записываются Ч,в триггер 25 по сигналу 32 с блока И переводится в 1 состояние. Далее осуществляется повторный контроль исправности резервной ячейки, т.е. производится чтение содержимого резервной ячейки на регистр 10, затем осуществляется запись-считывание обратного кода этой ячейки на регистр 11, Содержимое регистров 10 и 11 подается на блок I, и в разряды регистра 29 (так как триггер 25 в 1), соответствующие отказавшим разрядам, записываются 1, триггер 23 устанавливается сигналом 32 с блока k в О. Содержимое регистров 28 и 29 поступает на схему 30, при совпадении к содержимому счетчику 31 прибавляется 1, если переполнения счетчика нет, то данный процесс повторяется. В счетчик 31 предварительно записывается обратный код количества необходимых повторений , которое определяется конкретно в каждом случае в зависимости от предъявляемых требований к быстродействию устройства. При переполнении счетчика 31 блок 1 вырабатывает сигнал КК (Конец контроля) и через группы элементов И 21 и 22 в соответствующие. разряды регистра 20 записываются 1, в счетчик 17 записывается количество отказавших разрядов, а в маркерный . разряд резервной ячейки накопителязаписываетс 1. Таким образом, на этапе контроля неисправности разрядов резервных ячеек возникающие сбои не оказывают влияния на правильность определения неисправных разрядов. Далее осуществялется запись массива чисел. Первое число поступает в регистр 9, и содержимое регистра k через элементы ИЛИ 3 подается на вход накопителя 1.. Обратный код из регистра 9 через элеенты ИЛИ 13 записывается в рабочую чейку накопителя 1, затем содержимое чейки считывается на регистр 11, и существляется запись-считывание рямого кода числа на регистр 10. сли блок Н не обнаружил в рабочей чейке отказавшие разряды, то .в реистр 4 поступает следующий адрес и налогично производится запись второо числа. Если же в ячейке есть отка7завшие разряды, то блок 14 запускае блок 23 и начинается определение отказавших разрядов рабочей ячейки (аналогично тому, как это делалось для резервной ячейки). Естественно, что при этом возможные сбои не буду оказывать влияния на правильность определения отказавших разрядов. За .блок k, счетчик 17 и регистр 20 выд ют на коммутатор 15 сигналы, по которым из регистра 9 в младшие разря ды регистра 12 передаются разряды числа, соответствующие отказавшим разрядам рабочей ячейки, причем в разряды регистра 12, соответствующие 1 регистра 20 (т.е. отказавшим разрядам резервной ячейки)запис не производится,они пропускаются и не используются. Затем с блока I в счетчик 17 через элементы И 22 за писывается код, соответствующий количеству отказавших разрядов ячейки. Из блока 18 в блок 19 поступает сигнал, по которому в маркерный раз ряд рабочей ячейки накопителя 1 через регистр 10 записывается 1. Аналогично производится запись числа во вторую рабочую ячейку, имеющу отказавшие разряды. Только соответс вукицие отказавшим разряды регистра записываются в следующие младшие не занятые разряды регистра 12 (с пропуском разрядов, соответствующих отказавшим разрядам резервной ячейк После того, как все разряды регистра 12 будут заполнены, счетчик разрядов выдает сигнал заполнения в блок 18. Адрес резервной ячейки из счетчика 7 поступает на регистр 6 и через элементы ИЛИ 3 на вход 2 на копителя 1. Содержимое регистра 12 через элементы ИЛИ 13 записывается в первую резервную ячейку массива чисел.После этого по сигналу из блока 18 в счетчике.7 формируется адрес следующей резервной ячейки, и весь процесс повторяется. Чтение информации производится следующим образом, В регистр подается адрес первой ячейки считываемого массива чисел, а в счетчик 7 записывается адрес первой резервной ячейки массива чисел. Счетчик 17 пр этом находится в нулевом состоянии. По сигналу из блока 18 производится передача содержимого счетчика 7 через регистр 6 и элементы ИЛИ 3 на вход накопителя 1. Производится чте ние числа из резервной ячейки на ре ,8 гистры 12 и 10. Если в маркерном разн ряде резервной ячейки код 1, то осуществляется запись-чтение обратного кода на регистр 11. Содержимое регистров 10 (4 11 подается на блок }k, По сигналу блока И блок 23 уже рассмотренным порядком обеспечивает правильное определение отказавших разрядов резервной ячейки независимо от появления сбоев. По сигналу КК от блока 23 через группы элементов И 21 и 22 записываются 1 в разряды регистра 20, соответствующие отказавшим разрядам резервной ячейки, а в счетчик 17 записывается количество этих разрядов. Если в маркерном разряде код О, то счетчик 17 и разряды регистра 20 остаются в О состоянии. Затем из регистра 6 поступает адрес первой рабочей ячейки считываемого массива числа и производится чтение на регистры 9 и 10. Если в маркерном разряде код О, то, следовательно, в ячейке не было отказавших разрядов и число из регистра 9 поступает на выход. Если же в маркерном разряде код 1, то производится запись-чтение обратного кода числа на регистр 11. Содержимое регистров 10 и 11 подается на блок Н, вновь запускается блок 23 сигналом НК и в известном уже порядке формируется сигнал КК. По сигналам блока 1 при наличии сигнала КК регистр 20, счетчик 17 через коммутатор 16 обеспечивает передачу необходимых младших раарядов регистра 12 в регистр 9, причем разряды регистра 12, соответствующие взведенным разрядам регистра 20, пропускаются. Отказавшие разряды рабочей ячейки, таким образом, подменяются разрядами резервной ячейки. Число из регистра 9 поступает на выход.. В счетчик 17 записывается код, соответствующий количеству использованных разрядов регистра 12. Если все разряды регистра 12 будут использова.ны, на что указывает соответствующее состояние счетчика 17, то по сигналу из блока 18 счетчиком 7 формируется адрес следующей резервной ячейки. Содержимое резервной ячейки считывается на регистр 12 и аналогично продолжается считывание массива чисел с подменой .отказавших разрядов. В изобретении необходимым количеством повторений чтения-записи данных в ячейку накопителя исклю, V.- , 9 , чаётай вЬа ейстаие сбоев на правиль ность ра змещенйя йанйых в рабочей и резервнойячейках, и повышается- надежность ycTpofric.TBa. Формула изобретения 1 .Запоминающее устройство с самоконтролем, содержащее накопитель, адресные входы которого подключены к выходам элементов ИЛИ первой груп пы, информационные входы - к выхода элементов ИЛИ второй группы, а выхо ды - к первым входам первого, вторс третьего и четвертого регистров чисел, блок контроля, первые и вторые входы которого подключены соответст венно к первым выходам второго регис ра числа, первые выходы блока контроля подключены к первым входам пер вого и второго коммутаторов, вторые входы, которых подключены к первым выходам регистра резервных ячеек, счетчик разрядов, первый вход котор го подключен к второму выходу регис ра резервных ячеек, а первый выход к третьим входам первого и второго коммутаторов, второй выход счетчика разрядов подключен к первому входу блока управления, первый и второй выходы которого подключены к четвертым входам соответственно первого и второго коммутаторов, выходы первого и второго коммутаторов подключе ны соответственно к второму входу четвертого регистра числа и к второму входу первого регистра, выходы которого подключены к первым, входам элементов ИЛИ второй группы, вторые и третьи входы элементов ИЛИ второй группы подключены соответственно к вторым выходам второго регистра числа и к первым выходам четвертого регистра числа, вторые выходы которого подключены к пятым входам второго коммутатора, счетчик адреса, вход ко торого подключен к третьему выходу блока управления, а выходы - к входа второго регистра адреса, выхо/з1ы второго регистра адреса подключены к первым входам элементов ИЛИ первой 10 группы, вторые входы которых подключены к выходу первого регистра адреса, вторые входы второго и третьего регистров числа подключены к соответствующим выходам блока управления, отличающееся тем, что, с целью повышения надежности устрой ства, в него введены элементы И первой и второй групп и блок анализа сбоев, первый вход которого поди.ючен к второму выходу блока контроля, второй вход - к четвертому выходу блока управления, а выход блока анализа сбоев подключен к первым входам элементов И первой и второй групп, первые входы которых подключены соответственно к третьим и к четвертым выходам блока контроля, выходы элементов И первой и второй групп подключены соответственно к входам регистра резервных ячеек и к входам счетчика разрядов. 2. Устройство по п. 1, отличающееся тем, что блок анализа сбоев содержит третий коммутатор, элементы И третьей и четвертой групп, первые входы которых подключены к выходам третьего коммутатора, входы которого являются входами блока анализа сбоев, триггер, первый и второй выходы которого подключены к вторым входам элементов И соответственно первой и второй групп, первый и второй регистры сбоев, входы которых подключены к выходам элементов И соответственно первой и второй групп, схему сравнения, первый и второй входы которой подключены к выходам соответственно первого и второго регистров сбоев, и счетчик циклЪв, вход которого подключен к выходу схемы сравнения, выход счетчика циклов является выходом блока анализа сбоев. Источники инс;юрмации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР по зйявке № 2631178/18-2+, кл. G 11 С 29/00, 1978. 2. Авторское свидетельство СССР о заявке № 284б+А5/18-24, л, G 11 С 29/00, 1979 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1981 |

|

SU963109A2 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1152044A2 |

| Запоминающее устройство с самоконтролем | 1978 |

|

SU748515A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU911627A2 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1133623A2 |

| Запоминающее устройство с самоконтролем | 1979 |

|

SU883975A2 |

| Резервное запоминающее устройство | 1976 |

|

SU604036A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU920849A2 |

| Устройство для записи информации в запоминающее устройство | 1980 |

|

SU951399A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1805503A1 |

Авторы

Даты

1981-12-07—Публикация

1980-03-24—Подача