Изобретение относится к вычисяитепь- ной технике и предназначено, например, дпя электронной цифровой вычислительной системы, выпогшенной на функциональных узиах с большой степенью интеграции.

Известны резервированные запомина1о. шие устройства (ЗУ), используемые в электронных цифровых вычислительных системах для надежного хранения информа ции при наличии отказавших ячеек ijH 2J, в которых повышение надежности обеспечивается применением значитеппьного количества аппаратных средств.

Наиболее близким по технической сущности является ЗУ Sj, содержащее основные и резервные блоки памяти соедйнен ные с одним из выходов регистра адреса, другие выходы которого подключены к резервному блоку памяти и через дешифратор - к входам выборки основных бпо- ков памяти, соединенных с соответствуюшими блоками контроля и через первую группу элементов ИЛИ и регистр слова - с первыми входами блока поразрядного контроля, а через вторую группу элементов ИЛИ - со вторыми входами блока поразрядного контроля, выходы которого через элементы И подключены к одним из входов основных блоков памяти, другие Bxofu.1 которых подсоединечы к выходам регистра слова, входы которого через 6hOK коррекции ошибок и непосредственно подключены к выходу блока обнаружения ошибок, входьг которого через третью группу элементов ИЛИ подключены к вы- ходам основных блоков памяти.

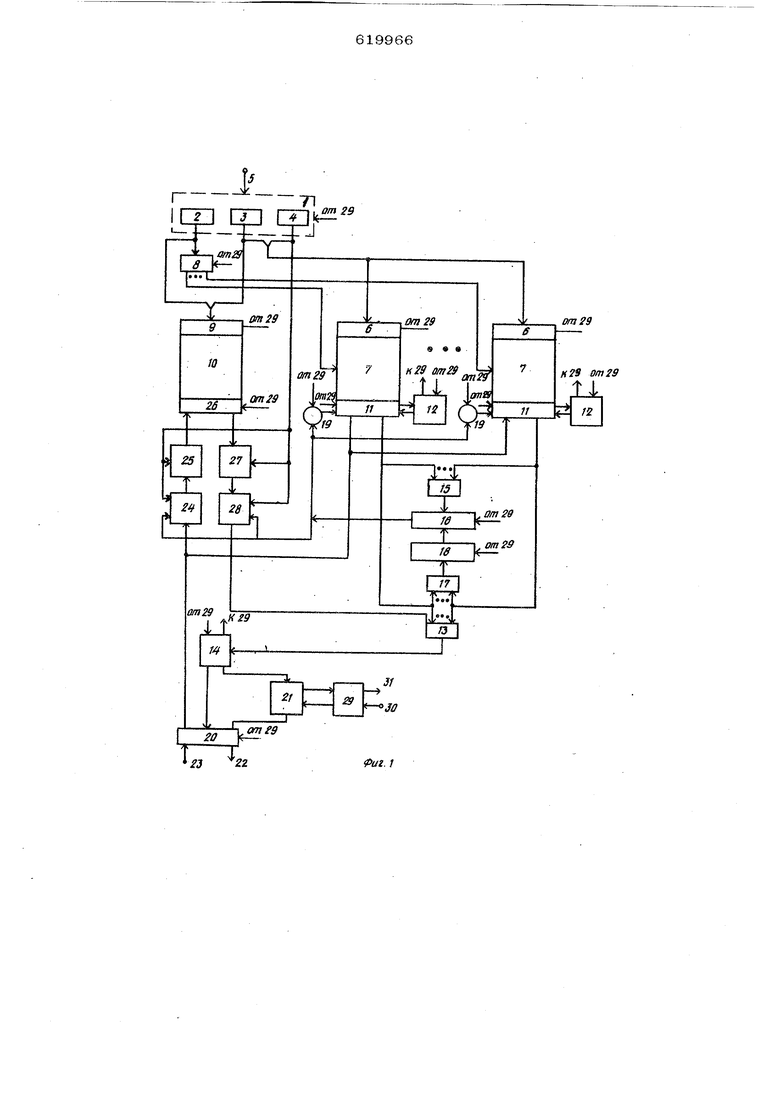

В этом ЗУ для обеспечения наяененой работы при наличии отказавших ячеек основного блока памяти используются ячейки резервного блока памяти. Однако, для резервирования одной ячейки основного блока памяти необходима одна ячейка резервного блока памяти. Замена при отказе .основной ячейки только отказавших разрядов на разряды резервной ячейки, а не всей основной ячейки на резервную ячейку, позволит использовать одну резервную ячейку для нескольких основных ячеек,,в результате чего значительно унизится ыеобходвмое количество резервных анеек дня ЗУ в цепом. Цепью изобретения является упрощени устройства. Поставленная цепь достигается тем, что резервирставное ЗУ содержит блоки выделения разрядов и блоки сдвига, при чем первые входы одного блока сдвига соединены с выходами регистра слова, вторые - с выходами блока поразрядного контроля, третьи - с выходами регистра адреса, а выходы- с первыми входами блока выделения разрядов, вторые входы которого подключены к выходам регистра адреса, а выходы к резервному бло ку памяти, выходы которого подключены к первым входам другого блока выделения разрядов, вторые входы которого соединены с выходами регистра адреса, а выходы - с первыми входами блока сдвига, вторые входы которого подключены к выходам регистра адреса, третьи к выходам блока поразрядного контроля, а выходь - к дополнительным выходам третьей группы элементов ИЛИ. На фиг. 1 изображена блок-схема предлагаемого резервированного ЗУ, содер жащего, например, четыре основных блока памяти: на фиг. 2 показаны примеры, иллюстрирующие работу резервированного ЗУ. ЗУ содержит регистр адреса 1, состоящий из регистра 2 номера блока паМя . ти, регистра старших разрядов 3 и реги ра л;л5адших разрядов 4, Регистр 1 имее информационный вход 5, Регистры 3 и 4 подключены к регистрам агфеба 6 ооновных блоков памяти 7. Регистр 2 через дешифратор 8 подключен к основным блокам памяти 7. Регистры 3 и 2 «вязаны с регистром афеса 9 резервно го блока памяти 1О. Прёдооложим что ейкость блока памяти 7 или 10 равна 16 восьмиразрядных информационных слов. Далее допустим, что в ячейках блока памяти 7 возможны, например, двукратные отказы. Следовательно, не- обходимо резервировать два разряда для каждой ячейки всех блоков памяти 7. Очевидно, что в данном примере для резервировения четырех блоков памяти 7 ьпиеуказанной емкости достаточно использовать один блок памяти 10 такой же емкости. В первых четырех ячейках блока памяти 1О бупут находиться все резервные разряды первого блока памяти 7 {считая с лева), во вторых четьфех ячейках блока памяти Ю - все резервные раз;ряды. ДЛЯ второго блока памяти 7 и г. п Регистры слова 11 блоков памяти 7 соединены с соответствующими блоками контроля 12. Выходы регистров 11 через группу элементов ИЛИ 13 подключены к блоку обнаружения ошибок 14, через группу элементов ИЛИ 15 -к одним входам блока поразрядного контроля - 16, а через группу элементов ИЛИ - 17 - к регистру слова 18. Регистр 18 связан с щзугими входами блока 16. Выходы блока 16 подключены через соответствующие элементы И 19 к регистрам 11. Блок 14 связан со входами регистра слова 2О непосредственно и через блок коррекции ошибок 21. Регистр 20 имеет информационные выходь 22 и входы 23. Выходы регистра 2 О под:5лючены к регист рам 11. Выходы регистра 20 соединены через блок сдаига 24 и блок выделения разрядов 25 со входами регистра слова 26 резервного блока памяти lO. Выходы регистра 26 связаны через блок выделения разрядов 27 и блок сдвига 28 с группой элементов ИЛИ 13. Со входами блоков выделения разрядов 25 и 27 соединены регистра 4, а со входам блоков сдвига 24 и 28 связаны выходы регистра 4 и выходы блока 16. Блок местного управления 29, который имеет вход 30, и выход 31, подключен к регистру 1, к регистрам 6, к дешифратору 8, к регистрам 9, 11, к блокам 12, к блоку 14, к блоку 16, к регистру 18, к элементам И 19, к блоку 21 и к регистрам 20 и 26. Предлагаемое резервированное ЗУ работает следующим образом. По входу 5 поступает адрес ячейки, который записьгоается в регистр 1, причем номер блока памяти 7 записьтается в регистр 2, старшие разряды апрвса в регистр 3, а младшие разряды ащзеса в регистр 4. По содержимому регистра 4 через дешифратор 8 выбирается блок памяти 7, к которому будет происходить обращение. В дальнейшем будем предполагать, что обращение в данном случае производится к первому блоку памяти 7 (считая слева) Принцип работы одинаков для обращения к любому из блоков памяти 7. Итак, при обращении к блоку памяти 7 содержимое регистров 3 и 4 поступает на регистр 6 блока памяти 7, а содержимое регистров 2 и 3 поступает на регистр 9. Необходимо различать следующие возможные ситуации, возникак ,щие при обращении к блоку памяти 7. -запись слова в исправную ячейку, аапись слова в отказавшую ячейку, «чтение слова из исправной ячейки, -чтение слова из отказавшей ячейки, При считьтании слова из ячейки блока памяти 7 блок 12 анализирует специальный индикаторный разряд.(или группу разрядов), указьгеающий на отсутствие или наличие отказов в ячейке, и выдает соответствующий сигнал в блок 29, При записи слова в ячейку блока памяти 7 установка указанного разряда, например в О при отсутствии отказов и в 1 при наличии oткaзoв производит ся соответствующим блоком 12. Перед записью слова в ячейку необходимо произвести считывание ее содержимого для определения того, является ли ячейка отказавшей или исправной. Запись слова в исправную ячейку. Блок 12 определяет по индикаторному разряду предварительно считанного содер жимого ячейки, что ячейка исправна. При этом слово с регистра 2О поступае в регистр 11 блока памяти 7 и записывается в ггчейку по адресу, содержащему ся в регистре 6. Запись слова в отказавшую ячейку. Блок определяет по индикаторному разряду предварительно считанного содер жимого 5гчейки, что ячейка отказала. При этом прямой код слова, считанного на регистр 11, передается через группу элементов ИЛИ 17 на регистр 18, а обратный код его записывается в ту же «гчейку блока памяти 7 и считьтается на тот же регистр 11. Следующим шагом является выдача слов из регистра 18 и из регистра 11 через группу элементов ИЛИ 15 в блок 16. Блок 16 по совпадению прямого и обратного кодов одноименных разрядов определяет отказавшие разряды,разрешает выдачу из регистра 2О в регистр 11 только тех разрядов,; слова, которые соответствуют исправным разрядам ячейки блока памяти 7. Разряд регистра 2О, которые соответствуют отказавшим разрядам ячейки блока памя ти 7, по сигналам из блока 16 и по сиг налам из регистра 4 передаются через блок 24 в блок 25. Блок 25 по сигналам из регистра 4 записьгеает эти разряды на нужную позицию в регистре 26, т. е. в те разряды, которые являют ся резервными для данной ячейки блока памяти 7. После этого производится запись слова из регистра 11 в ячейку блока памяти 7 по адресу, записанному в регистре 6, и запись слова из регистра 26 в ячейку блока памяти 1О по адресу, записанному в регистре 9. Чтение слова из исправной ячейки, На выходе блока 12 присутствует сигнал о Считанное на регистр 11 слово записьгаается через группу элементов ИЛИ 13 в блок 14. Сигнал ошибки на выходе блока 14 отсутствует, и слово передается в регистр 20. Чтение слова из отказавшей ячейки. При этом возможно даа сяучая: а.Резервные разряды данной ячейки еще не использованы, так как отказ в этой ячейке до сих пор не был обнаружен. На выходе блока 12 присутствует сигнал О. б.Резервные разряды данной ячейки уже использованы, так как отказ в этой ячейке был обнаружен при чтении, происшедшем ранее. На выходе блока 12 при- сутстЪует сигнал , В первом случае чтение производится следующим образом. Слово, считанное из ячейки блока памяти 7 на регистр 11, передается через группу элементов ИЛИ 13 в блок 14, На выходе блока 14 появляеЛя сигнал ошибки. Слово передается в регистр 20 через блок 21, который исправляет обнаруженные ошибки. В регистре 20 после этого будет находиться исправленное слово. Далее исправленное слово восстанавливается в ячейке блока памзати 7 аналогично вьпнерассмотренно- му процессу записи в отказувшую ячейку. Во втором случае чтение осущаствляеч ся в следующем порядке . Слове, считанное из ячейки блока памяти 7 на регистр 11, передается в прямом коде через группу элементов ИЛИ 17 на регистр 18. Обратный код слова из регистра 11 записьтается в ту же ячейку блока памяти 7 с последующим считьгеанием на этот же регистр. Следующим шагом является выдача слов из регистра 11 через группу элементов ИЛИ 15 и из регистра 18 в блок 16. Блок 16 по совпадению прямого и обратного кодов одноименных разрядов определяет отказавшие разряды и разрешает .выдачу в обратном коде из регистра 11 через группу элементов ИЛИ 13 и блок 14 в регистр 20 только тех разрядов слова, которые соответствуют исправным разрядам ячейки блока памяти 7, Выдача отказавших разрядов из регистра 11 блокируется. Слово, считанное из ячейки блока,памяти 10 на регистр 26, поступает в блок 27. Блок 27 по сигналам из регистра 4 передает в блок 28 те разряды, которые являются резервными для данной ячейки блока па- MSTH 7, из которой производктси чт-ение Бпок 28 по сигналам яз регистра 4 и ,из блока 16 выдает резервные разряды через группу элементов ИЛИ 13 вместо отказавших разрядов ячейки блока пам ти 7, В результате в блок 14 и далее в оегистр 2О поступает исправное слово Работу резервированного ЗУ можно иллюстрировать примерами, представлен ными на фиг. 2а, б. Запись слова в отказавшую ячейку, Пусть в ячейку ОО10 первого блока памяти 7 необходимо записать слово 11 ОО 11 01, которое находится в ре- гистре 20. Для этого по входу 5 по ступает адрес ОО 00 10, т. 6. в регист 2записывается число ОО, в регистр 3 ОО, а в регистр 4 « 10. В реауль тате в первом блоке памяти 7 будет тано содержимое ячейки О01О на регист 26. На выхода блока 12 появляется сиг нал , который свияетепьствует о на пичии отказов в ячейке О010 первого блока памяти 7. Предположим (см. фиг.2 что в ячейке 0010 первого блока памяти 7 находится слово ООН 00 00. (отказавшие разряды подчеркнуты), а .в соответствующей резервной ячейке ОООО блока памяти 1О находится слово ХХХХ1ОХХ (резервные разряды, не от носящиеся к рассматриваемой ячейке пер вого блока памяти 7, отмечены, крестиками). Таким o6pa3OMs после чтения на регистре 11 будет находиться слово ОО 11 QO 00, а°на ре гистре 26. ХЯХХЮХХ. Далее прямой, код слова, считанного на регистр 11, передается в регистр 18, а обратный код еЬо за- письгоается в ту же ячейку первого бло ка памяти 7 и затем считьгоается на регистр 11„ В результате на регистре Ч1 будет находиться слово 11 00 11 00, а в регистре 18 - слово ОО 11 ОО О О. Как видно, слова, содержащиеся в регистрах 11 и 18, совпадают в первых даух разрядах (считая справа), т. е. имеет место отказ в этих разрядах ячейки 0010 первого блока памяти 7. Это обстоятельство выявляется блоком 16, по сигналам которого все разряды регистра 20, кроме первых двух, поступают в регистр 11, в результате на регистре 11 будет находиться слово 11 00 11 00, Из регистра 2О на вход блока 24 поступает слово 11 ОО 11 О1, а на вы ходе блока 24 по сигналам из блока 16 и регистра 4 появляется сдвинутое слов 00 11 01.,, которое послеблока 25 принимает вид.... 01 ... (точками отме чены невыдав&емые разряды). Попучен-. ное слово поступает в регистр 26, в результате на регистре 26 будет находиться слово ХХХХ01ХХ Далее, слово из регис ра 11 НООНОО записьтается в ячейку 00 Ю первого блока памяти 7 и слово из регистра 26 ХХХХ01ХХ записьгаается в ячейку ОООО блока памяти 10 (См. фиг. 26). Чтение слова из отказавшей ячейки. Пусть из ячейки ОО10 (см, фиг,2) первого блока памяти 7 необходимо считать слово, содержащееся в ней. Для этого по входу 5 поступает адрес ОО 0010, т. е. в регистр 2 записываются число ОО в регистр 3 - ОО, а в регистр 4 - 10. В результате в первом блоке памяти 7 будет считано содержимое ячейки OOlp на регистр 11, а в блоке памяти 10 будет считано содержимой ячейкщ ОООО на регистр 26. На входе блока 12 появзгяется сигнап I, который свидетельств вует о наличии отказов в ячейке 0010 первого блока памяти 7. Таким образом, после чтения на регистре 11 будет на- ходиться слово НООНОО.а на регистре 26 ХХХХ01Х|( (см. фиг. 2, б). Далее прямой код слойа, .считанного на регистр 11, передаетдя в регистр 18, а обратный код его записывается в ту же ячейку первого блока памяти 7 и затем счи тывается на регистр 11. В результате в регистре 11 будет находиться слово 001000, а в регистре 18 слово llOOllOO. Как видно, слова, содержащиеся в регистрах 11 и 18, совпадают в первых двух разрядах (считая справа), т. е. имеет место отказ в этих же разрядах ячейки 0010 первого блока памя ти 7. Это обстоятельство выявляется блоком 16, по сигналам которого всё разряды регистра 11, кроме первых двух, в обратном коде поступают в регистр 20, в результате на регистр 20 поступает слово 110011... Спово ХХХХ01ХХ, находящееся на регистре 26, поступает в блок 27, на выходах которого оно принимает вид ... 01 ... Это слово передается в блок 28, на выходах которого по сигналам из блока 16 и регистра 4 появляется сдвинутое слово Ol, которое записывается в регистр 20. В результате на регистре 20 будет находиться исправное слово 11 ОО 11 О1. Таким образом, предложенное резервированное ЗУ обеспечивает достоверное воспроизведение информации при наличии отказов в ячейках основных блоков памяти, используя для нескольких основных ячеек одну резервную ячейку. Эт намного экономичнее по сравнению с ре зервированием основных ячеек таким же количеством резервных ячеек, так как необходимое число резервных ячеек гфи этом значительно снижается. Формула изобретени Резервированное запоминающее устройство, содержащее основные и резерв ные блоки памяти, соединенные с одним из выходов регистра а {феса, другие выходы которого подключены к резервному блоку памяти и через дещифратор - к входам выборки основных блоков памяти соединенных с соответствующими блоками контроля и через первую группу элементов ИЛИ и регистр слова - с пер выми входами блока поразрядного контроля, а через вторую группу элементов ИЛИ - со вторыми входами блока по разрядного контроля, выходы которого через элементы И подключены к одним из входов основных блоков памяти, пру- гие входы которых подсоединены к выходам регистра слова, входы которого через блок коррекции ошибок и непосредственно подключены к выходу блока обнаружения ошибок, входы которого через третью группу элемен1юв ИЛИ подключены к выходам основных блоков памяти, отличающееся тем, что, с целью упрощения устройства, оно содержит блоки выделения разрядов и блоки сдвига, причем первые входы одного блока сдвига соединены с выходами регистра слова, вторые - с выходами блока поразрядного контроля, третьи с выходами регистра адреса, а выходыс первыми входами блока выделения разрядов, вторые входь которого подключены к выходам регистра адреса, а выходы - крезервному блоку памяти,выходы которого подключены к первым входам другого блока выделения разрядов, вторые , входы которого соединены с выходами регистра адреса, а выходы - с первыми входами блока сдвига, вторые входы которого подключены к выходам регистра адреса, третьи - к выходам блока поразрядного контроля, а выходы - к дополнительным входам третьей группы элементов ИЛИ. Источники информации, принятые во внимание при экспертизе; 1.Патент США №3742459, кл, Q 06 Р 11/ОО,- 1973. 2.Авторское свидетельство СССР №385319, кл. Q 11 С 29/ОО, 1973. 3.Патент США №3544777, кл. Q 11 С 29/00, 197О.

i

22

от 29

.1

0000

00 а I

0010 00 1 1

о о о о

0001 0010

о о I 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервное запоминающее устройство | 1976 |

|

SU604036A1 |

| Резервированное запоминающее устройство | 1981 |

|

SU1018152A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ДИНАМИЧЕСКИМ РЕЗЕРВИРОВАНИЕМ | 1990 |

|

RU2028677C1 |

| Устройство для управления режимамиОбМЕНА РЕзЕРВиРОВАННОй СиСТЕМы | 1979 |

|

SU849216A1 |

| Резервированное запоминающее устройство | 1978 |

|

SU720539A1 |

| Резервированное запоминающее устройство | 1987 |

|

SU1510012A1 |

| Микропроцессорная система | 1989 |

|

SU1686454A1 |

| ЗАПОМИНАНМЦЕЕ УСТРОЙСТВО С БЛОШРОВКОЙ НЕИСПРАВНЫХ ЯЧЕЕК ПАМЯТИ | 1979 |

|

SU826425A1 |

| Оперативное запоминающее устройство с автономным контролем | 1983 |

|

SU1113855A2 |

| ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ВЫСОКОЙ СТЕПЕНЬЮ ОТКАЗОУСТОЙЧИВОСТИ | 2005 |

|

RU2327236C2 |

f 1 00 1101 1110

1111

1100 1101 1110

П 1 1

Авторы

Даты

1978-08-15—Публикация

1975-11-10—Подача