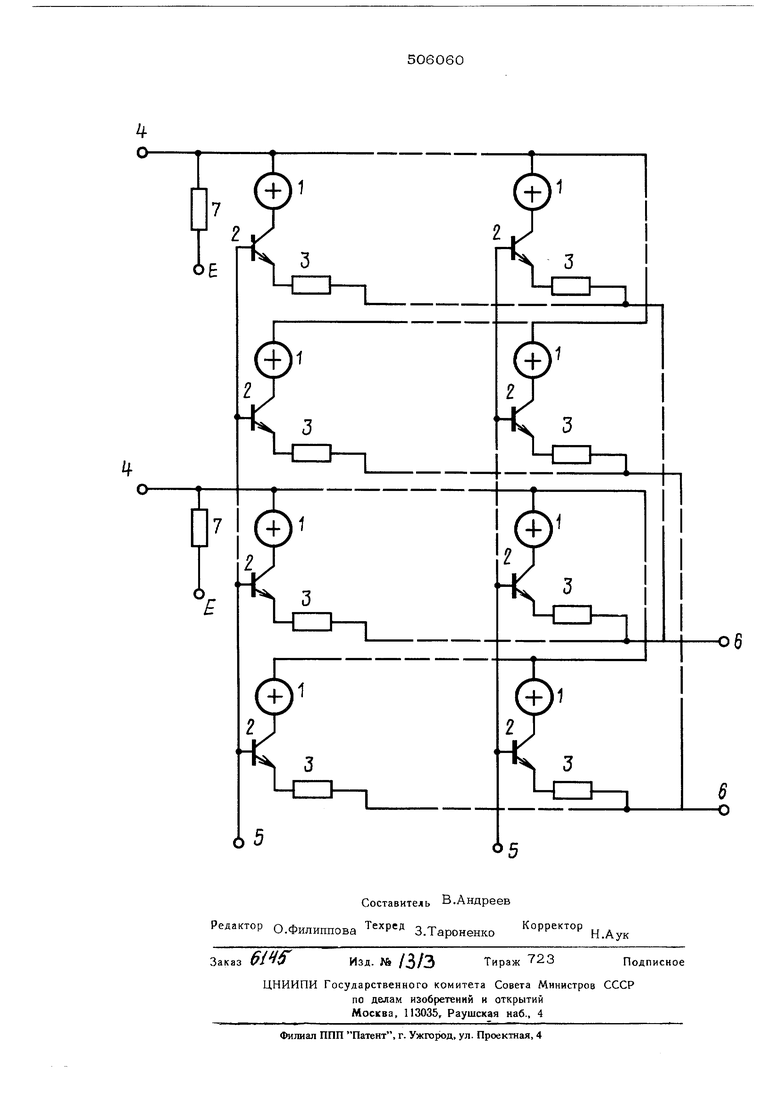

(54) МАТРИЧНЫЙ НАКВПИТЕЛЬ бранной шине X и к невыбранным шинам У, и транзисторы, которые подключены к выбранной шине У и к выбранным шинам X, закрыты, так как напряжение эмиттер-база равно нулю. Остальные транзисторы закры- ты, так как напряжение эмиттер-база больше нуля. При работе с ЗЭ на основе аморфных полупроводников различают три режима: стирание, запись и считывание. Эти три ре жима отличаются длительностью импульсов тока через ЗЭ и их амплитудой. Обнуление ячеек памяти осуществляется в режиме стирания. В предлагаемом накопителе этот режим осуществляется следующим образом. Выбирается число, на разрядные выводы подается импульс напряжения длительностью, соответствующей режиму стирания, на выбран ную шину X (и на невыбранные шины У) подается напряжение, величина которого задает ток стирания. Разделительный элемент $тляется здесь генератором тока для 33 выбранной ячейки памяти. В режиме записи величина напряжения подаваемого на выбранную шину X (и на невыбранные шины У ), задает ток записи. На разрядные шины 4 подается напряжение необходимое для записи в том случае, если в данном разряде записывается 1. Длительность этого импульса напряжения соответствует режиму записи. При записи О напряжение на разрядный вывод не подается и ток через ЗЭ ячейки памяти не течет. При считывании амплитудой напряжения, подаваемого на выбранную шину X (и невыбранную шину У), задается такая амплитуда тока через ЗЭ ячейки памяти, на- ходящейся в состоянии 1, чтобы разделительный транзистор был близок к режиму насыщения. В этом случае напряжение на разрядной шине 4 (в режиме считывания разрядные шины являются выходом матрицы) значительно отличается от напряжения Е за счет протекания тока считывания через резистор 7. Если ячейка памяти хранит О (высокоомное состояние ЗЭ), то разделительный транзистор находится в области насыщения и, в связи со значительным отношением сопротивления ЗЭ в высокоомном состоянии к сопротивлению ЗЭ в низкоомном состоянии, ток через резистор 7 значительно меньше, чем ток при считывании 1, а выходное напряжение близко к Е. Формула изобретения Матричный накопитель, содержащ|ий ячейки памяти, каждая из которых состоит из запоминающего элемента, выполненного на основе аморфного полупроводника, и разделительного элемента, разрядные и адресные щины, резисторы, отличающийся тем, что, с целью улучшения эксплуатационных характеристик и повышения надежности накопителя, в нем разделительный элемент выполнен в виде бипол5фного транзистора, коллектор которого подключен к первому электроду запоминающего элемента, эмиттер через резистор - к первой адресной шине, база - к второй адресной Ешне, второй электрод запоминающего элемента подключен к разрядной щине.

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричный накопитель | 1981 |

|

SU1015440A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МОНОП-ЯЧЕЙКИ ПАМЯТИ, ЯЧЕЙКА ПАМЯТИ И МАТРИЧНЫЙ НАКОПИТЕЛЬ НА ЕЕ ОСНОВЕ | 1996 |

|

RU2105383C1 |

| Полупостоянное запоминающее устройство с электрической перезаписью информации | 1983 |

|

SU1088068A1 |

| МАТРИЧНЫЙ НАКОПИТЕЛЬ ДЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1986 |

|

SU1385872A1 |

| Полупостоянное запоминающее устройство с электрической перезаписью информации | 1976 |

|

SU634373A1 |

| Оперативное запоминающее устройство | 1979 |

|

SU903972A1 |

| Оперативное запоминающее устройство | 1988 |

|

SU1575234A1 |

| Формирователь записи-считывания для запоминающих устройств | 1978 |

|

SU765873A1 |

| Матричный накопитель для постоянного запоминающего устройства | 1990 |

|

SU1756939A1 |

| Способ записи и считывания информации в запоминающих устройствах с инжекционным питанием и устройство для его осуществления | 1975 |

|

SU646371A1 |

Авторы

Даты

1976-03-05—Публикация

1973-07-18—Подача