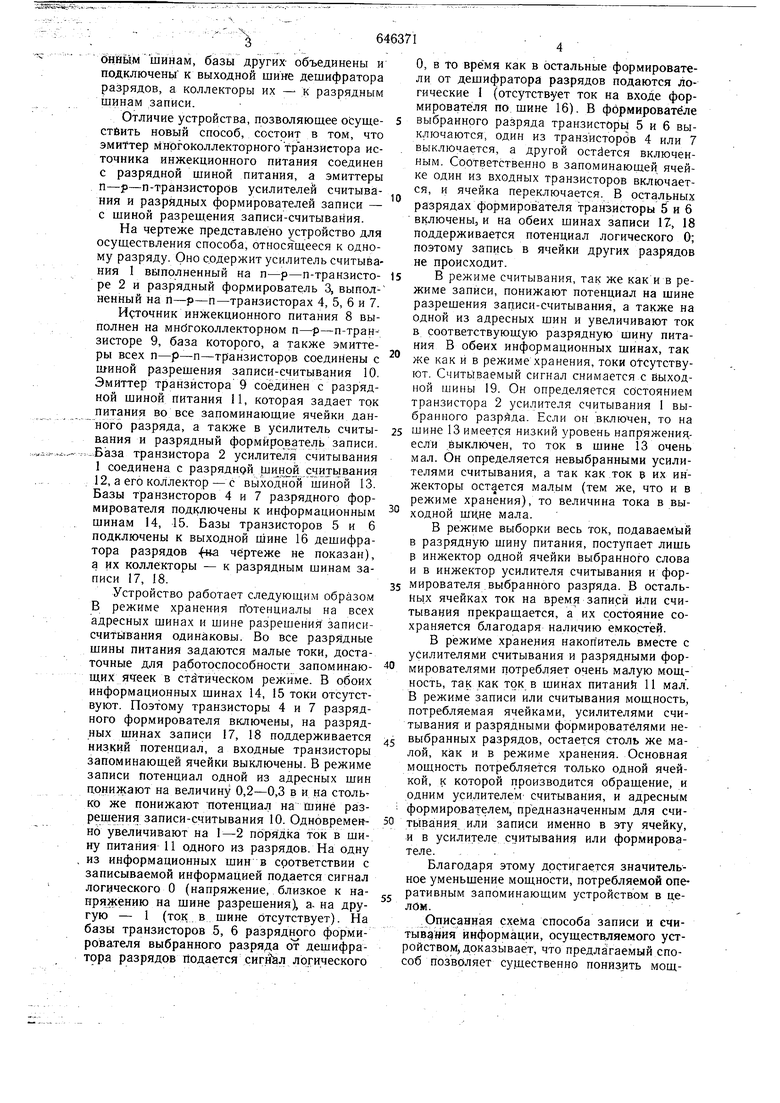

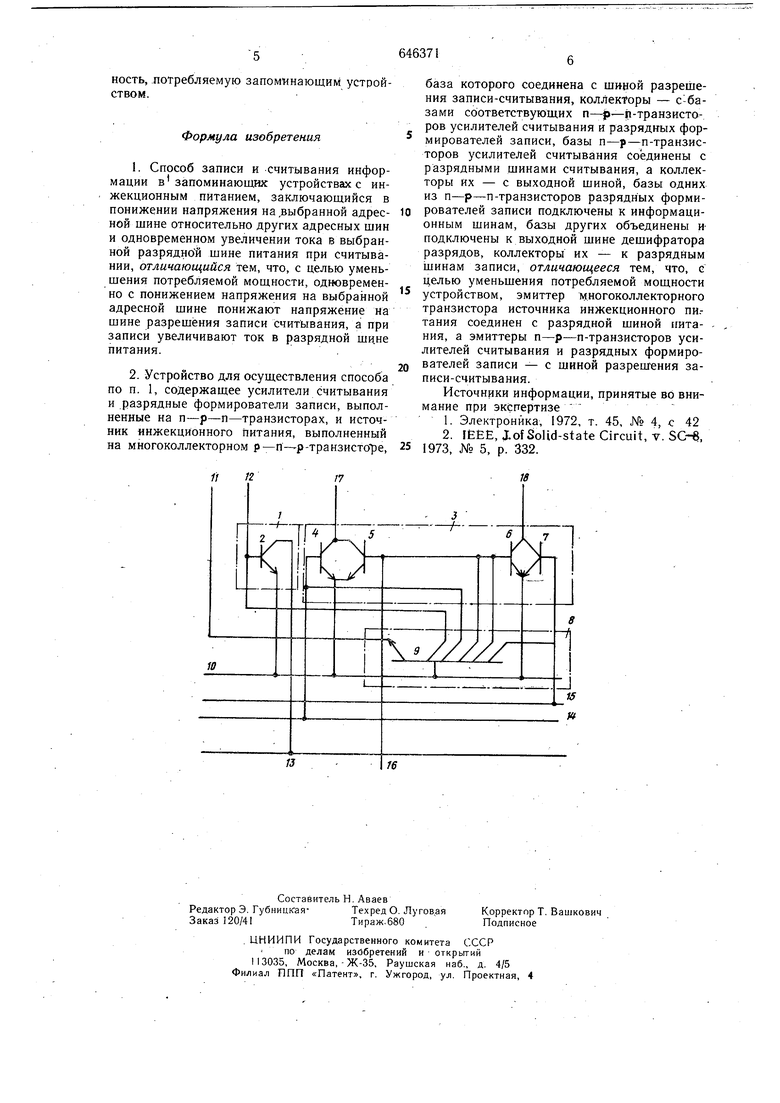

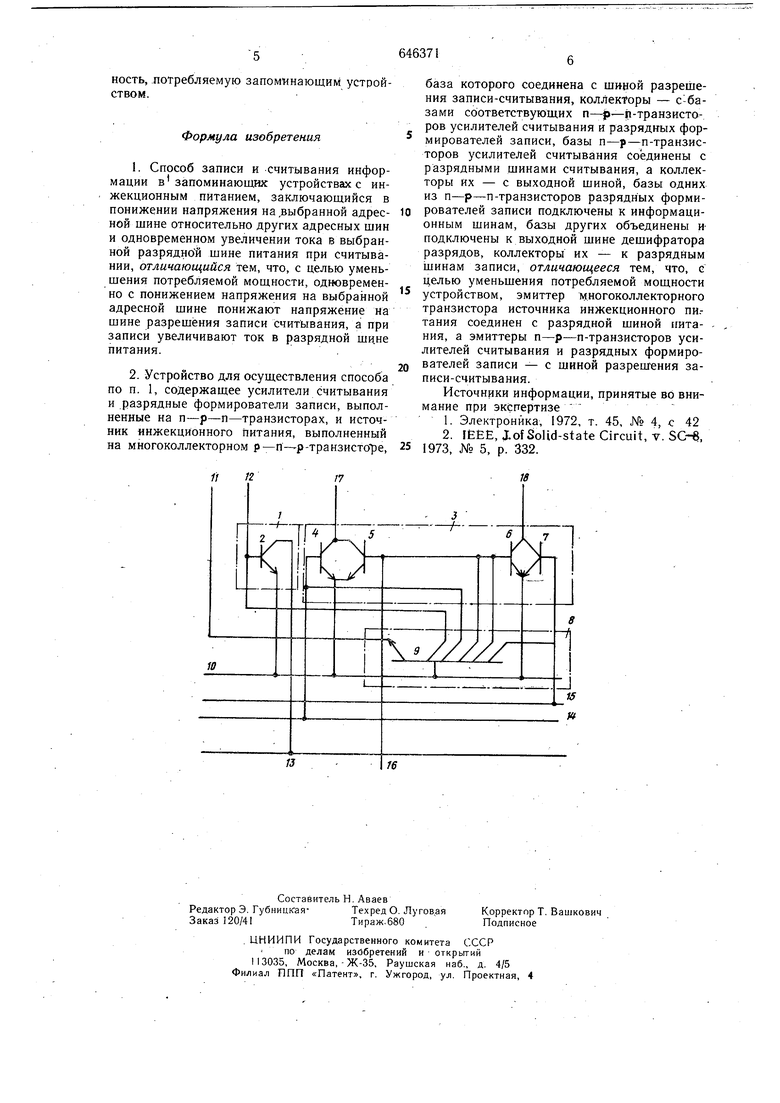

онШм шинам, базы других- объединены и подключены к выходной шине дешифратора разрядов, а коллекторы их - к разрядным шинам записи. Отличие устройства, позволяющее осуществить новый способ, сострит в том, что эмиттер МнргоКоллекторного транзистора источника инжекционного питания соединен с разрядной шиной питания, а эмиттеры п-р-п-транзисторов усилителей считывания и разрядных формирователей записи - с шиной разрещения записи-считывания. На чертеже представлено устройство для осуществления способа, относящееся к одному разряду. Оно содержит усилитель считывания 1 выполненный на п-р-п-транзисторе 2 и разрядный формирователь 3, выполненный на п-р-п-транзисторах 4, 5, 6 и 7. Источник инжекционного питания 8 выполнен на мнбгоколлекторном п-р-п-транзисторе 9, база которого, а также эмиттеры всех п-р-п-транзисторов соединены с Шиной разрешения записи-считывания 10. Эмиттер транзистора 9 соединен с разрядной шиной питания 11, которая задает ток питания во все запоминающие ячейки данного разряда, а также в усилитель считыаания и разрядный формирователь записи. База транзистора 2 усилителя считывания 1 соединена с разрядной Ши ойсчить1вания 12, а его коллектор - с выходной шиной 13. Базы транзисторов 4 и 7 разрядного формирователя подключены к информационным шинам 14, 15. Базы транзисторов 5 и 6 подключены к выходной 16 дешифратора разрядов чертеже не показан), а их коллекторы - к разрядным шинам записи 17, 18. Устройство работает следующим образом В режиме хранения потенциалы на всех адресных щинах и шине разрешения записисчитьшания одинаковы. Во все разрядные шины питания задаются малые токи, достаточные для работоспособности запоминающих ячеек в статическом режиме. В обоих информационных шинах 14, 15 токи отсутствуют. Поэтому транзисторы 4 и 7 разрядного формирователя включены, на разрядных шинах записи 17, 18 поддерживается низкий потенциал, а входные транзисторы запоминающей ячейки выключены. В режиме записи потенциал одной из адресных шин понижают на величину 0,2-0,3 в и на столько же понижают потенциал на шиНё разрещения записи-считывания 10. Одновременно увеличивают на 1-2 порядка ток в шину питания 11 одного из разрядов. На одну , из информационных шин в соответствии с записываемой информацией подается сигнал логического О (напряжение, близкое к напряжению на щине разрешения), а- на другую - 1 (ток. в шине Отсутствует). На базы транзисторов 5, 6 разрядного формирователя выбранного разряда yt дещифратора разрядов подается сигн л логического

646371 О, в то время как в остальные формирователи от дешифратора разрядов подаются логические 1 (отсутствует ток на входе формирователя по шине 16). В формирователе выбранного разряда транзисторь 5 и 6 выключаются, один из транзисторов 4 или 7 выключается, а другой остается включенным. Соответственно в запоминающей ячейке один из входных транзисторов включается, и ячейка переключается. В остальных разрядах формирователя транзисторы 5 и 6 включены, и на обеих шинах записи 17, 18 поддерживается потенциал логического 0; поэтому запись в ячейки других разрядов не происходит. В режиме считывания, так же как и в режиме записи, понижают потенциал на шине разрешения записи-считывания, а также на одной из адресных шин и увеличивают ток в соответствующую разрядную шину питания В обеих информационных шинах, так же как и в режиме хранения, токи otcyTCTByют. Считываемый сигнал снимается с выходной шины 19. Он определяется состоянием транзистора 2 усилителя считывания I выбранного разрйда. Если он включен, то на шине 13 имеется низкий уровень напряжения,если .выключен, то ток в шине 13 очень мал. Он определяется невыбранными усилителями считывания, а так как ток в их инжекторы остается малым (тем же, что и в режиме хранения), то величина тока в выходной шНне мала. В режиме выборки весь ток, подаваемь1Й в разрядную шину питания, поступает лишь в инжектор одной ячейки выбранного слова и в инжектор усилителя считывания и фор.мирователя выбранного разряда. В остальHbix ячейках ток на время записи Или считывания прекрашается, а их состояние сохраняется благодаря наличию емкостей. В режиме хранения накопитель вместе с усилителями считывания и разрядными формирователями потребляет очень малую мощность, так как ток в шинах питаний 11 мал. В режиме записи или считывания мощность, потребляемая ячейками, усилителями считывания и разрядными формирователями невыбранных разрядов, остается столь же малой, как и в режиме хранения. Основная мощность потребляется только одной ячейкой, к которой производится обращение, и одним усилителем считывания, и адресным формирователем, предназначенным для считывания или записи именно в эту ячейку, и в усилителе считывания или формирователе. . . Благодаря этому достигается значительное уменьшение мощности, потребляемой оперативным запоминающим устройством в целОм. Описанная схема способа записи и считывайия информации, осуществляемого устройством, доказывает, что предлагаемый способ позволяет существенно понизить мощность, потребляемую запоминающим устройством.

Формула изобретения

1.Способ записи и считывания информации взапоминающих устройствах с инжекционным питанием, заключающийся в понижении напряжения на .выбранной адресной шине относительно других адресных шин и одновременном увеличении тока в выбранной разрядной щине питания при считывании, отличающийся тем, что, с целью уменьшения потребляемой мощности, одновременно с понижением напряжения на выбранной адресной щине понижают напряжение на щине разрешения записи считывания, а при записи увеличивают ток в разрядной ши.не питания.

2.Устройство для осуществления способа по п. 1, содержащее усилители считывания и разрядные формирователи записи, выполненные на п-р-п-транзисторах, и источник инжекционного питания, выполненный на многоколлекторном р-п-р-транзисторе.

11

13

база которого соединена с шиной разрешения записи-считывания, коллекторы - с-базами соответствующих п-р-п-транзисторов усилителей считывания и разрядных формирователей записи, базы п-р-п-транзисторов усилителей считывания соединены с разрядными шинами считывания, а коллекторы ИХ - с выходной шиной, базы одних из п-р-п-транзисторов разрядных формирователей записи подключены к информационным шинам, базы других объединены иподключены к выходной шине дешифратора разрядов, коллекторы их - к разрядным и1инам записи, отличающееся тем, что, с целью уменьшения потребляемой мощности устройством, эмиттер многоколлекторного транзистора источника инжекционного пи.тания соединен с разрядной шиной питания, а эмиттеры п-р-п-транзисторов усилителей считывания и разрядных формирователей записи с шиной разрещения записи-считывания.

Источники информации, принятые во внимание при экспертизе

1.Электроника, 1972, т. 45, № 4, с 42

2.ГЁЕЕ, Хо Solid-state Circuit, т. SC-в, 1973, № 5, р. 332.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1977 |

|

SU769627A1 |

| Матричное запоминающее устройство | 1977 |

|

SU744724A1 |

| Запоминающее устройство с произвольной выборкой | 1977 |

|

SU769626A1 |

| Запоминающее устройство | 1974 |

|

SU658600A1 |

| Интегральная ячейка памяти | 1977 |

|

SU637867A2 |

| Запоминающее устройство | 1985 |

|

SU1269208A1 |

| Запоминающее устройство | 1976 |

|

SU597006A1 |

| Ячейка памяти | 1974 |

|

SU491998A1 |

| Ячейка памяти | 1973 |

|

SU444244A1 |

| Накопитель для полупроводникового запоминающего устройства | 1980 |

|

SU955202A1 |

Авторы

Даты

1979-02-05—Публикация

1975-03-06—Подача