Изобретение относится к вычислительной технике и может быть использовано в электрически перепрограммируемом запоминающем устройстве на запоминающих МНОП-транзисторах, сохраняющих информацию при отключении источника питания.

Цель изобретения - повышение надежности работы матричного накопителя путем исключения замыканий, пробоя диэлектрика, паразитных конденсаторов между адресными шинами второй и первой групп, увеличения пороговых напряжений паразитных транзисторов.

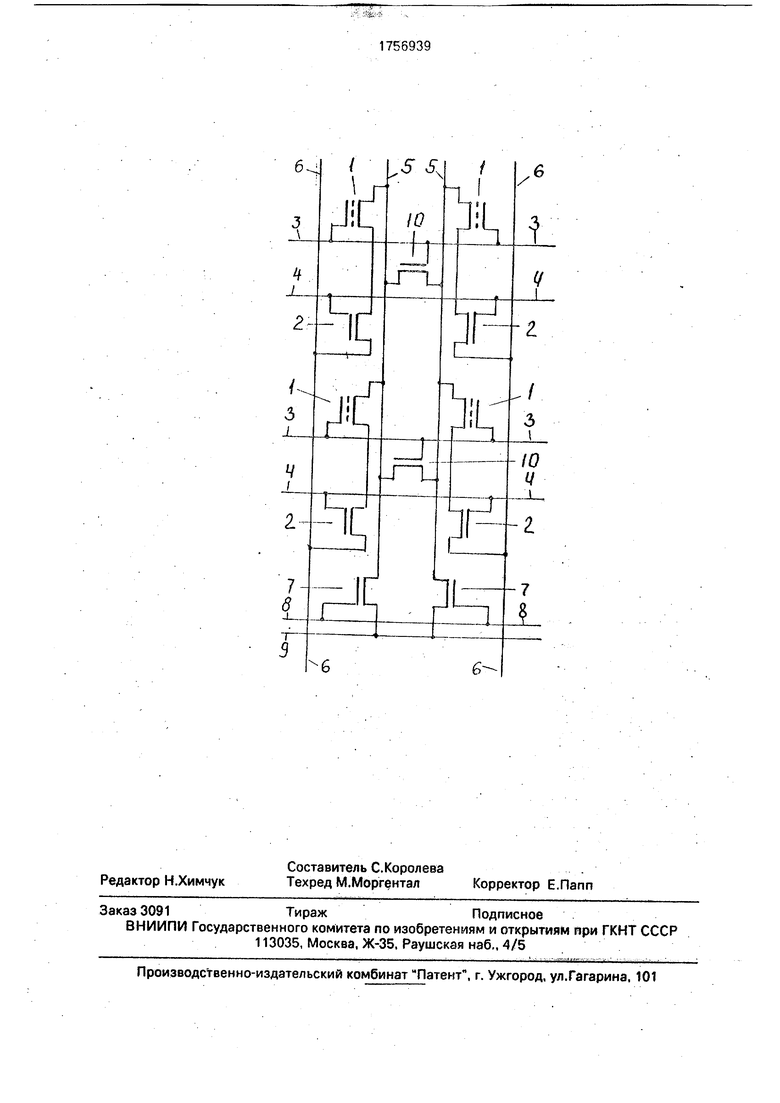

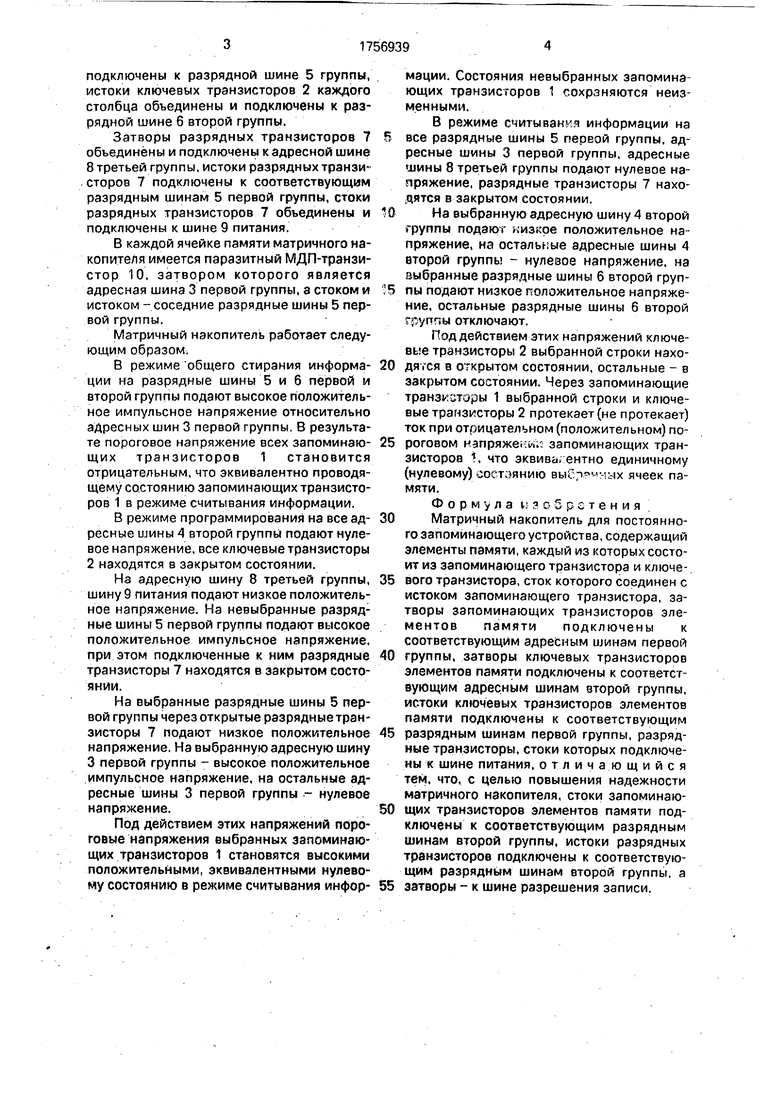

На чертэже приведена эквивалентная электрическая схема фрагмента матричного накопителя и указанием в качестве примера паразитных МДП-транзисторов между соседними разрядными шинами первой группы.

Матричный накопитель содержит запоминающий транзистор 1 ячейки памяти,

ключевой транзистор 2 этой ячейки, первую и вторую группы адресных шин 3,4, первую и вторую группы разрядных шин 5 и 6, разрядный транзистор 7, адресную шину 8 третьей группы , шину 9 питания , паразитный МДП-транзистор 10. В перекрестиях групп адресных и разрядных шин расположены ячейки памяти.

Каждая из ячеек памяти состоит из запоминающего транзистора 1 и ключевого транзистора 2, причем исток запоминающего транзистора 1 соединен со стоком ключевого транзистора 2.

Затворы запоминающих транзисторов 1 ячеек памяти каждой строки накопителя объединены и подключены к адресной шине 3 первой группы. Затворы ключевых транзисторов 2 каждой строки объединены и подключены к адресной шине 4 второй группы. Строки запоминающих транзисторов 1 ячеек памяти каждого столбца объединены и

СП

о

ю

(л)

подключены к разрядной шине 5 группы, истоки ключевых транзисторов 2 каждого столбца объединены и подключены к разрядной шине б второй группы.

Затворы разрядных транзисторов 7 объединены и подключены к адресной шине 8 третьей группы, истоки разрядных транзисторов 7 подключены к соответствующим разрядным шинам 5 первой группы, стоки разрядных транзисторов 7 объединены и подключены к шине 9 питания.

В каждой ячейке памяти матричного накопителя имеется паразитный МДП-транзи- стор 10, затвором которого является адресная шина 3 первой группы, а стоком и истоком - соседние разрядные шины 5 первой группы.

Матричный накопитель работает следующим образом.

В режиме общего стирания информации на разрядные шины 5 и 6 первой и второй группы подают высокое положительное импульсное напряжение относительно адресных шин 3 первой группы. В результате пороговое напряжение всех запоминающих транзисторов 1 становится отрицательным, что эквивалентно проводящему состоянию запоминающих транзисторов 1 в режиме считывания информации.

В режиме программирования на все адресные шины 4 второй группы подают нулевое напряжение, все ключевые транзисторы

2находятся в закрытом состоянии.

На адресную шину 8 третьей группы, шину 9 питания подают низкое положительное напряжение. На невыбранные разрядные шины 5 первой группы подают высокое положительное импульсное напряжение, при этом подключенные к ним разрядные транзисторы 7 находятся в закрытом состоянии.

На выбранные разрядные шины 5 первой группы через открытые разрядные транзисторы 7 подают низкое положительное напряжение. На выбранную адресную шину

3первой группы - высокое положительное импульсное напряжение, на остальные адресные шины 3 первой группы - нулевое напряжение.

Под действием этих напряжений пороговые напряжения выбранных запоминающих транзисторов 1 становятся высокими положительными, эквивалентными нулевому состоянию в режиме считывания информации. Состояния невыбранных запоминающих транзисторов 1 сохраняются неизменными.

В режиме считывания информации на

все разрядные шины 5 первой группы, адресные шины 3 первой группы, адресные шины 8 третьей группы подают нулевое напряжение, разрядные транзисторы 7 находятся в закрытом состоянии.

На выбранную адресную шину 4 второй группы подают низкое положительное напряжение, на остальные адресные шины 4 второй группы - нулевое напряжение, на выбранные разрядные шины 6 второй группы подают низкое положительное напряжение, остальные разрядные шины 6 второй группы отключают.

Под действием этих напряжений ключевые транзисторы 2 выбранной строки находятся в открытом состоянии, остальные - в закрытом состоянии. Через запоминающие транзкгторы 1 выбранной строки и ключевые транзисторы 2 протекает (не протекает) ток при отрицательном (положительном) пороговом иэпряже :. запоминающих транзисторов , что эквивалентно единичному (нулевому) состоянию выСр°«чах ячеек памяти.

Формула изобретения

Матричный накопитель для постоянного запоминающего устройства, содержащий элементы памяти, каждый из которых состоит из запоминающего транзистора и ключевого транзистора, сток которого соединен с истоком запоминающего транзистора, затворы запоминающих транзисторов элементов памяти подключены к соответствующим адресным шинам первой

группы, затворы ключевых транзисторов элементов памяти подключены к соответствующим адресным шинам второй группы, истоки ключевых транзисторов элементов памяти подключены к соответствующим

разрядным шинам первой группы, разрядные транзисторы, стоки которых подключены к шине питания, отличающийся тем, что, с целью повышения надежности матричного накопителя, стоки запоминающих транзисторов элементов памяти подключены к соответствующим разрядным шинам второй группы, истоки разрядных транзисторов подключены к соответствующим разрядным шинам второй группы, а

затворы - к шине разрешения записи.

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричный накопитель | 1980 |

|

SU974412A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| МАТРИЧНЫЙ НАКОПИТЕЛЬ НА МДП-ТРАНЗИСТОРАХ С ИЗМЕНЯЕМЫМ ПОРОГОВЫМ ВКЛЮЧЕНИЕМ | 1985 |

|

RU1378681C |

| Матричный накопитель для постоянного запоминающего устройства | 1988 |

|

SU1531169A1 |

| МАТРИЧНЫЙ НАКОПИТЕЛЬ ДЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1981 |

|

SU1025259A1 |

| Матричный накопитель | 1981 |

|

SU1015440A1 |

| Способ записи и считывания информации в МНОП-элементе памяти и матричный накопитель для запоминающего устройства | 1983 |

|

SU1405089A1 |

| Устройство для считывания информации из матричного накопителя | 1978 |

|

SU767834A1 |

| Оперативное запоминающее устройство | 1987 |

|

SU1429167A1 |

| Матричный накопитель для постоянного запоминающего устройства | 1988 |

|

SU1778790A1 |

Изобретение относится к вычислительной технике и может быть использовано в электрически перепрограммируемом посто- янном запоминающем устройстве на МНОП- транзисторах, Целью изобретения является повышение надежности матричного накопителя. Поставленная цель достигается за счет того, что стоки запоминающих транзисторов элементов памяти подключены к соответствующим разрядным шинам аторой группы, истоки разрядных транзисторов подключены к соответствующим разрядным шинам второй группы, а затворы - к шине разрешения записи. 1 ил.

| Матричный накопитель | 1981 |

|

SU1015440A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Авторское свидетельство СССР № 483036, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1992-08-23—Публикация

1990-06-04—Подача