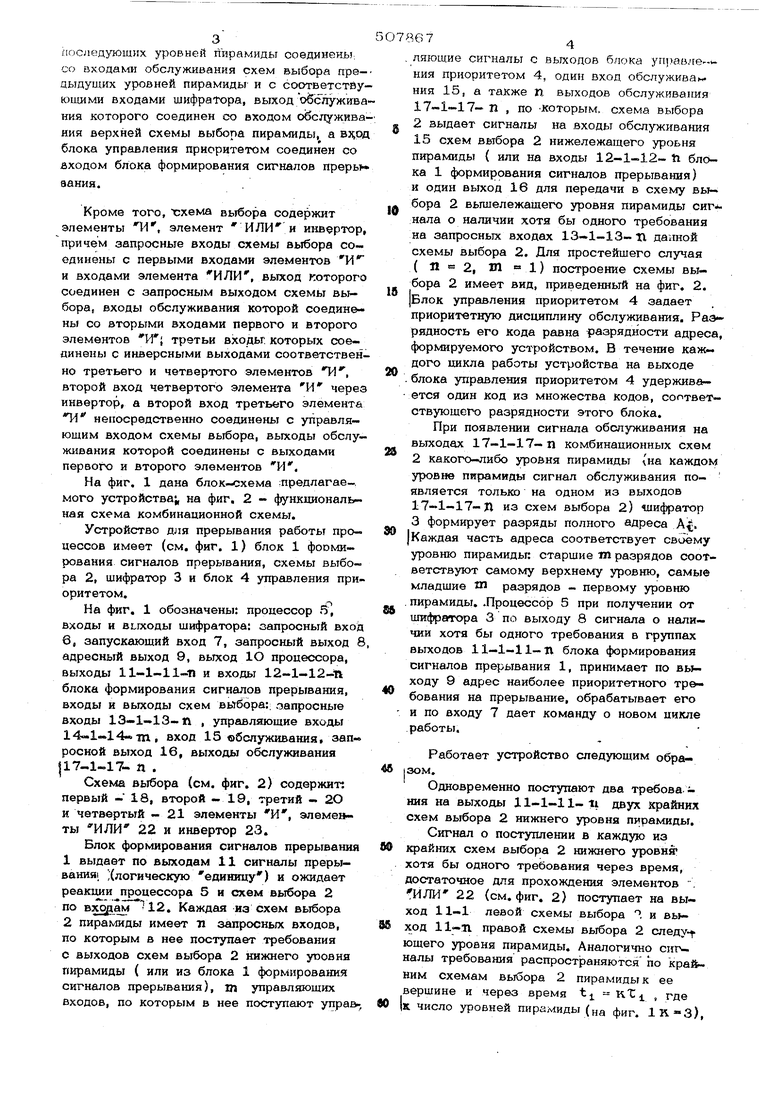

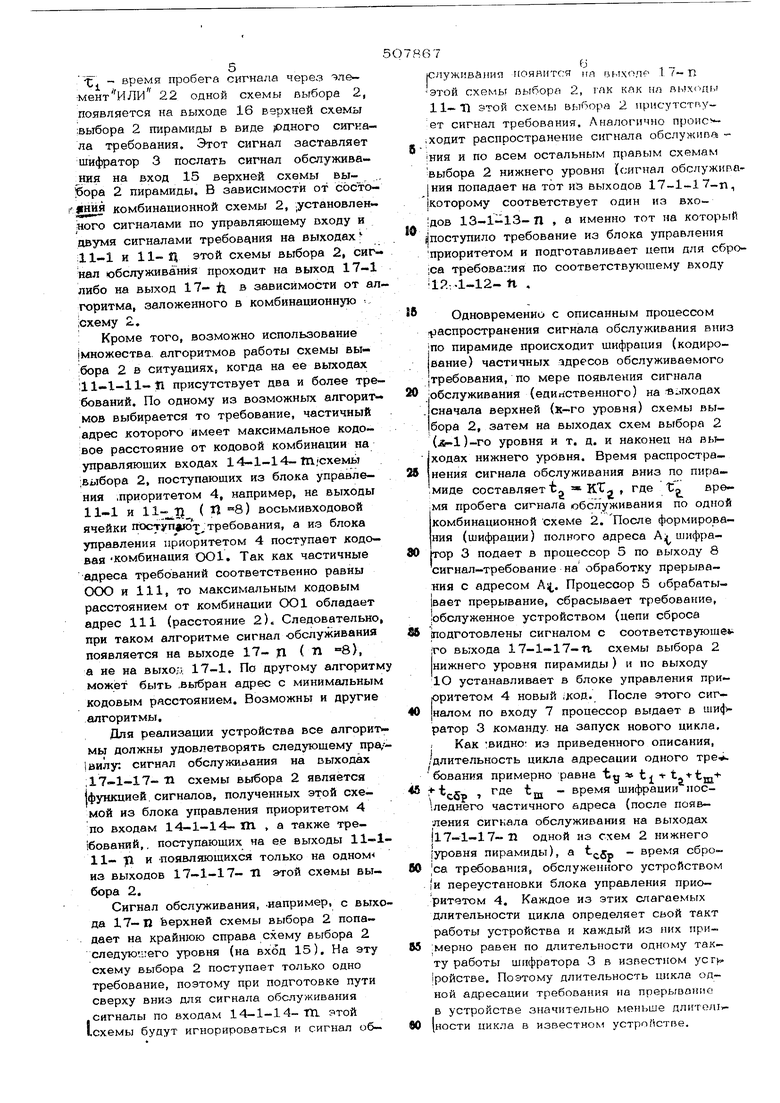

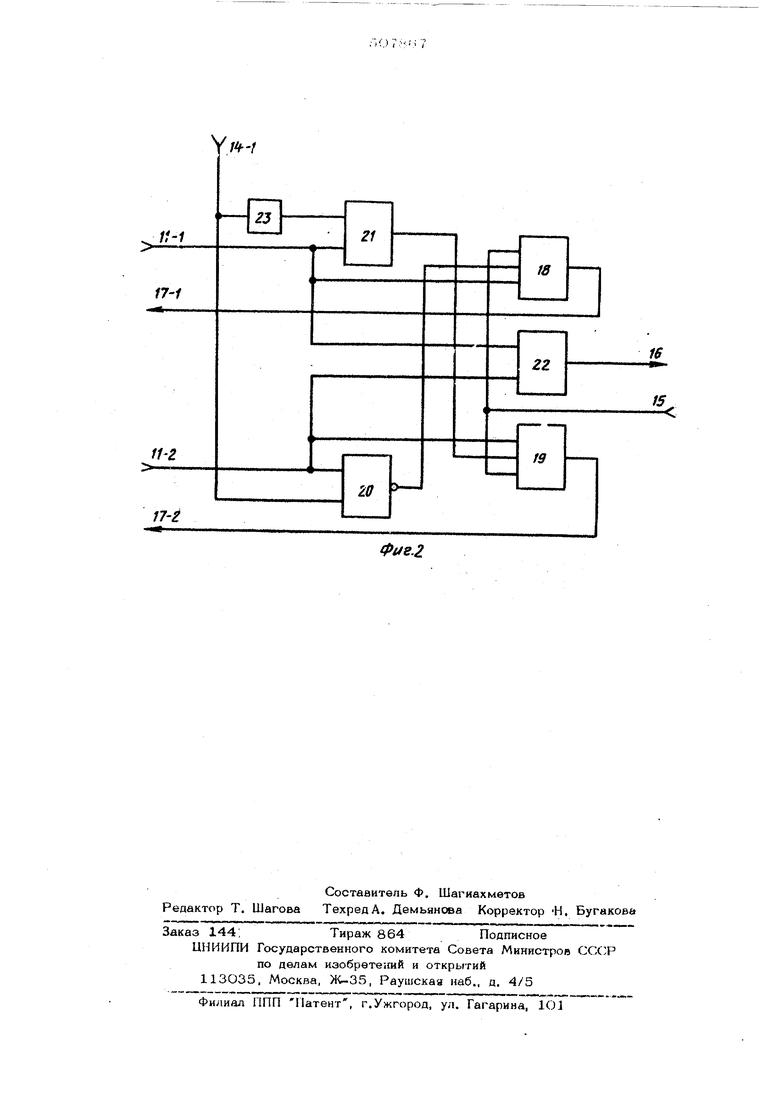

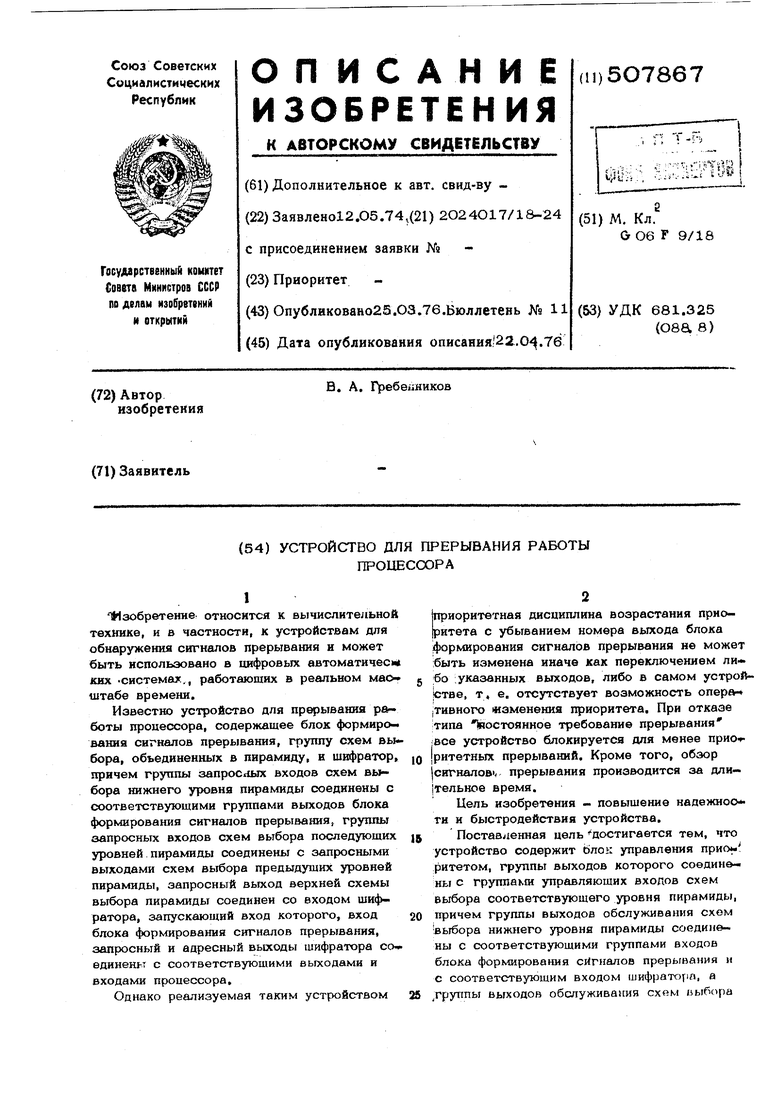

(54) УСТРОЙСТВО ДЛЯ ПРЕРЫВАНИЯ РАБОТЫ ПРОЦЕССОРА последующих уровней пирамиды соединень. со входак обслуживания схем выбора пре- аыдущих уровней пирамиды и с соответству ющими входами шифратора, выходоёслужиБа ния которого соединен со входом оёслужива ния верхней схемы выбора пирамиды, а ъх,о блока управления приоритетом соединен со входом блока формирования сигналов преры вания. Кроме того, тзхема выбора содержит элементы И, элемент ИЛИ и инвертор причем запросные входы схемы выбора соединены с первыми входами элементов И и входами элемента ИЛИ, выход которог соединен с запросным выходом схемы выбора, входы обслуживания которой соединены со вторыми входами первого и второго элементов И} третьи входы: которых сое йинены с инверсными выходами соответствен но третьего и четвертого элементов И, второй вход четвертого элемента И чере инвертор, а второй вход третьего элемента Т1 непосредственно соединены с управляющим входом схемы выбора, выходы обслу живания которой соединены с выходами первого и второго элементов И. На фиг. 1 дана блок-схема ;предлагае-, мого устройства;, на фиг. 2 - функционал на я схема комбинационной схемы. Устройство для прерывания работы процессов имеет (см. фиг. 1) блок 1 фооми рования сигналов прерывания, схемы выбора 2, шифратор 3 и блок 4 управления при оритетом. На фиг. 1 обозначены: процессор 5, входы и вьгходы шифратора; запросный вход в, запускающий вход 7, запросный выход 8 адресный выход 9, выход Ю процессора, выходы 11-l-ll-T и входы 12-1-12-tl блока формирования сигналов прерывания, входы и выходы схем выбора:: запросные входы 13-1-13-п , управляющие входы 14-.1 14«7П, вход 15 обслуживания запросной выход 16, выходы обслуживания |17-1-17- п . Схема выбора (см. фиг. 2) содержит: первый - 18, второй - 19, третий - 2О и четвертый - 21 элементы И, элементы ИЛИ 22 и инвертор 23. Блок формирования сигналов прерывания 1выдает по выходам 11 сигналы прерывания (логическую единицу) и ожидает реакгши процессора 5 и схем выбора 2 по вхоракГ 12. Каждая из схем выбора 2пирамиды имеет п запросньк входов, по которым в нее поступает требования с выходов схем выбора 2 нижнего уоовня пирамиды ( или из блока 1 формирования сигналов прерывания), щ управляющих Входов, по которым в нее поступают управ 67 лягощие сигналы с выходов блока ynjiaBjre ния приоритетом 4, один вход обслуживай. ния 15, а также п выходов обслуживания п , по Которым, схема выбора 2 выдает сигналы на входы обслуживания 15 схем ввтбора 2 нижележащего уроьня пирамиды { или на входы 12-1-12- ti блока 1 формирования сигналов прерывания) и один выход 16 для передачи в схему вы- бора 2 вышележащего уровня пирамиды сиг нала о наличии хотя бы одного требования на запросных входах 13-1-13- ц данной схемы выбора 2. Для простейшего случая ( П 2, Ш 1) построение схемы выбора 2 имеет вид, приведенный на фиг. 2. |БЛОК управления приоритетом 4 задает приоритетную дисциплину обслуживания. Разрядность его кода равна разрядности адреса, формируемого устройством. В течение каж дого цикла работы устройства на выходе блока управления приоритетом 4 удерживается один код из множества кодов, соптветствующего разрядности этого блока. При появлении сигнала обслуживания на выходах 17-1-17-п комбинационных схем 2какого-либо уровня пирамиды (на каждом уровне пирамиды сигнал обслуживания появляется только на одном из выходов 17-1-17-П из схем выбора 2) шифратор 3формирует разряды полного адреса Aij;. I Каждая часть адреса соответствует своему уровню пирамидьк старшие Ш разрядов соответствуют самому верхнему уровню, самые младшие ОТ разрядов - первому уровню пирамиды, .Процессор 5 при получении от шифратора 3 по выходу 8 сигнала о наличии хотя бы одного требования в группах выходов 11-1-11- п блока формирования сигналов прерывания 1, принимает по выходу 9 адрес наиболее приоритетного требования на прерывание, обрабатывает его и по входу 7 дает команду о новом цикле .работы. Работает устройство следующим обраЗОМ, Одновременно поступают два требования на выходы 11-1-11- 11 двух крайних схем выбора 2 нижнего уровня пирамиды. Сигнал о поступлении в каждую из крайних схем выбора 2 нижнего уровня хотя бы одного требования через время, достаточное для прохождения элементов . ИЛИ 22 (см. фиг. 2) поступает на выход 11-1 левой схемы выбора . и выход 11-И правой схемы выбора 2 следу-t щего уровня пирамиды. Аналогично сигалы требования распространяются по крайим схемам выбора 2 пирамиды к ее вершине и через время tj - кТ. , где к число уровней пирамиды („а фиг. 1К.3), t;. - время пробега сигнала через ле- 22 одной схемы выбора 2, появляется на выходе 16 верхней схемы выбора 2 пирамиды в виде одного сигна ла требования. Этот сигнал заставляет шифратор 3 послать сигнал обслужива ния на вход 15 верхней схемы выбора 2 пирамиды, В зависимости от состо комбинационной схемы 2, ;установлен него сигналами по управляющему входу и двумя сигналами требования на выходах 11-1 и 11- Ц этой схемы выбора 2, сиг нал обслужива ния проходит на выход 17-1 либо на выход 17- и в зависимости от а горитма, заложенного в комбинационную |охему 2. Кроме того, возможно использование |множества, алгоритмов работы схемы вы:бора 2 в ситуациях, когда на ее выходах :11-1-11-11 присутствует два и более тре бований. По одному из возможных алгорит мов выбирается то требование, частичный адрес которого имеет максимальное кодовое расстояние от кодовой комбинации на управляющих входах 14-1-14-Ш;схемы ;выбора 2, поступающих из блока управления .приоритетом 4, например, не выходы 11-1 и 11- 11 ( п °8) восьмивходовой ячейки поступают, требования, а из блока управления приоритетом 4 поступает кодовая -комбинация ОО1, Так как частичные адреса требований соответственно равны ООО и 111, то максимальным кодовым расстоянием от комбинации ОО1 обладает адрес 111 (расстояние 2). Следовательно при таком алгоритме сигнал обслуживания появляется на выходе 17- д ( Т1 8), а не на выход 17-1. По другому алгоритм может быть .выбран адрес с минимальным кодовым расстоянием. Возможны и другие алгоритмы. Для реализации устройства все алгорит мы должны удовлетворять следующему пра аилу: сигнал обслуживания на выходах ; 17-1-17- TQ схемы выбора 2 является |фушсцией сигналов, полученных этой схемой из блока управления приоритетом 4 по входам 14-1-14- Ш , а также требований,. поступающих на ее выходы 11-1 11- р и -появляющихся только на одном из выходов 17-1-17- И этой схемы выбора 2. Сигнал обслуживания, -например, с выхо да 17-11 Ьерхней схемы выбора 2 попа- дает на крайнюю справа схему выбора 2 следую .иего уровня (на вход 15). На эту схему выбора 2 поступает только одно требование, поэтому при подготовке пути сверху вниз для сигнала обслуживания .сигналы по входам 14-1-14-ТП этой 1схемы будут игнорироваться и сигнал об- (служива)1ип появится ня вмхол 1 (-п ЭТОЙ схемы выбора 2, гпк как нп 11- 11 этой схемы выбора 2 присутствует сигнал требования. Лналогнчно проис ;ходит распространение сигнала обслужила - 1ния и по всем остальным правым схемам выбора 2 нижнего уровня (сигнал обслужпва|ния попадает на тот иэ выходов 17-1-1 V-n, которому соответствует один из вхо;дов 13-1-13- п , а именно тот на который ||поступило требование из блока управления приоритетом и подготавливает цепи для сброica требования по соответствующему входу 12:-1-12- ft , Одновременно с описанным процессом распространения сигнала обслуживания вниз :по пирамиде происходит шифрация (кодирование) частичных адресов обслуживаемого требования, по мере появления сигнала -обслуживания (единственного) на гв;,1ходах сначала верхней (к-го уровня) схемы вы|бора 2, затем на выходах схем выбора 2 (-1)-го уровня и т. д. и наконец на выходах нижнего уровня. Время распространения сигнала обслуживания вниз по пирамиде составляет t « KTj, , где t время пробега сигнала обслуживания по одной комбинационной схеме 2. После формирования (шифрации) полного адреса А; шифратор 3 подает в процессор 5 по выкоау & сигнал-требование на обработку прерывания с адресом А. Процессор 5 обрабаты|вает прерывание, сбрасывает требование, обслуженное устройством (цепи сброса (подготовлены сигналом с соответствующе (ГО выхода 17-1-17-п схемы выбора 2 нижнего уровня пирамиды ) и по выходу 1О устанавливает в блоке управления приоритетом 4 новый ,код. После этого сиг|налом по входу 7 процессор выдает в ши(| ратор 3 команду, на запуск нового цикла, ; Как :видно- из приведенного описания, /длительность цикла адресации одного тре бования примерно равна tg сбр ш вр шифрации пос леднего частичного адреса (после появления сигнала обслуживания на выходах il7-l-17-tl одной из схем 2 нижнего уровня пирамиды), а t,- - время сбро|са требования, обслуженного устройством и переустановки блока управления приоритетом 4. Каждое из этих слагаемых длительности цикла определяет свой такт работы устройства и каждый из них при:мерно равен по длительности одному такту работы шифратора 3 в известном уст ройстве. Поэтому длительность цикла одной адресации требования на прерывонпй в устройстве значительно меньше длите/П нести цикла в известном устроГютве. Следует заметить, что в устройстве бло управления -приоритетом 4 может; представлять собой и простой регистр с числом раз рядов Лр « TQfi , и счетчик, и генератор слу чайных чисел.В первом случае при реализа ции алгоритма выборки требования с адрео сом, имеющим минимальное кодовое рассто яние от управляющего кода (ш разрядов i, запись в регистр кода ОО.,,О опрёйбляе последовательность приоритетов, убывающих с возрастанием номера запроса на прерывание. Запись в регистр кода 11... 1 изменяет порядок следования приоритетов на об ратныйд Запись какого-либо произвольного кода в регистр сделает эапрос| таким произ вольным адресом наиболее приоритетным. На отмеченном; свойстве управляемости пирамидальной схемы кодом, подаваемым с выходов блока управления приоритетом 4, и построено управление приоритетной дисциплиной в устройстве. Целая гамма приоритетных дисциплин может быть получена в устройстве при использовании в качестве блока управления приоритетом 4 генераторов случайных чисел с различными видами распределений (равномерным, линейным,: экспоненцяйльным и т. д J. Равномерное распределение приоритетов получается в устройстве при использовании двоичного счетчика в качестве блока управления приоритетом 4. Возможны также и раз личные варианты исполнения других блоков устройства (например, не все схемы выбора 2 могут быть одинаковыми, шифратор 3 может представлять собой как комбинацоонную, так и регистровую схему). Формула изобретения 1. Устройство для прерывания работы проиес дзра, содержащее блок формирования сигналов прерывания , группу схем выбора, объединенных в пирамиду, шифра1ч р, причем группы запросных входов схем выбора нижнего уровня пирамиды соединены с соответствующими группами выходов блока формирования сигналов прерывания, группы запросных входов схем выбора последующих уровней пирамиды соединены 67 с запросными выходами схем выбора предыдущих; уровней пирамиды,. запросный выход верхней схемы выбора пирагл1дыОоединен со входом шифратора, запускающий вход которого, вход блока формирования сигналов прерывания, запросный и адресный выходы шифратора соединены с соответствующимивыходами и входами процессора, отличающееся тем, что, с целью повыщения надежности и быстродействия устройства, оно содержит блок управления приоритетом, группы выхо- дов которого соединены с группами управляющих входов схем выбора с6ответствук щего уровня пирамиды, причем группы выходов обслуживания схем выбора нижнего уровА ня пирамиды соединены с соответствующими группами входов блока формирования сигналов прерывания и с соответствующим входом шифратора, а группы выходов обслужй вания схем выбора последующих уровней пирамиды соединены со входами обе;./живания схем выбора предыдущих уровней пирамиды и с соответствующими входами щифратора, выход обслуживания которого соединен со входом обслуживания верхней схемы выбора пирамиды, а вход блока управления приоритетом соединен со входом блока формирования сигналов прерывания. 2. Устройство по п. 1, отличающееся тем, что схема выбора содер-. жит алементы И, элемент ИЛИ и инвертор, причем запросные входы схемы выбора соединены с первыми входами элемен- -тов И и входами элемента ИЛИ, выход которого соединен с запросным выходом схемы выбора, входы обслуживания которой с единены со вторыми входами первого и второго элементов И, третьи входы которых соединены с инверсными выходами соот ветственно третьего и четвертого элементов И, второй вход четвертого элемента И через инвертор, а второй вход третьего элемента И непосредственно соединевы с управляющим входом; схемы выбора, выходы обслуживания которой соединены с выходами первого и второго элементов И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство переменного приоритета | 1986 |

|

SU1383353A1 |

| Отказоустойчивая вычислительная система | 1990 |

|

SU1798800A1 |

| УСТРОЙСТВО ПЕРЕМЕННОГО ПРИОРИТЕТА | 1993 |

|

RU2087939C1 |

| Устройство приоритетного прерывания | 1990 |

|

SU1793440A1 |

| УСТРОЙСТВО ПЕРЕМЕННОГО ПРИОРИТЕТА | 1999 |

|

RU2152072C1 |

| Устройство для прерывания программ | 1980 |

|

SU970370A1 |

| Многоуровневая подсистема обработки прерываний | 1988 |

|

SU1624448A1 |

| Устройство для обмена информацией между цифровой вычислительной машиной и внешними устройствами | 1981 |

|

SU1003066A1 |

| Устройство для обслуживания запросов | 1988 |

|

SU1550517A1 |

| Устройство сопряжения процессора с внешними устройствами | 1987 |

|

SU1509893A1 |

Авторы

Даты

1976-03-25—Публикация

1974-05-12—Подача