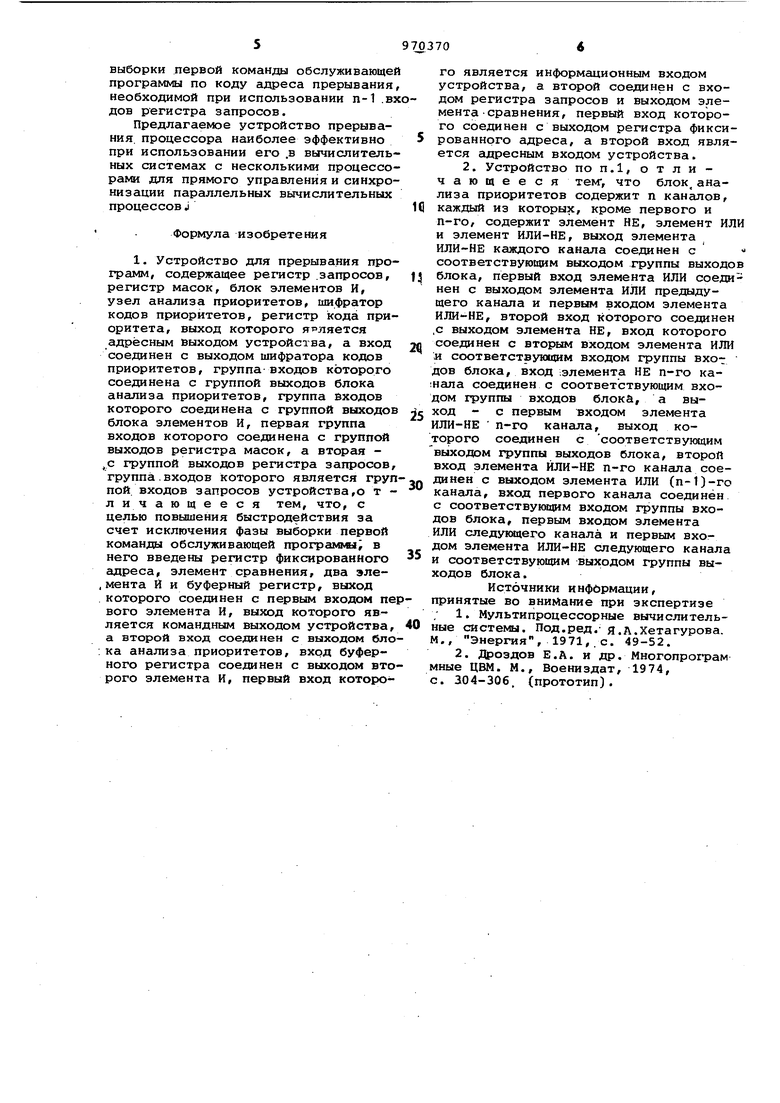

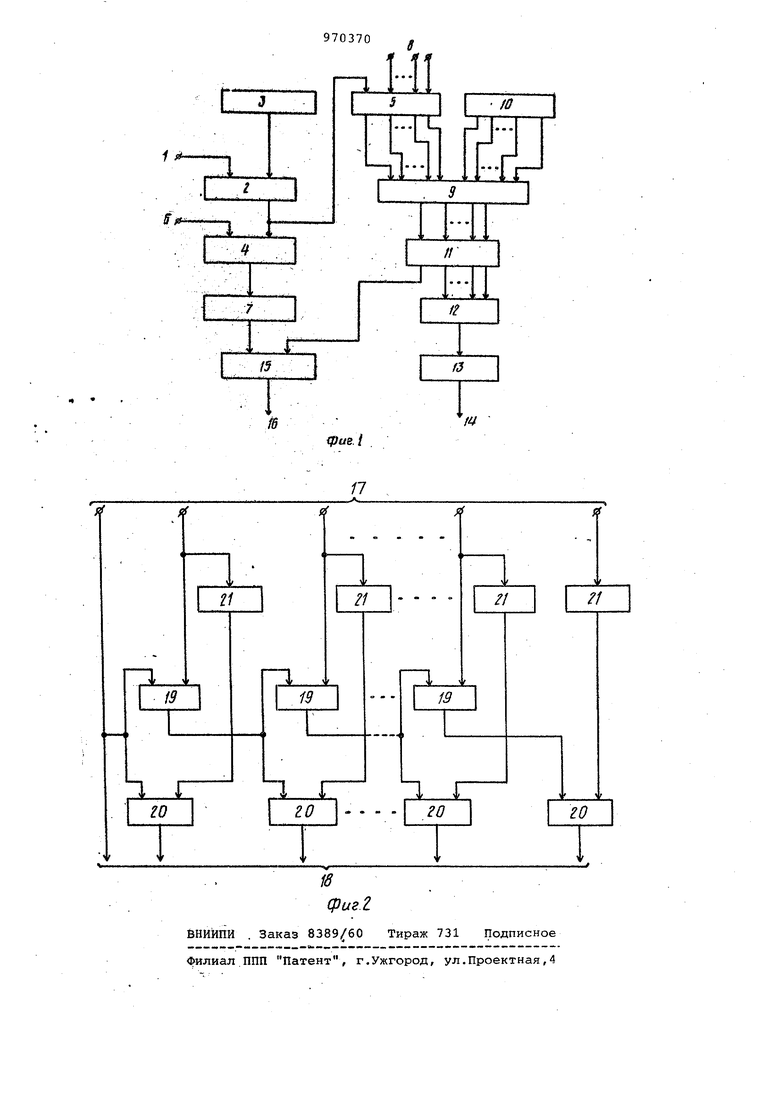

Изобретение относится к вычислительной технике и может быть использовано в вычислительных машинах и системах. Известно устройство прерывания, процессора, содержащее регистр запросов прерывания, схему разретиения прерывания, шифратор кода команды и блок .элементов И 1 1. Недостатки указанного устройства низкое быстродействие из-за программной организации анешиза причины прерывания и выхода на обслуживаихцую про грамму, а также ограниченное количест во программ, на которые можнопередат управление по сигналу прерывания. Наиболее близким по технической сущности к предлагаемому является устройство прерывания процессора, содержащее регистр запросов, регистр маски прерываний, блок элементов И, схему ансшиза приоритета запросов, шифратор кода прерываний, регистр кода прерываний,выход которого соединен с адресным выходом устройства,а вход с выходе шифратора кода прерывания, соединенного по входам с выходами схемы анализа приоритетов запросов, входы которой соединены с выходами блока элементов И, соединенного по первым входам с выходами регистра маски прерываний, а по вторым - с выходами регистра запросов, входы которюго соединены с входом кода за- .просов i устройства 12. Недостатками известного устройства являются отсутствие возможности выполнения любой программы или команды по сигналу запроса прерывания, а также дополнительные затраты времени на выборку первой команды программы обагхуживания запроса Указанный недостаток устрсй1ства особенно проявляется при использовании в многомашинш:1х вычислительных системах при решении задачи обеспечения гибкого прямого управления процессорами. Цель изобретения - повыщение быстродействия устройства за счет исключения фазы выборки первой команды обслуживающей программа. Поставленная цель достигается тем, что -в устройство для прерывания программ, содержащее регистр запросов, регистр масок, блок элементов И, узел анализа приоритетов, шифратор кодов приоритетов, регистр кода приоритета, выход которого является адресным выходом устройства, а вход соединен с выходом шифратора кодов приоритетов, группа входов которого соединена с группой выходов блока анализа приоритетов, группа входов которого соединена с группой выходов блока элементов И, первая группа вхо дов которого соединена с группой выходов регистра масок, а вторая - с группой выходов регистра запросов, группа входов которого является груп пой входов запросов устройства, введ ны регистр фиксированного адреса, элемент сравнения, два элемента И и буферный регистр, выход которого сое динен с первым входом первого влемен т.а И, выход которого является команд ным выходом устройства, а второй вхо соединен с выходом блока анализа при оритетов,вход буферного регистра сое.динен с выходом второго элемента И, первый вход которого является информационным устройства, а второй соединен с входом регистра запросов и выходом элемента сравнения, первый вход которого соединен с выходом регистра фиксированного адреса, а второй вход является адресным входом устройства.. Блок анализа приоритетов содержит п каналов, каждый из которых, кроме первого и п-го содержит эле-, мент НЕ, элемент ИЛИ и элемент ИЛИ-Н выход элемента ИЛИ-НЕ каждого канала соединен с соответствующим выходом группы выходов блока, первый вход элемента ИЛИ соединен с выходом элемента ИЛИ предыдущего канала и первым входом элемента ИЛИ-НЕ, ззторой вход которого соединен с выходом эле мента НЕ, вход которого соединен с вторым входом элемента ИЛИ и соответ ствующим входом группы входов блока, вход элемента НЕ п-го канала соединен с соответствующим входом группы входов блока,а выход - с первым.вхо дом элемента ЙЛИ-НЕ п-го кангша, выход которого соединен с соответствую щим выходом группы выходов блока, второй вход элемента ИЛИ-НЕ п-го канала соединен с выходом элембгнта ИЛИ (п-1)-го канала, вход первого канала соединен с соответствукидим входом группы входов блока, первым ,входом элемента ИЛИ следующего канала и перйым входом элемента ИЛИ-НЕ следующего канала и соответствующим выходом группы выходов блока. На фиг. 1 представлена структурн4я электрическая схема устройства д|я прерывания nporpaMMf на фиг.2 структурная схема блока анализа прио ритетов. Устройство содержит адресный вход 1, элемент 2 сравнения, регистр 3 фиксированного адреса, элемент И 4, регистр 5 запросов, информационный вход 6, буферный регистр7, группу запросных входов 8, блок элементов И 9, регистр 10 масок, блок 11 анализа приоритетов, шифратор 12 кодов приоритетов, регистр 13 кода приоритета, адресный выход 14, элемент И 15, командный выход 16. Блок анализа приоритетов содержит группу из п входов 17, группу из п выходов 18, п-2 элементов ИЛИ 19, п-1 элементов ИЛИ-НЕ 20, п-1 элементов НЕ 21. Устройство работает следующим образом. На адресный вход 1 устройства поступает код адреса ЗУ и сравнивается элементов 2 сравнения с содержимым регистра 3 фиксированного адреса, которое эквивалентно адресу фиксированной ячейки ЗУ и записывается лиВо аппаратурными, либо программными средствами процессора. В случае совпадения кодов вырабатывается сигнал, который поступает на управляющий вход элемента И 4 и одновременно на п-й вход регистра 5 запросов. По этому сигналу информация с информационного входа б устройства записывается в буферный регистр 7. На п-1 входов регистра запросов поступают сигналы запросов прерываний с группы входов 8 запросов устройства. Сигналы запросов с регистра запросов поступают на вторые входы блока элементов И 9, который в соответствии с кодом маски , поступающим на первые входы блока элементов И с регистра 10 маски, выделяет незамаскированные запросы и : передает их на входы блока-11 анализа приоритетов, который на основании заданной дисциплины обслуживания выделяет запрос с максимальным приоритетом и разрешает его обслуживание. Если максимальный приоритет имеет рдин из п-1 запросов, то п-1 разряд|ный унитарный код поступает на шифратор 12, который .Формирует относительный либо абсолютный адрес первой команды программы обслуживания данного запроса прерывания, поступающий через регистр 13 кода приоритета на выход 14 адресов команд устройства ..В случае максимального приоритета у п-го запроса сигнгш с п-го выхода схемы анализа приоритетов запросов поступает на управляющий вход элемента И 15 и разрешает передачу содержимого буферного регистра на командный выход 16 устройства. Таким образом, предлагаемое устройство прерывания процессора позволяет процессору воспринимать информацию с информационного входа устройства как первую команду обслуживающей программы, тем самым обеспечивая расширение функциональных возможностей устройства за счет практически неограниченного косвенного увеличения уровней прерывания и увеличение быстродействия за счет исключения фазы

выборки первой команды обслуживающей программы по коду адреса прерывания, необходимой при использовании п-1.входов регистра запросов.

Предлагаемое устройство прерывания, процессора наиболее эффективно 5 при использовании его .в вычислительных системах с несколькими процессорами для прямого управления и синхронизации параллельных вычислительных процессов Id

Формула изобретения

1, Устройство для прерывания программ, содержащее регистр .запросов, fj регистр масок, блок элементов И, узел анализа приоритетов, шифратор кодов приоритетов, регистр кода приоритета, выход которого является адресным выходом устройства, а вход 2fl соединен с выходом шифратора кодов приоритетов, группа-входов которого соединена с группой выходов блока анализа приоритетов, группа Входов которого соединена с группой выходов с блока элементов И, первая группа входов которого соединена с группой выходов регистра масок, а вторая с группой выходов регистра запросов, группа.входов которого является груп- пой входов запросов устройства,о т ичающееся тем, что, с целью повышения быстродействия за счет исключения фазы выборки первой команды обслуживающей программы в него введены регистр фиксированного 5 адреса, элемент сравнения, два элемента И и буферный регистр, выход которого соединен с первым входом первого элемента И, выход которого является командным выходом устройства, 40 а второй вход соединен с выходом блока анализа приоритетов, вхрд буферного регистра соединен с выходом второго элемента И, первый вход которого является информационным входом устройства, а второй соединен с входом регистра запросов и выходом элемента сравнения, первый вход которого соединен с выходом регистра фиксированного адреса, а второй вход является ащресным входом устройства.

2. Устройство по п.1, отличающееся тем-, что блок, анализа приоритетов содержит п каналов, каждый из которых, кроме первого и п-го, содержит элемент НЕ, элемент ИЛ и элемент ИЛИ-НЕ, выход элемента ИЛИ-НЕ каждого канала соединен с соответствующим выходом группы выходо блока, первый вход элемента ИЛИ соединен с выходом элемента ИЛИ предыдущего канала и первым входом элемента ИЛИ-НЕ, второй вход которого соединен .с выходом элемента НЕ, вход которого соединен с вторым входом элемента ИЛИ и соответствующим входом группы входов блока, вход ;злемента НЕ п-го соединен с соответствующим входом группы входов блока, а выход - с первым входом элемента ИЛИ-НЕ п-го канала, выход которого соединен с соответствующим выходом группы выходов блока, второй вход элемента ЙЛИ-НЕ п-го канала соединен с выходом элемента ИЛИ (п-1)-го канала, вход первого канала соединён с соответствукмцим входом группы входов блока, первым входом элемента ИЛИ следукядего канала и первым входом элемента ИЛИ-НЕ следующего канала и соответствующим выходом группы выходов блока.

Источники инфбрмации, принятые во внимание при экспертизе

1.Мультипроцессорные вычислительные системы. Под.ред.- я.Л.Хетагурова. М., Энергия, 1971,.с. 49-52.

2.Дроздов Е.А. и др. Многопрограм мные ЦВМ. М., Воениздат, 1974,

с. 304-306. (прототип).

tB

(pus. i

ш

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена информацией | 1982 |

|

SU1048468A1 |

| Устройство для прерывания программ | 1978 |

|

SU736101A1 |

| Селекторный канал | 1983 |

|

SU1226477A1 |

| Многоканальное устройство дляпРЕРыВАНия пРОгРАММ | 1979 |

|

SU811257A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Устройство для сопряжения процессора с внешними устройствами | 1990 |

|

SU1839253A1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Устройство для сопряжения | 1977 |

|

SU648974A1 |

| Устройство для управления вводом-выводом | 1989 |

|

SU1735859A1 |

| Устройство для обмена информацией между цифровой вычислительной машиной и внешними устройствами | 1981 |

|

SU1003066A1 |

1

19

19

m

Авторы

Даты

1982-10-30—Публикация

1980-07-08—Подача